这一章是续第一章实验和第二章实验,我们建立一个名为“SMG Controlelr”的TOP模块,用于连接“SPI 控制器” 和 “SPI发送模块”。

示意图如下:

注意点:

为什么我命名为“1位SMG控制器”呢?其实我的设计构思时这样的-这个“1位SMG控制器”要完成的工作仅是“点亮一个数码管在某一个位”而已。

除此之外,这个“1位SMG控制器”,是没必要输入“数码管码和位选码”。“数码管码和位选码”因为早已经固定在Verilog代码中(SPI控制模块里)。如果你问我为什么要那么做?这纯粹是“故意”,为了就是仿真和测试SPI发送模块和SPI控制器。

1.module smg_controller

2.(

3. CLK, RST,

4. STCP, SDO, SCL,

5. //DO, SEND_SIG, DONE_SIG

6.);

7.

8. input CLK, RST;

9. output STCP, SDO, SCL;

10. //output [7:0]DO;

11. //output SEND_SIG, DONE_SIG;

12.

13. /*************************************/

14.

15. wire Send_Sig;

16. wire Done_Sig;

17. wire [7:0]DI;

18.

19. spi_module u1

20. (

21. .CLK( CLK ),

22. .RST( RST ),

23. .Send_Sig( Send_Sig ),

24. .Done_Sig( Done_Sig ),

25. .DI( DI ),

26. .SCL( SCL ),

27. .SDO( SDO )

28. );

29.

30. spi_controller u2

31. (

32. .CLK( CLK ),

33. .RST( RST ),

34. .Send_Sig( Send_Sig ),

35. .Done_Sig( Done_Sig ),

36. .DI( DI ),

37. .STCP( STCP )

38. );

39.

40./*************************************/

41.

42.endmodule

1. 这个Verilog代码比较简单,就是建立了TOP模块,用来连接SPI控制模块和SPI发送模

块。

2. 至于第5行,底10~11行被我注释掉了。为什么这些东西我还留着呢?其实有这样一个故

事的...

老实说,这一章实验是消耗我最长时间的了。我大约用了将近一整天的时间在测试,第一章和第二章的实验已经都被我修改了好几回,但是结果还是不尽人意。后来我在这个TOP模块将DI,Send_Sig 和 Done_Sig引出来,然后放到Modelsim里观察,最终才找到问题点。

1.`timescale 1 ns/ 1 ns

2.module smg_controller_vlg_tst();

3.

4. reg CLK;

5. reg RST;

6.

7. wire SCL;

8. wire SDO;

9. wire STCP;

10. //wire SEND_SIG;

11. //wire DONE_SIG;

12. //wire [7:0]DO;

13.

14. smg_controller i1

15. (

16. .CLK(CLK),

17. .RST(RST),

18. .SCL(SCL),

19. .SDO(SDO),

20. .STCP(STCP),

21. //.DONE_SIG( DONE_SIG ),

22. //.SEND_SIG( SEND_SIG ),

23. //.DO( DO )

24. );

25.

26. initial

27. begin CLK = 0; forever #20 CLK = ~CLK; end

28.

29. initial

30. begin RST = 0; #100; RST = 1; end

31.

32.endmodule

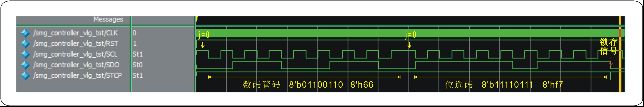

从载图上,可以很清楚的看见“1位SMG控制器”先发送一字节“数码管吗”“0x66”,然后再发送一字节“位选码”“0xf7”。最后,产生一个锁存信号。

阿对不起,这一章没有问题和答案 m( _ _ )m 。

( ⊙ o ⊙ )啊!终于完成了。如果仿真结果和上面的载图差不多,那么你就成功了。不妨下载到SF-EP1V2试试看吧。

源码(太大了)

/5

/5

用户1724981 2013-11-26 21:52

用户1373959 2010-5-18 21:30