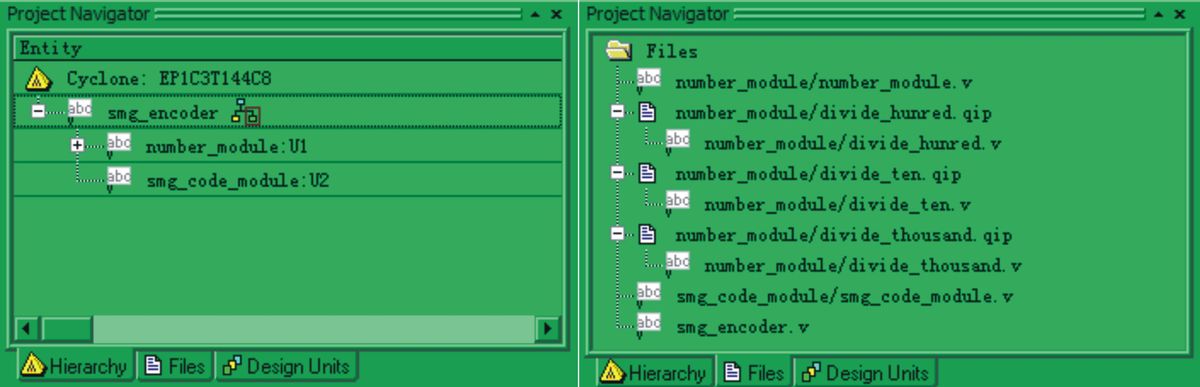

SMG加码器,划一句话说就是“千位取位逻辑”+ “数码管码加码模块”。以下的示意图说明了一切:

项目导航操作:

1.module smg_encoder

2.(

3. CLK, RST,

4. Data_In,

5. Thousand_Out, Hundred_Out, Ten_Out, One_Out

6.);

7.

8. input CLK;

9. input RST;

10. input [25:0]Data_In;

11.

12. output [7:0]Thousand_Out;

13. output [7:0]Hundred_Out;

14. output [7:0]Ten_Out;

15. output [7:0]One_Out;

16.

17. wire [3:0]Thousand;

18. wire [3:0]Hundred;

19. wire [3:0]Ten;

20. wire [3:0]One;

21.

22. number_module U1

23. (

24. .Data_In( Data_In ),

25. .Thousand( Thousand ),

26. .Hundred( Hundred ),

27. .Ten( Ten ),

28. .One( One )

29. );

30.

31. smg_code_module U2

32. (

33. .CLK( CLK ),

34. .RST( RST ),

35. .Thousand_In( Thousand ),

36. .Hundred_In( Hundred ),

37. .Ten_In( Ten ),

38. .One_In( One ),

39. .Thousand_Out( Thousand_Out ),

40. .Hundred_Out( Hundred_Out ),

41. .Ten_Out( Ten_Out ),

42. .One_Out( One_Out )

43. );

44.

45.endmodule

1. 以上的代码很简单而已,直接给上一个RTL 示意图更能解释一切。(示意图如下)

Testbench代码:

1.`timescale 1 ns/ 1 ns

2.module smg_encoder_vlg_tst();

3.

4. reg CLK;

5. reg [25:0] Data_In;

6. reg RST;

7.

8. wire [7:0] Hundred_Out;

9. wire [7:0] One_Out;

10. wire [7:0] Ten_Out;

11. wire [7:0] Thousand_Out;

12.

13. smg_encoder i1

14. (

15. .CLK(CLK),

16. .Data_In(Data_In),

17. .Hundred_Out(Hundred_Out),

18. .One_Out(One_Out),

19. .RST(RST),

20. .Ten_Out(Ten_Out),

21. .Thousand_Out(Thousand_Out)

22. );

23. initial

24. begin CLK = 0; forever #10 CLK = ~CLK; end

25. initial

26. begin RST = 0; #100; RST = 1; end

27. initial

28. begin Data_In = 26'd7821; end

29.

30.endmodule

Testbench代码没有什么苦难度,自己看着明白吧~

仿真载图:

从载图中可以看到,“Thousand_Out”的输出是 0x07 也就是“数字7”对应的数码管码,0x7f 对应“数字8”,0x5b对应“数字2”,0x06对应“数字1”。

╮(╯▽╰)╭ 唉~这一章没有“问题和答案”。

我们已经完成两个重要模块的设计了。下一章实验就是“SMG加码器”和“4位SMG控制器”的组合,形成SF-EP1V2独一无二的“SMG接口”。到目前为止,是不是觉得所有设计构思都很简单呢?但是,当这些简单的东西“团结”起来,就成为不简单的东西了。

源码:

/5

/5

用户1373959 2010-5-18 21:33