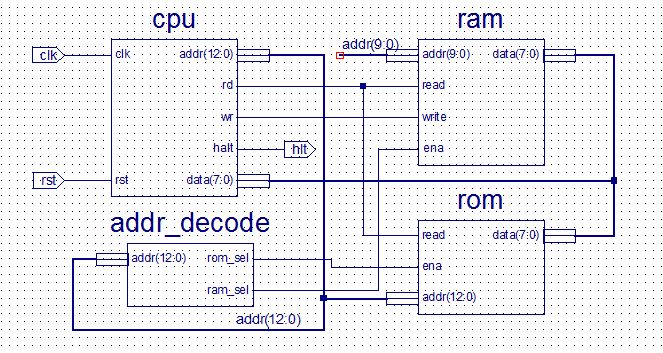

为了对cpu进行测试,需要有存储测试程序的rom和装载数据的ram、地址译码器。

1.地址译码器用于产生选通信号,选通rom或ram。

module addr_decode(

input [12:0] addr,

output reg rom_sel,

output reg ram_sel

);

always @(addr)

begin

casex(addr)

13'b1_1xxx_xxxx_xxxx: {rom_sel,ram_sel} <= 2'b01;

13'b0_xxxx_xxxx_xxxx: {rom_sel,ram_sel} <= 2'b10;

13'b1_0xxx_xxxx_xxxx: {rom_sel,ram_sel} <= 2'b10;

default: {rom_sel,ram_sel} <= 2'b00;

endcase

end

endmodule

2.rom用于装载测试程序。

module rom(

output [7:0] data,

input [12:0] addr,

input read,

input ena

);

reg[7:0] memory [13'h1fff:0];

assign data = (read && ena)? memory[addr] : 8'bzzzzzzzz;

endmodule

3.ram用于存放数据。

module ram(

inout [7:0] data,

input [9:0] addr,

input ena,

input read,

input write

);

reg [7:0] ram [10'h3ff:0];

assign data = (read && ena)? ram[addr] : 8'hzz;

always @(posedge write)

begin

ram[addr] <= data;

end

endmodule

///////////////////////////////////////////////////////////////

cpu与外围模块连接如下:

/5

/5

文章评论(0条评论)

登录后参与讨论