本文设计的是一种加权均值滤波算法,窗口大小是5(列)*1(行),适用于灰度图像实时视频处理,可以有效淡化视频竖条纹。同时为了保持图像的细节,采用如下图所示的加权窗口。

同时考虑到一场视频最左边和最右边的2列数据的特殊性,其窗口对应为:

最左边两列

最右边两列

代码接口定义如下表所示。

|

接口名称 |

输入输出 |

接口含义 |

|

I_clk_7m |

I |

视频采样时钟,实际为6.75MHz |

|

I_reset_n |

I |

系统复位信号,低复位 |

|

I_smooth_en |

I |

均值滤波使能信号,1:使能,0:不使能 |

|

I_data_vsync |

I |

输入视频场同步信号 |

|

I_data_valid |

I |

输入视频数据有效信号,1:视频信号,0:消隐信号 |

|

I_data_in[11:0] |

I |

输入视频数据信号 |

|

O_data_vsync |

O |

输出视频场同步信号 |

|

O_data_valid |

O |

输出视频数据有效信号,1:视频信号,0:消隐信号 |

|

O_data_out[11:0] |

O |

输出视频数据信号 |

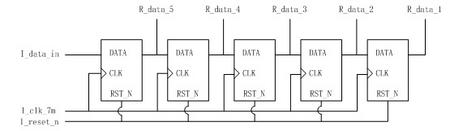

简单介绍下设计原理:由于采用的是5*1的窗口,不需要大规模数据缓存,窗口内相邻的视频数据相差一个时钟周期,使用触发器将原始视频数据缓存5级,分别对应5个寄存器信号。在同一时钟周期内的5个寄存器信号即为窗口内的5个数据,在同一时钟周期内可进行并行处理。

接下来,需要对窗口内的视频数据以16位基数进行加权处理,得到数值除以16后用来替换原有像素灰度值。

接下来,需要对窗口内的视频数据以16位基数进行加权处理,得到数值除以16后用来替换原有像素灰度值。

R_sum16 = R_data_5*2 + R_data_4*3 + R_data_3*6 + R_data_2*3 + R_data_1 *2

最左边两行:

R_sum16 = R_data_5*4 +R_data_4*6 + R_data_3*6

最右边两行:

R_sum16 = R_data_3*6 + R_data_2*6 + R_data_1*4

源代码不算很复杂,适合初学FPGA的同学作为学习参考,如有需要,请留下您的邮箱地址,每当回复数超过10 的整数倍时,我会统一发送!

如果文章或代码对您有帮助,麻烦您为我投上一票,您的支持是我不断进步和分享的动力,谢谢!

用户3878319 2018-2-8 11:29

用户1615289 2016-1-18 17:04

用户377235 2016-1-18 13:02

用户606370 2016-1-18 09:22

用户1854463 2015-11-26 08:57

用户1833262 2015-11-24 14:11

用户1573828 2015-11-13 14:54

用户1773537 2015-11-13 11:47

用户377235 2015-11-9 23:17

用户1769465 2015-10-1 23:12