基于FPGA的CIC以及补偿滤波器的设计

KevinWan

CIC滤波器最早是由Hogenauer提出的,后来出现了不少改进的结构形式。CIC滤波器的特点:

只需要加法器,无需乘法器

无需存储滤波器系数

结构易于拓展

无需外部控制

窗口长度控制截止频率方便

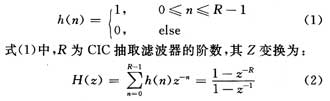

CIC也被称为无乘法运算的滤波器,概念上,滤波器计算可以理解为:一个输入数据到达后,寄存器中的数据向右平移以便接纳新的数据,然后滤波器将所有的存储器的数据相加,最后输出求和结果,可以通过下式描述:

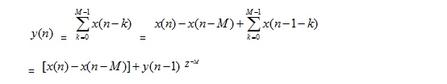

可以采用递归的方式实现:

图1: CIC原理结构图

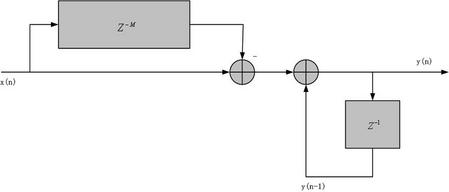

最基本的CIC抽取滤波器是指该滤波器的冲激响应具有如下形式:

以WCDMA中CIC为例,CIC抽取滤波器在f=0处的幅度值为R,单阶CIC滤波器如图所示。称频率区间0~fs/M为CIC滤波器的主瓣,而其他区间为旁瓣。由图可以看见随着频率的增大,旁瓣电平不断减小,单阶CIC滤波器的频率响应特**:

图2:单阶CIC的频率响应图

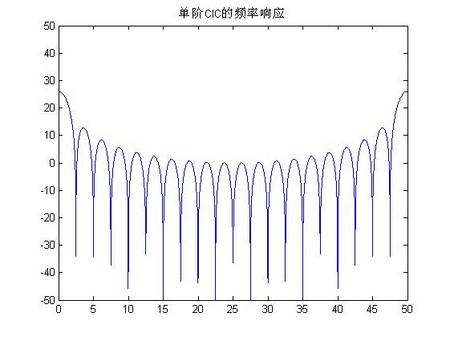

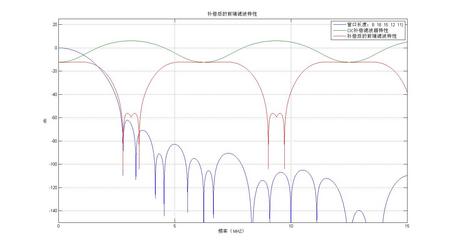

上图为单阶CIC的频率响应图,旁瓣衰减了12DB左右,说明阻带衰减很差,一般很难满足实用要求。为了降低旁瓣电平,可以采用多级CIC滤波器级联的办法来解决,4阶相同窗口长度的CIC的频率特性如下:

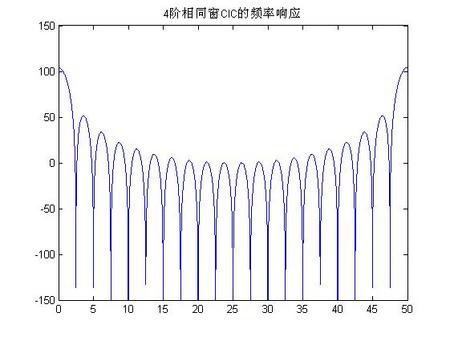

图3:4阶相同窗口长度的CIC的频率响应图

上图为4阶相同窗口长度CIC的频率响应图,旁瓣衰减了50DB左右,明显比单阶CIC旁瓣衰减的要多,但还是不够理想,一般采用各个窗口长度不相等的CIC串联,采用4阶窗口不相同的CIC频率响应图:

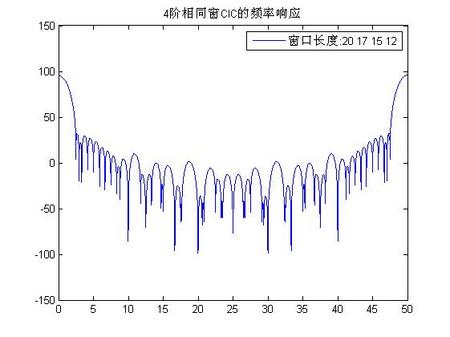

图4:4阶不同窗口长度的CIC的频率响应图

上图为4阶不同窗口长度CIC的频率响应图,旁瓣衰减了70DB左右,明显比单阶CIC和相同窗口的CIC旁瓣衰减的要多,由此可见4级级联的CIC滤波器具有70 dB左右的阻带衰减,基本能满足实际要求。比较理想,本系统采用这种方式设计多级CIC。

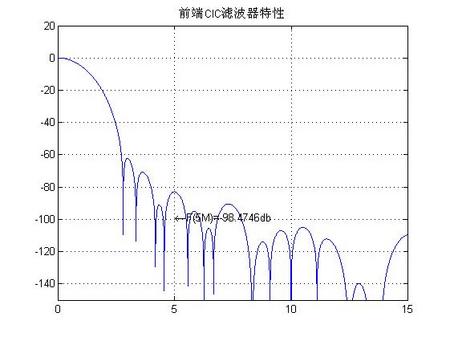

图5:前端CIC的频率响应图

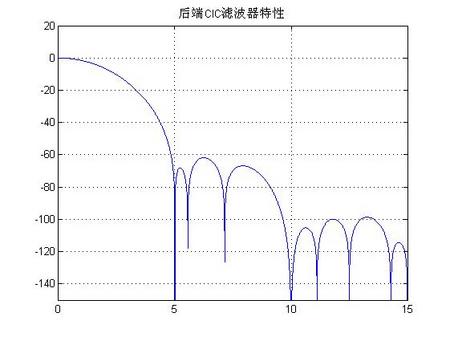

图6:后端CIC的频率响应图

FIR滤波器

FIR滤波器具有线性相位和稳定两大优点,他的突出特点是单位取样响应h(n)仅有有限个非零值。对于一个N阶的FIR滤波器,其具体形式如下:

FIR滤波器的实现方法按照结构主要可以分为三种:

直接结构实现的FIR滤波器

转置结构实现的FIR滤波器

分布式算法实现的FIR滤波器

FIR补偿滤波器

当CIC的M值(即states)很大时,他很难有一个平坦的通带,在数字下变频中,补偿滤波器放在CIC之后,而在数字上变频中,补偿滤波器作为预处理放在CIC之前,总之,CIC补偿滤波器是应用在多采样率的系统中,是在牺牲采样率的基础上,获得高效的硬件性能。

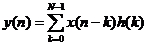

CIC的频率响应特性为:

当R很大时,上式公式就可以转换为sinc公式。而补偿滤波器要达到补偿效果,其频率响应就应该是CIC滤波器频率响应的倒数,即:

所以,CIC补偿滤波器也可以成为“inverse sinc filter”,在多采样率的系统中,CIC补偿滤波器作为多采样率滤波器,可以是插值或者抽取滤波器,但采样率变化最少是2。CIC补偿滤波器Matlab代码如下:

%CIC顶部补偿滤波器

slen=floor(2.2/FS*FLEN);

zv(1:FLEN/SEG_LEN)=1;

for m=1:slen

zv(m)=(F_tf(slen)/F_tf(m));

end

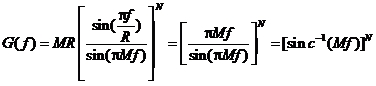

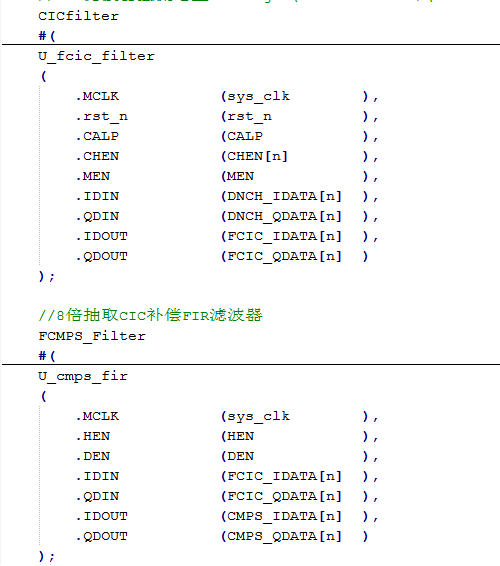

采用8倍抽取的方式设计FIR补偿滤波器,采用IQ复用的方式,节省硬件乘法器和逻辑资源。

图7:CIC补偿FIR的频率响应图

源代码:

/4

/4

用户377235 2014-3-18 11:12

不是用工具产生的,是代码写的

用户443418 2014-3-11 19:53