Altera CycloneIV SerDes应用和仿真

KevinWan

SerDes是SERializer和DESerializer的英文缩写,即串行收发器。

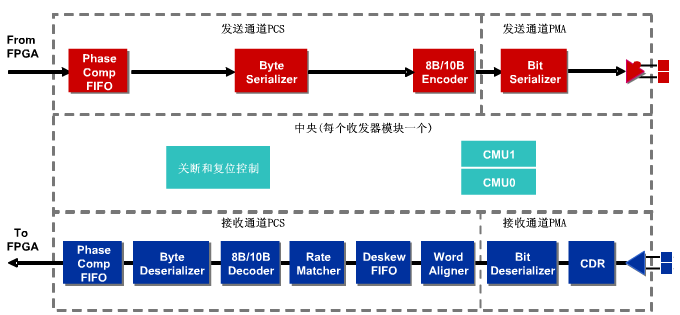

Altera SerDes的基本结构:

n PMA(Physical media attachment):物理介质接入层,主要完成数据串并/并串转换,包含:IO缓冲器(模拟电路)、数据时钟恢复(CDR)、数据串并/并串转换serializer/deserializer (SERDES)、可编程的预加重和均衡改善串行数据通道的性能。

n PCS(Physical coding sublayer):物理编码层,主要完成数据的编解码,数据缓冲,8B/10B编解码等。

各个部件的原理在其他博文中有介绍,大家可以参考:

http://bbs.ednchina.com/BLOG_ARTICLE_3012346.HTM

http://bbs.ednchina.com/BLOG_ARTICLE_3012285.HTM

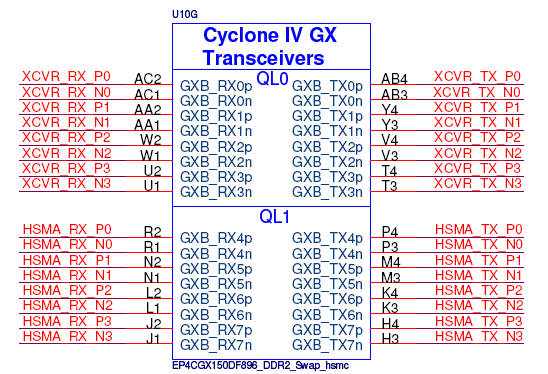

RX与TX管脚连接图:

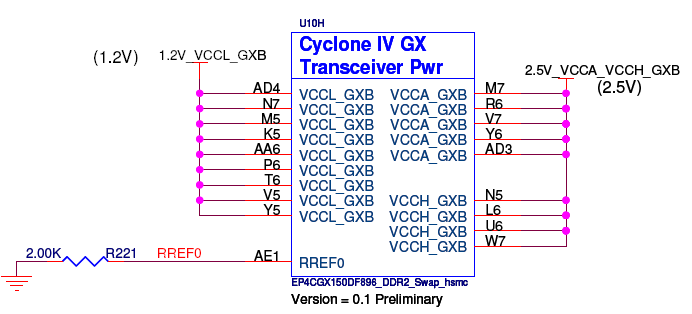

电源和校验部分连接:

仿真方法同另一篇博文,这里就不再详细介绍了:

http://bbs.ednchina.com/BLOG_ARTICLE_3018611.HTM

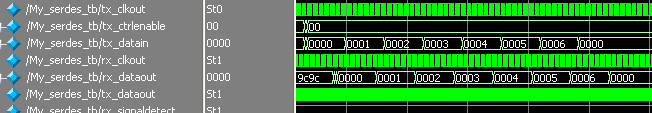

自环测试结果:

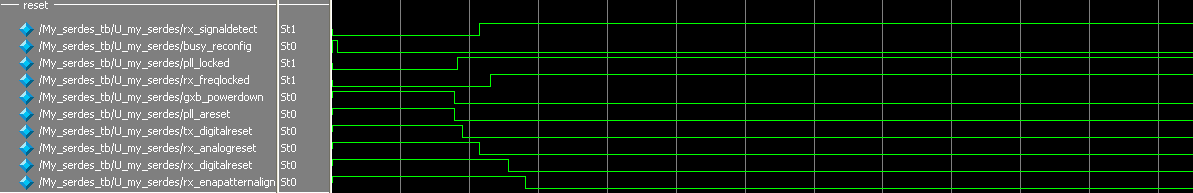

Serdes复位时序图:

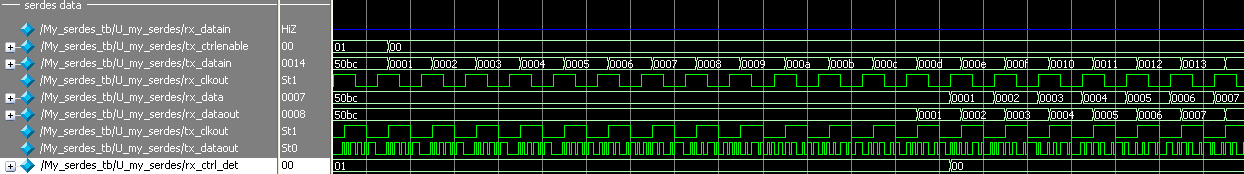

Serdes输入输出图:

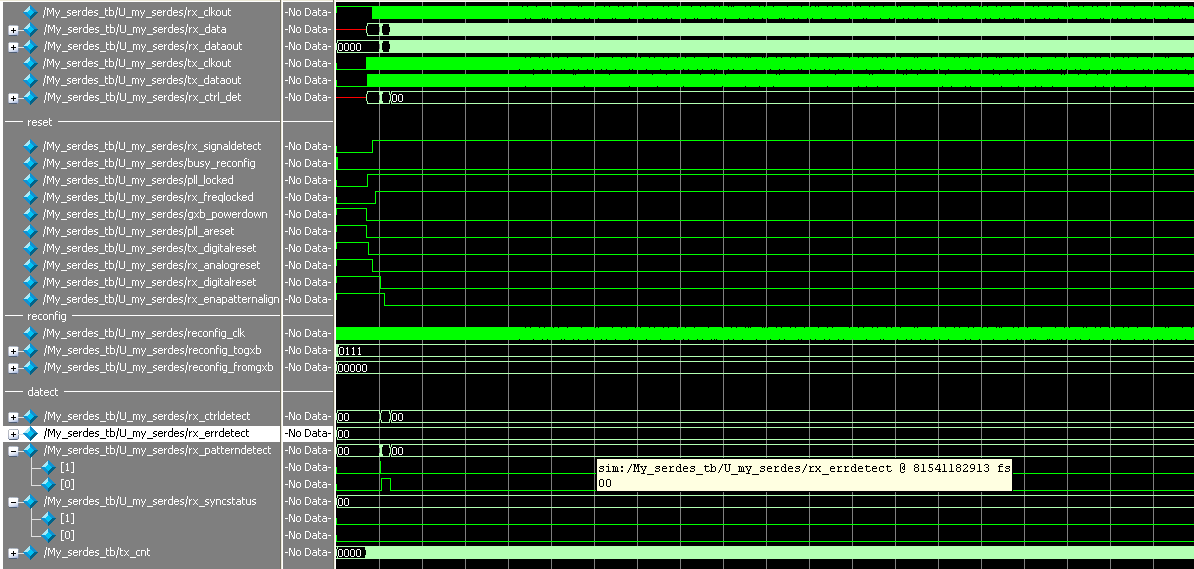

整体的仿真图:

代码设计主要注意SerDes的各个部分复位的顺序,以及检测K码等。

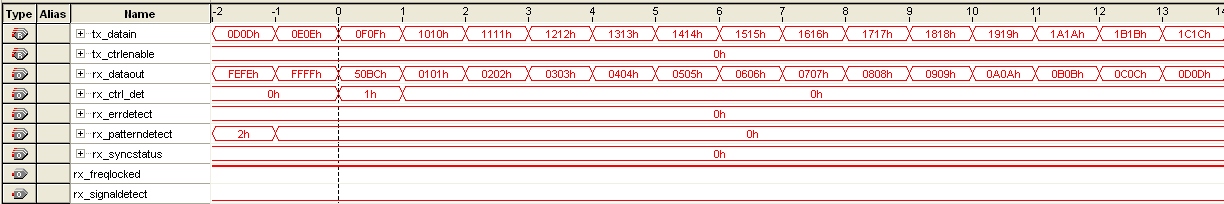

自环SignalTap图:

/4

/4

用户1778655 2014-11-25 11:27