AHB重点难点总结

编辑要给我加精华啊啊啊啊啊啊啊啊!

迄今为止最满意的难点和重点分析,下面的这些问题是很多人都会迷惑的地方,我是思考了很久,参考了许多论坛,问了我们老大得出的结论。

前言:

如果你之前看过一些总线或者类似总线的协议的话,那么你第一次看AHB协议可能感觉还行,不是很难,觉得都能看懂;如果你多看几遍或者看一遍去做和AHB相关的设计的时候,譬如你模拟AHB-Master,模拟AHB-Slave,然后让它们通信,你就会发现AHB协议中有些地方你没看懂,而且你会发现SPEC有些地方写的不是很明显,需要你结合前后文反复推敲,才能得到你想要的答案;关于手册其实写的已经很好了,比起国内的一些设计公司的手册,不知好多少倍,只是有些关键点是一笔带过,我想可能是为了让你去它们公司咨询或者购买它们的IP吧,如果都轻易搞懂了,那岂不是,哈哈!后面是我瞎扯淡!

下面进入正题:

一:模块接口(关于接口的含义,大家可以参考SPEC,在此不赘述)

AHB-Master接口

AHB_Slave接口

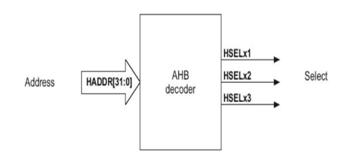

Decoder接口

Arbiter接口

二:重点和难点分析

1、关于Hready信号

英文版手册对Hready解释如上,我主要想解释一下红线部分,大意是说,挂载在总线上的Slave要求它的Hready即为输入也为输出,什么意思呢,其实是每个Slave都有一个Hready输出,这些输出经过一个MUX(记住,不能是简单的and或者or,有很多人这样以为,至于为什么,大家可以参考下图2稍作分析就知道原因了)再最终选择出一个Hready_o,这个Hready_o会输入到每个Master和每个slave及Arbiter。如图1,以2个M,2个S为例,图中的sel4产生有些难度。

图1

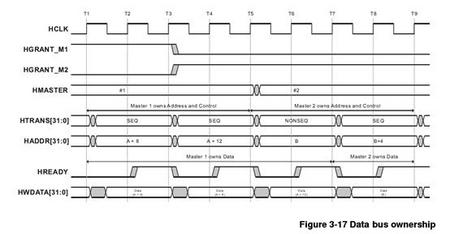

2、结合图2(SPEC中是图3-17)解释图1中的选择信号可以如何产生及图2的含义

图2

图2中Hgrant信号是图1中Arbiter根据每个M发出的Hbusreq结合自身的优先级算法(没有规定何种算法,设计者可以根据自身需求选择,如Fair-access,Round-robin)及control信号仲裁得到的结果,不是随便切换的,它的切换点非常有技巧,能够保证全程流水线。

从图2中可以看出,虽然Hgrant2切换为M2(为什么这个地方切换,是上面我提到的相关技术所致),但是M2并不能立即获得总线使用权,而是在Hgrant2为高且Hready(注意这个地方的Hready就是我上面说的经过MUX后的Hready_o)为高时,Hmaster才被切换为2,原因是保证上一个传输的最后一个control和地址发出去,进而这个时候M2可以发送control信号和addr信号。所以对应图1,sel1和sel2这些信号可以为Hmaster,而sel6可以为Haddr。

再看图2,T5时刻以后control已经是M2的了,但是data仍然是M1对应的(就是图中对应的Master owns data那个注释),原因很简单,AHB是采用流水线技术,分为地址阶段和数据阶段。所以当control和addr信号切换的时候,data并不能切换,而是要保证最后一个control要读或者写的数据完成才可以。所以Hready对应的sel4可以利用addr向后延时一拍,同时检测到Hready为1时(保证数据被采样)才进行切换,Hwdata和Hrdata对应的sel也可以用上面的方法。

3、从上面的分析不难得出如下结论

1)Master在检测到Hready为1时发送一个control和addr,所以Slave也可以在检测到Hready为1时进行control和addr的采样,在采样到有效的control和addr后一个周期当Hready为时进行数据的采样。

2)Slave在默认情况下最好将Hready设置为1(这个也是ARM公司推荐的),这样可以让Arbiter及时将总线使用权进行切换,如图2中,如果Hready提前为1,那么Hmaster会提前变为#2。

3)整个总线最难设计的部分就是Arbiter,大家可以参考接口图可以看出,master和salve有的信号它都有,它会监测Master和Slave的情况,及时切换总线使用权,保证效率的最大化。

sunyzz 2014-8-24 11:18

sunyzz 2014-8-24 10:00

用户244424 2014-8-24 00:33

sunyzz 2014-8-14 18:22

用户403664 2014-8-14 16:53