五: 综合及时序分析

前言:

我们将一个idea用rtl代码实现,然后经过仿真验证确保功能正确,但是到这一步离芯片出厂还有十万八千里,应该来说,如果不是超级复杂的idea,其实写代码反而是整个ic设计中最容易的事情了,因为你如果画好时序图,分析足够透彻,基本上就像写普通的文档一样。

代码完毕后一般还会进行lint的检查,检查一些语法上的不规范或者错误,也会进行cdc的检查,确保cdc处理的正确,到此时代码阶段基本就会停止,进入code freeze的状态,后面再出现问题,如果不是很大的,基本上就不允许修改rtl代码,而是要进行netlist网表级或者版图级的ECO,否则从头开始的话,整个流程会很长很长。

代码code freeze后就进入了所谓的综合阶段,综合在干神马,用一个公式表示如下:

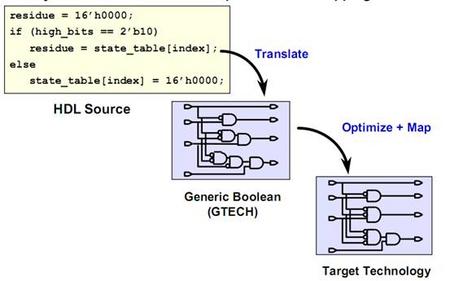

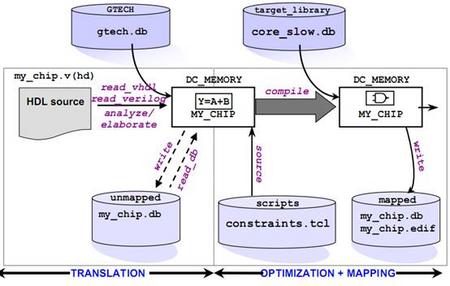

综合(synthesis)= 翻译(translation)+ 优化(optimization)+ 映射(mapping),

翻译其实就是将代码对应到诸如与非,反向,触发器等基本的门,优化是利用施加的约束限制将芯片的面积,速度等控制在最优解上,映射就是将基本门对应到诸如台积电等第三方提供的工艺库中。

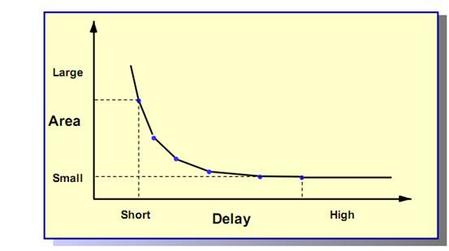

综合其实就是基于第三方工艺库在面积,功耗,速度之间需找一个最佳值,这个值满足用户的需求且是最优的。

/3

/3

文章评论(0条评论)

登录后参与讨论