终于有点时间了,继续我们的Robei介绍吧

插个小话题,其实网上有Robei的介绍,但总带上国产的帽子,我感觉不妥,设计的软件为什么都得戴个国产帽子,以后怎么走出去,因为Robei面对的人群是热爱FPGA的好孩子,再说了altera等软件在他们国度有怎么称呼的吗,Robei是Robei,面向世界,走向未来。

Robei软件的下载地址:http://robei.com/?cat=4&lang=zh

当你安装完软件后,会生成一个Robei的example包,初次使用你可以打开软件包的程序,感受下Robei软件的魅力哦。

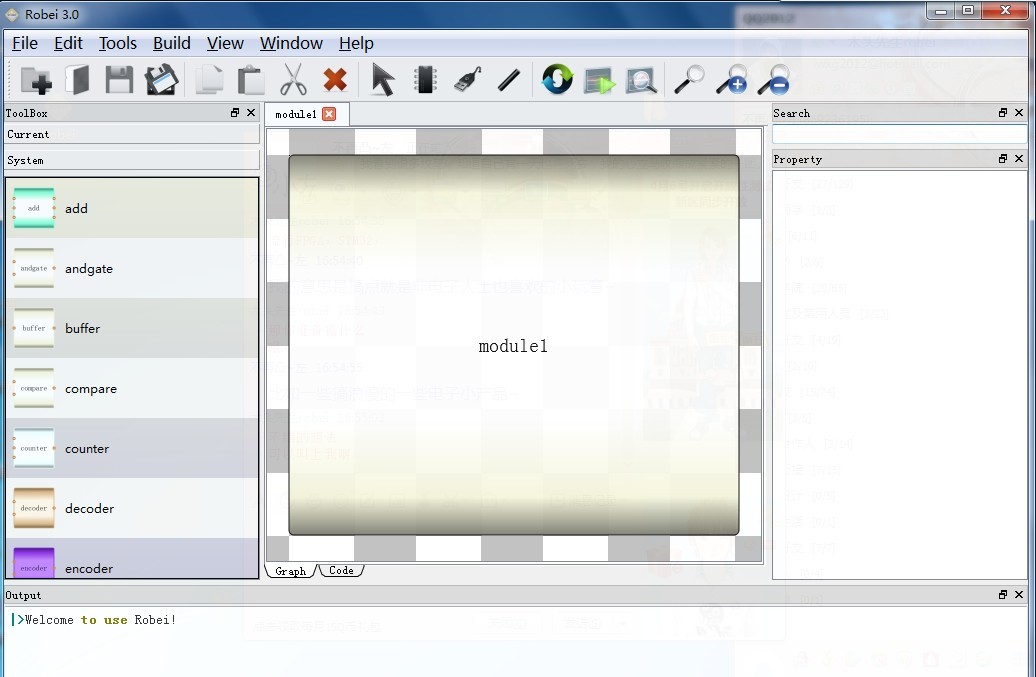

任何软件都有工作界面,Robei的工作界面十分简单,先上传一张看看吧!!

主界面

这就是Robei的主界面,映入眼帘的是工作框,最顶部的是菜单栏,下面就是工具栏了,工作框下面就是软件提示信息,在这里可以看到软件提示用户操作的正确性哦。

在工作框左边是工程里面建立的模块,用户可以清晰的看到自己建立的模块了。

Robei软件使用是需要注册的,目前针对教育用户,可联系QQ243675849免费提供教育用户试用,Robei注册方式如下操作:点击菜单栏的help-----register,提交软件序列号即可使用了。

如果看到这样的提示,那恭喜你软件可以授权使用啦!!

|

A

|

B

|

Y

|

|

0

|

0

|

0

|

|

0

|

1

|

0

|

|

1

|

0

|

0

|

|

1

|

1

|

1

|

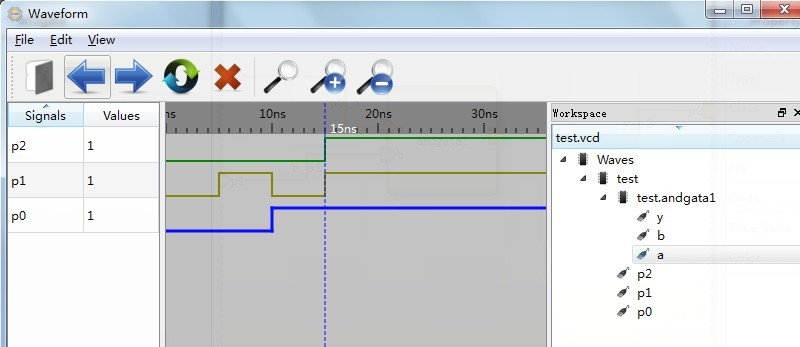

Y=A*B;

熟悉了与门逻辑,我们就开始吧!!

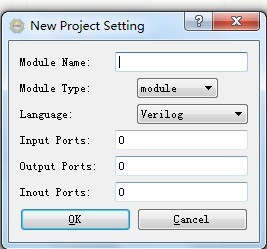

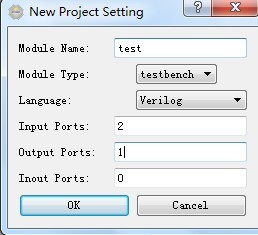

打开Robei软件,点击File---New(也可以直接在工具栏第一个带有+文件夹的按钮上轻轻点击下哦),出现以下界面

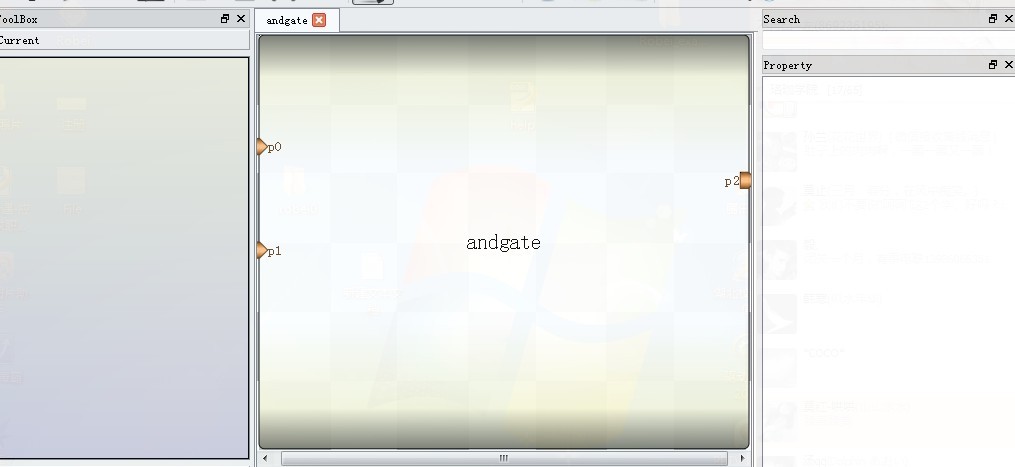

这样就到了建立文件,Module Name (模块名字)这里是与门,我就取名为andgate(PS:不要与关键字等相同)Module Type(模块类型),这里有module 和 testbench两种,module是建立的模块,testbench是对模块的测试,Robei的使用是先建立各个module文件,再对module进行测试才可以看到美丽的波形哦(PS:在这里与颜色相关的地方是可以自己编辑的哦)。然后就是Language(暂时只支持verilog,以后会有更多语言的版本的),再就是端口申明了,你有几个输入,几个输出,与门测试逻辑有2个输入,一个输出。OK,以后就到工作区域啦,如下图

initial begin

p0=1'b0;

p1=1'b0;

#5

p0=1'b0;

p1=1'b1;

#5

p0=1'b1;

p1=1'b0;

#5

p0=1'b1;

p1=1'b1;

#5

$finish;

end

保存后编译,运行run,编译代码。

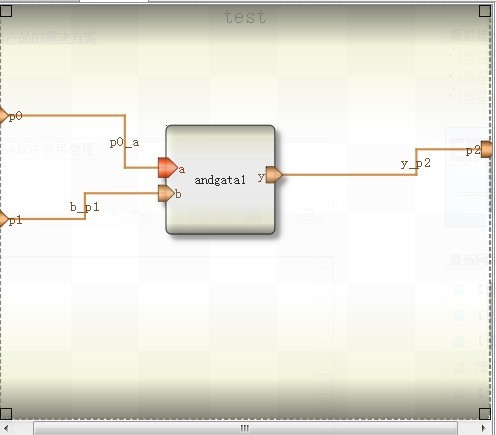

在点击tool下面的connect,将测试端口与模块端口连接起来,保存后运行run,生成仿真激励文件。

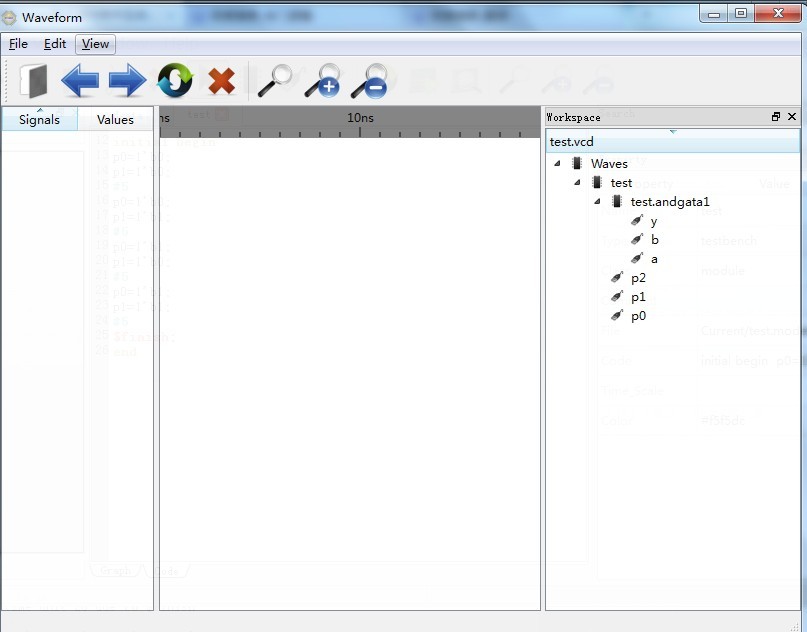

点击build----wave,出现如下波形

/5

/5

用户1639460 2012-12-16 12:19

用户1622604 2012-4-14 00:51

用户377235 2012-4-12 18:51