本文主要介绍ZYNQ PS + PL异构多核案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx SDK 2017.4。

axi_timer_pwm_demo案例

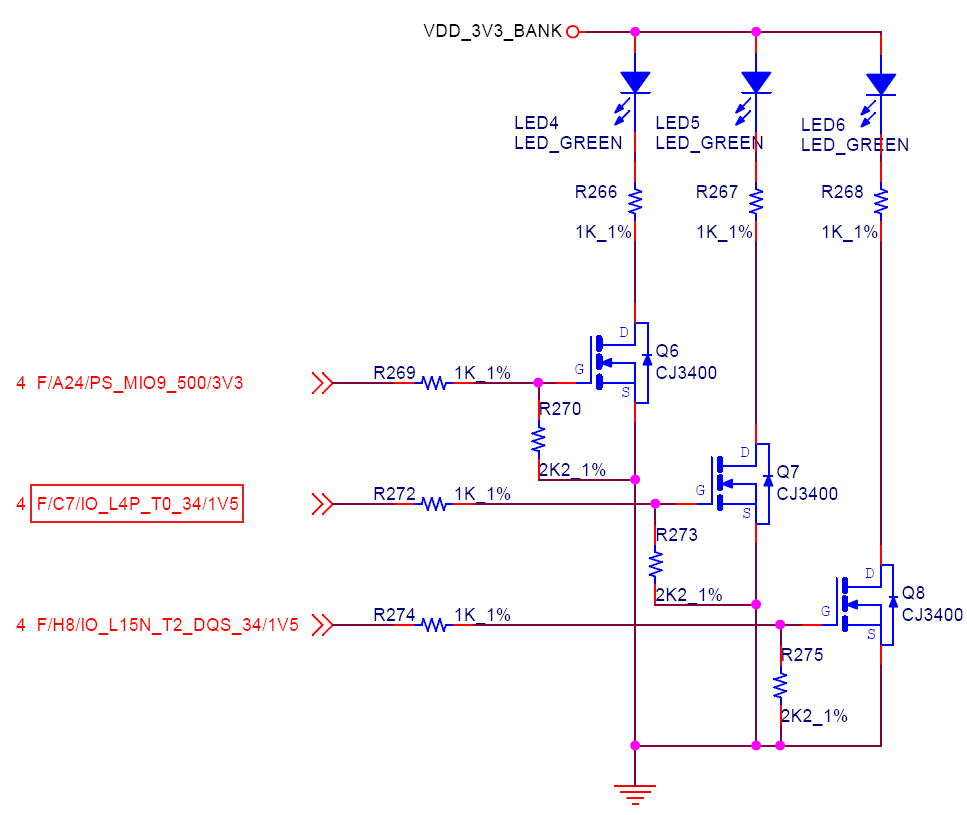

1 案例功能案例功能:PS端通过AXI4-Lite总线发送命令至PL端AXI Timer IP核,IP核再根据命令通过PWM方式控制评估底板PL端LED5的状态。

请点击输入图片描述(最多18字)

2. 操作说明2.1 基于裸机测试加载PS端裸机程序、PL端程序后,即可看到评估底板的LED5约每隔0.5s亮灭一次。

2.2 基于Linux测试将本案例的PL端.bin格式可执行文件复制到"/lib/firmware/"目录下,并将PL端可执行文件重命名为system_wrapper.bin,然后执行如下命令加载PL端可执行文件。

Target# echo system_wrapper.bin > /sys/class/fpga_manager/fpga0/firmware

请点击输入图片描述(最多18字)

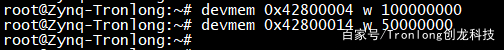

执行如下命令,通过IP核寄存器配置PWM周期和PWM占空比。

Target# devmem 0x42800004 w 100000000 //配置TLR0寄存器的值为100000000,则PWM周期=(100000000+2)x(1/100MHz),约为1s

Target# devmem 0x42800014 w 50000000 //配置TLR1寄存器的值为50000000,则则PWM占高值=(50000000+2)x(1/100MHz),约为0.5s,PWM占空比=(1-0.5s/1s)x100%,约为50%

请点击输入图片描述(最多18字)

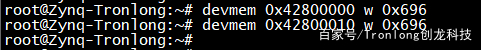

执行如下命令设置Timer 0与Timer 1为PWM向下计数模式。

Target# devmem 0x42800000 w 0x696

Target# devmem 0x42800010 w 0x696

请点击输入图片描述(最多18字)

命令执行后,即可看到评估底板的LED5每隔0.5s亮灭一次。

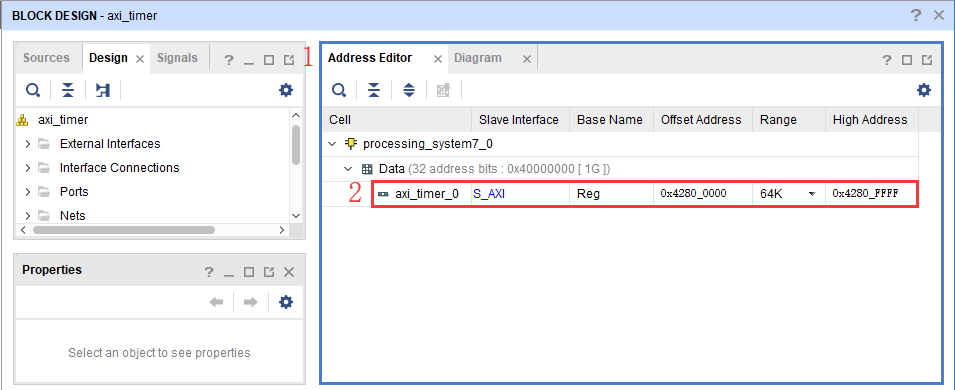

2.3 Vivado工程说明点击BLOCK DESIGN开发界面下的"Address Editor"选项,可查看IP核分配的地址为0x42800000,PS端可通过该地址对IP核进行控制。

请点击输入图片描述(最多18字)

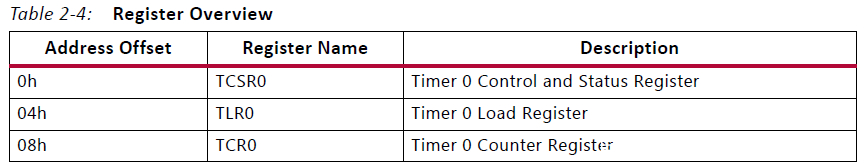

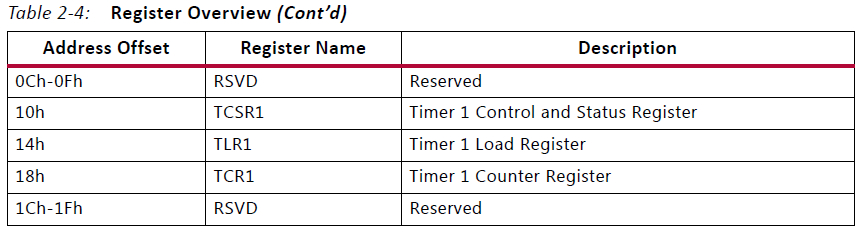

2.4 IP核配置AXI Timer IP核开发文档为产品资料“6-开发参考资料\Xilinx官方参考文档\”目录下的pg079-axi-timer.pdf。根据文档,通过寄存器TLR0(Timer 0)可配置PWM周期;通过寄存器TLR1(Timer 1)可配置PWM占空比。

请点击输入图片描述(最多18字)

请点击输入图片描述(最多18字)

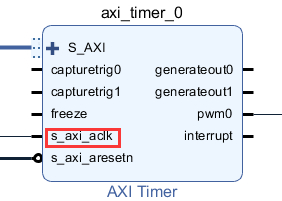

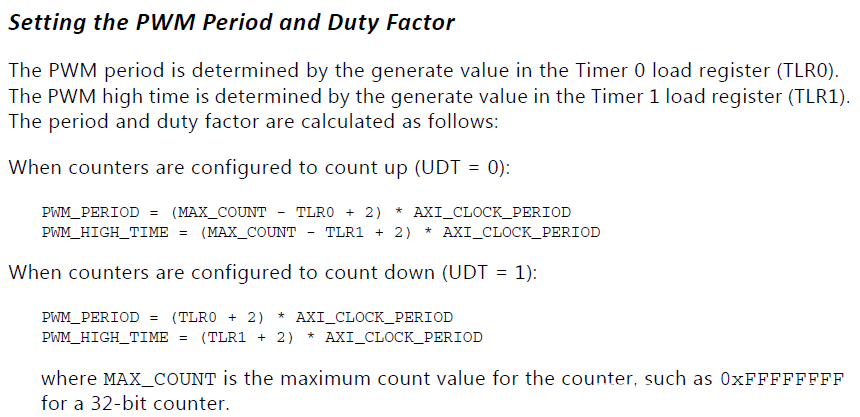

如采用PWM向下计数模式(count down),PWM周期与占空比的计算公式如下,公式中的100MHz为IP核所接的s_axi_aclk时钟。

* PWM周期=(TLR0+2)x(1/100MHz)

* PWM占高值=(TLR1+2)x(1/100MHz)

* PWM占空比=(1-PWM占高值/PWM周期)x100%

请点击输入图片描述(最多18字)

如需获取案例源码、TL6678ZH-EVM评估板或其他产品详细资料,欢迎留言或者私聊!

作者: Tronlong, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3881012.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/4

/4

文章评论(0条评论)

登录后参与讨论