本文主要介绍瑞芯微RK3568J+紫光同创Logos-2的B码对时案例,开发环境如下:

Windows开发环境:Windows 7 64bit、Windows 10 64bit

Pango Design Suite(PDS):PDS_2022.2-SP3

IRIG-B码对时典型应用

IRIG-B码对时可应用于继电保护装置、电力RTU、电力录波器、通讯管理机、电能质量在线监测等领域。创龙科技已基于TL3568F-EVM评估板(RK3568J+Logos-2)实现IRIG-B码对时方案,降低了终端用户的开发难度,缩减了研发时间,可快速进行产品方案评估与技术预研。

图 1

IRIG-B码对时原理

IRIG-B(inter-range instrumentationgroup-B)码是一种时间同步标准,通常用于精确的时间测量和数据同步,广泛应用于电力、通信、航空等领域。

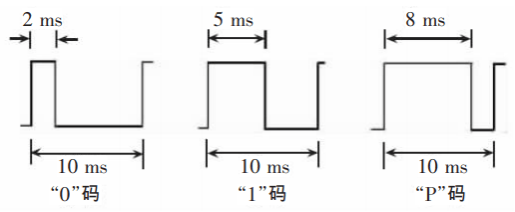

IRIG-B码为每秒一帧的时间串码,一帧串码中包含100个码元,频率为1KHz,即每个码元占用10ms时间。IRIG-B码基本的码元为"0"码元、"1"码元和"P"码元,"0"码元和"1"码元对应的脉冲宽度为2ms和5ms,"P"码元为位置码元,对应的脉冲宽度为8ms,IRIG-B码信息的基本码元的示意图如下所示。

图 2

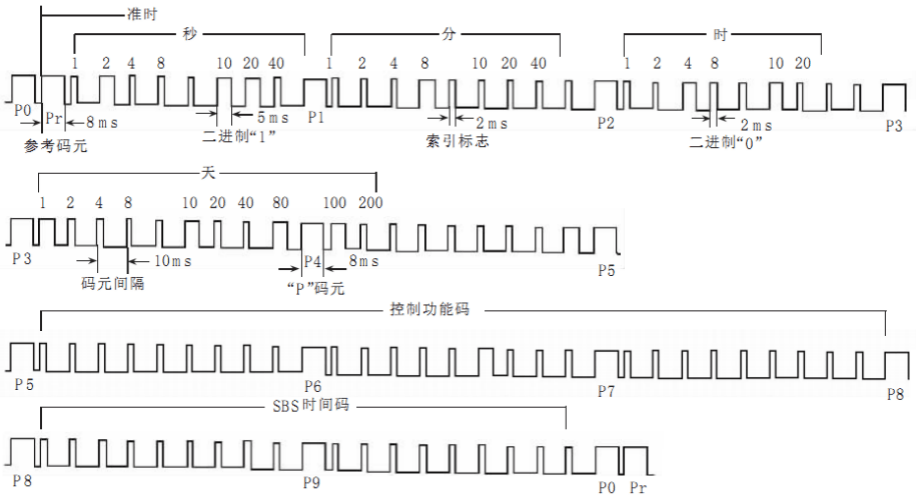

下图为一帧的IRIG-B码脉冲序列结构示意图。连续两个"P"码元表示整秒的开始,第二个"P"码元的脉冲前沿为“准时”参考点,定义其为"Pr"。每10个码元有一个位置码元,共有10个,定义其为P1,P2,…,P9,P0。IRIG-B 码时间格式的时序为秒、分、时、天,所占信息位分别为:秒7位、分7位、时6位、天10位,其位置在P0 ~ P5之间。

通常,从"Pr"开始对码元进行编号,分别定义为第0,1,2,…,99码元,则“秒”信息位于第1、2、3、4、6、7、8码元,“分”信息位于第10、11、12、13、15、16,17码元,“时”信息位于第20、21、22、23、25、26码元,“天”信息位于第30、31、32、33、35、36、37、38、40、41码元。

图 3

基于RK3568J+Logos-2的IRIG-B码对时方案

本文主要介绍创龙科技TL3568F-EVM评估板(RK3568J+Logos-2)基于FPGA端(Logos-2)实现IRIG-B码信号解析功能。

为了简化描述,本文仅摘录部分方案功能描述与测试结果。

(1)案例说明

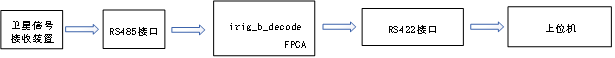

评估板FPGA端(Logos-2)通过FPGA RS485串口获取卫星时钟同步装置输出的IRIG-B信号,并对IRIG-B信号进行解码,将其转化为时间信息,然后通过FPGA RS422串口以每间隔一秒发送一次的频率将时间发送至上位机,并通过串口调试助手进行显示。程序功能框图如下所示。

图 4

(2)案例测试

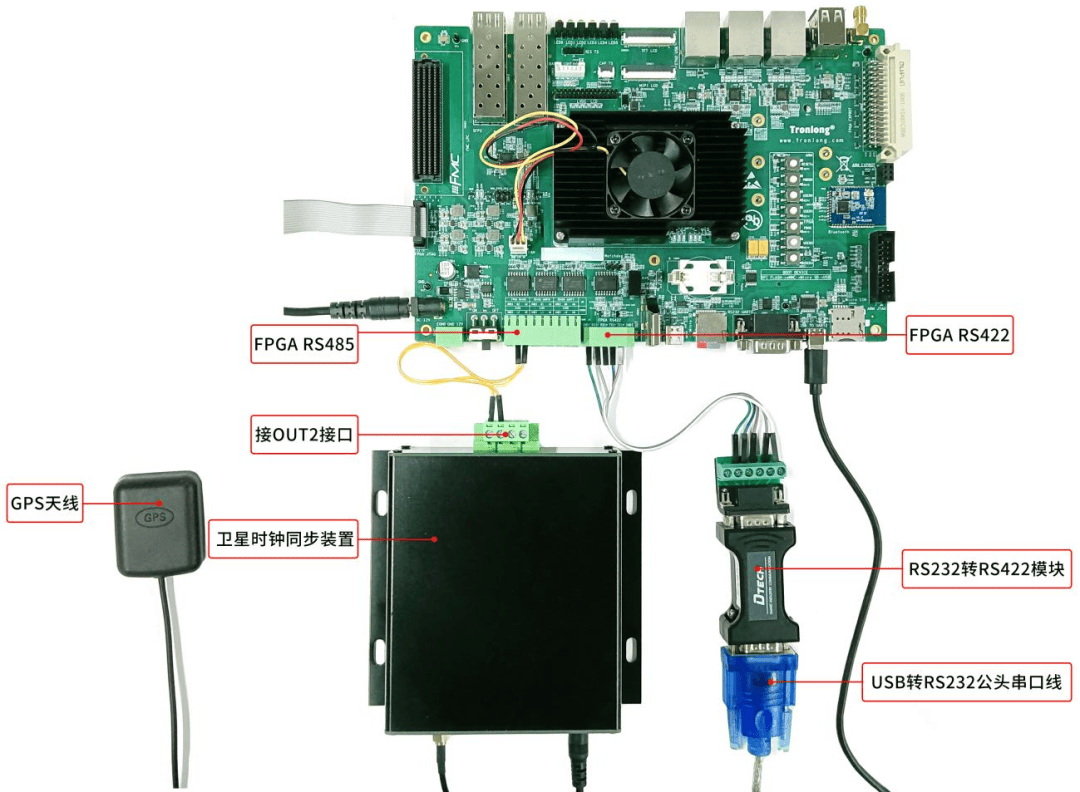

将卫星时钟同步装置的ANT接口连接至GPS天线模块,将卫星时钟同步装置的OUT2接口连接至评估板的FPGA RS485接口,将评估板FPGA RS422串口连接至PC机的USB接口,硬件连接如下图所示。

图 5

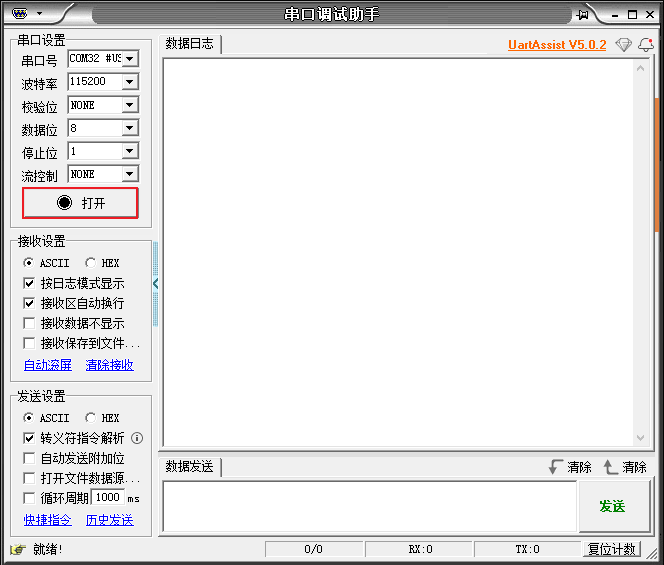

将评估板上电,请先加载运行FPGA端可执行程序。

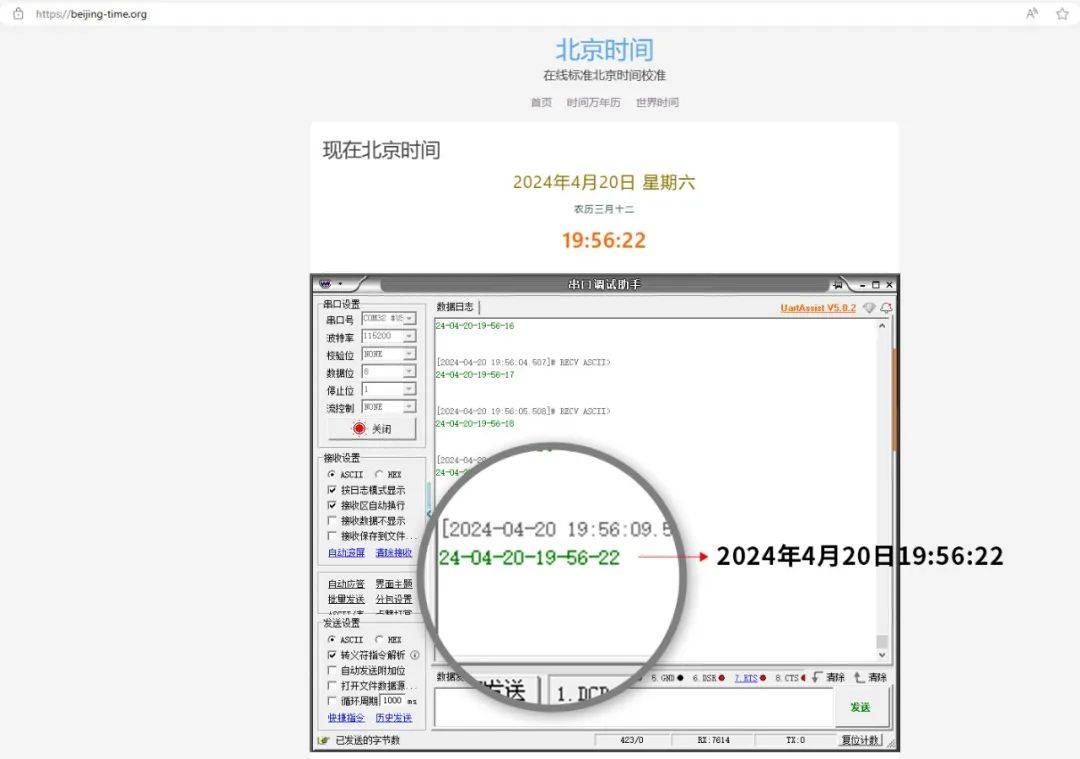

打开串口调试助手,点击“打开”按钮,此时可查看串口调试助手将打印卫星时钟同步装置输出的IRIG-B信号解码后转化的时间信息。可打开浏览器搜索北京时间对比查看时间是否一致,如下图所示。

图 6

图 7

/1

/1

文章评论(0条评论)

登录后参与讨论