一、SPI总线

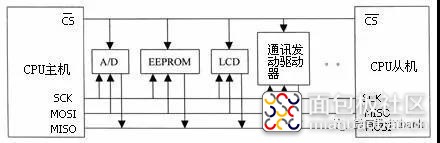

串行外围设备接口SPI(serial peripheral interface)总线技术是Motorola公司推出的一种同步串行接口,Motorola公司生产的绝大多数MCU(微控制器)都配有SPI硬件接口,如68系列MCU。SPI 用于CPU与各种外围器件进行全双工、同步串行通讯。SPI可以同时发出和接收串行数据。它只需四条线就可以完成MCU与各种外围器件的通讯,这四条线是:串行时钟线(CSK)、主机输入/从机输出数据线(MISO)、主机输出/从机输入数据线(MOSI)、低电平有效从机选择线CS。这些外围器件可以是简单的TTL移位寄存器,复杂的LCD显示驱动器,A/D、D/A转换子系统或其他的MCU。

当SPI工作时,在移位寄存器中的数据逐位从输出引脚(MOSI)输出(高位在前),同时从输入引脚(MISO)接收的数据逐位移到移位寄存器(高位在前)。发送一个字节后,从另一个外围器件接收的字节数据进入移位寄存器中。主SPI的时钟信号(SCK)使传输同步。其典型系统框图如下图所示。

SPI主要特点有: 可以同时发出和接收串行数据;

• 可以当作主机或从机工作;

• 提供频率可编程时钟;

• 发送结束中断标志;

• 写冲突保护;

• 总线竞争保护等。

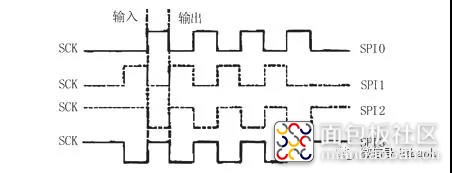

图2示出SPI总线工作的四种方式,其中使用的最为广泛的是SPI0和SPI3方式(实线表示):

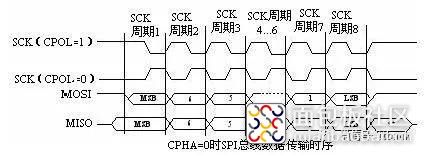

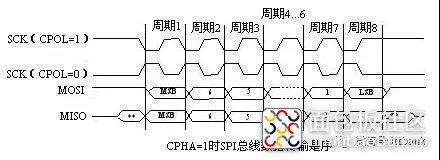

SPI 模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。如果 CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。SPI主模块和与之通信的外设音时钟相位和极性应该一致。SPI总线接口时序如图所示。

二、CAN总线

什么是CAN总线?

CAN全称为Controller Area Network,即控制器局域网,由德国Bosch 公司最先提出,是国际上应用最广泛的现场总线之一。CAN 是一种多主方式的串行通讯总线,基本设计规范要求有高的位速率、高抗电磁干扰性,而且要能够检测出总线的任何错误。当信号传输距离达10Km 时CAN 仍可提供高达50Kbit/s 的数据传输速率。

CAN 具有十分优越的特点:

A、较低的成本与极高的总线利用率;

B、 数据传输距离可长达10Km,传输速率可高达1Mbit/s;

C、可靠的错误处理和检错机制,发送的信息遭到破坏后可自动重发;

D、节点在错误严重的情况下具有自动退出总线的功能;

E、报文不包含源地址或目标地址仅用标志符来指示功能信息和优先级信息;

由于人为、自然、其它外界环境的影响和人们对公交系统的安全可靠性、真实、实时性的追求,使得我们对通信方式,通信设备有了更高的要求,基于CAN总线的网络则成为我们最佳的选择

CAN总线

现场总线是当今自动化领域技术发展的热点之一,被誉为自动化领域的计算机局域网。它的出现为分布式控制系统实现各节点之间实时、可靠的数据通信提供了强有力的技术支持。CAN(Controller Area Network)属于现场总线的范畴,它是一种有效支持分布式控制或实时控制的串行通信网络。较之目前许多RS-485基于R线构建的分布式控制系统而言。

基于CAN总线的分布式控制系统在以下方面具有明显的优越性:

首先,CAN控制器工作于多主方式,网络中的各节点都可根据总线访问优先权(取决于报文标识符)采用无损结构的逐位仲裁的方式竞争向总线发送数据,且CAN协议废除了站地址编码,而代之以对通信数据进行编码,这可使不同的节点同时接收到相同的数据,这些特点使得CAN总线构成的网络各节点之间的数据通信实时性强,并且容易构成冗余结构,提高系统的可靠性和系统的灵活性。而利用RS-485只能构成主从式结构系统,通信方式也只能以主站轮询的方式进行,系统的实时性、可靠性较差;

其次,CAN总线通过CAN控制器接口芯片82C250的两个输出端CANH和CANL与物理总线相连,而CANH端的状态只能是高电平或悬浮状态,CANL端只能是低电平或悬浮状态。这就保证不会出现象在RS-485网络中,当系统有错误,出现多节点同时向总线发送数据时,导致总线呈现短路,从而损坏某些节点的现象。而且CAN节点在错误严重的情况下具有自动关闭输出功能,以使总线上其他节点的操作不受影响,从而保证不会出现象在网络中,因个别节点出现问题,使得总线处于“死锁”状态。

而且,CAN具有的完善的通信协议可由CAN控制器芯片及其接口芯片来实现,从而大大降低系统开发难度,缩短了开发周期,这些是只仅仅有电气协议的RS-485所无法比拟的。另外,与其它现场总线比较而言,CAN总线是具有通信速率高、容易实现、且性价比高等诸多特点的一种已形成国际标准的现场总线。这些也是目前 CAN总线应用于众多领域,具有强劲的市场竞争力的重要原因。

CAN (Controller Area Network)即控制器局域网络,属于工业现场总线的范畴。与一般的通信总线相比,CAN总线的数据通信具有突出的可靠性、实时性和灵活性。由于其良好的性能及独特的设计,CAN总线越来越受到人们的重视。它在汽车领域上的应用是最广泛的,世界上一些著名的汽车制造厂商,如BENZ(奔驰)、BMW(宝马)、PORSCHE(保时捷)、ROLLS-ROYCE(劳斯莱斯)和JAGUAR(美洲豹)等都采用了CAN总线来实现汽车内部控制系统与各检测和执行机构间的数据通信。同时,由于CAN总线本身的特点,其应用范围目前已不再局限于汽车行业,而向自动控制、航空航天、航海、过程工业、机械工业、纺织机械、农用机械、机器人、数控机床、医疗器械及传感器等领域发展。CAN已经形成国际标准,并已被公认为几种最有前途的现场总线之一。其典型的应用协议有: SAE J1939/ISO11783、CANOpen、CANaerospace、DeviceNet、NMEA 2000等。

1 . 什么是CAN总线?

CAN意为Controller Area Network的缩写,意为控制区域网络。是国际上流行的现场总线中的一种。是一种特别适合于组建互连的设备网络系统或子系统。

2.CAN总线特点?

CAN是到目前为止为数不多的有国际标准的现场总线

CAN通讯距离最大是10公里(设速率为5Kbps),或最大通信速率为1Mbps(设通信距离为40米)。

CAN总线上的节点数可达110个。通信介质可在双绞线,同轴电缆,光纤中选择。

CAN采用非破坏性的总线仲裁技术,当多个节点同时发送数据时,优先级低的节点会主动退出发送,高优先级的节点可继续发送,节省总线仲裁时间。

CAN是多主方式工作,网上的任一节点均可在任意时刻主动地向网络上其他节点发送信息。

CAN采用报文识别符识别网络上的节点,从而把节点分成不同的优先级,高优先级的节点享有传送报文的优先权。

报文是短帧结构,短的传送时间使其受干扰概率低,CAN有很好的效验机制,这些都保证了CAN通信的可靠性。

3.CAN总线应用领域

CAN总线最初是德国BOSCH为汽车行业的监测,控制而设计的。现已应用到铁路、交通、国防、工程、工业机械、纺织、农用机械、数控、医疗器械机器人、楼宇、安防等方面。

三、I2C(Inter-Integrated Circuit)总线

I2C(Inter-Integrated Circuit)总线是一种由PHILIPS公司开发的两线式串行总线,用于连接微控制器及其外围设备。I2C总线产生于在80年代,最初为音频和视频设备开发,如今主要在服务器管理中使用,其中包括单个组件状态的通信。例如管理员可对各个组件进行查询,以管理系统的配置或掌握组件的功能状态,如电源和系统风扇。可随时监控内存、硬盘、网络、系统温度等多个参数,增加了系统的安全性,方便了管理。

1、I2C总线特点

I2C总线最主要的优点是其简单性和有效性。由于接口直接在组件之上,因此I2C总线占用的空间非常小,减少了电路板的空间和芯片管脚的数量,降低了互联成本。总线的长度可高达25英尺,并且能够以10Kbps的最大传输速率支持40个组件。I2C总线的另一个优点是,它支持多主控(multimastering), 其中任何能够进行发送和接收的设备都可以成为主总线。一个主控能够控制信号的传输和时钟频率。当然,在任何时间点上只能有一个主控。

2、I2C总线工作原理

2.1、总线的构成及信号类型

I2C总线是由数据线SDA和时钟SCL构成的串行总线,可发送和接收数据。在CPU与被控IC之间、IC与IC之间进行双向传送,最高传送速率100kbps。各种被控制电路均并联在这条总线上,但就像电话机一样只有拨通各自的号码才能工作,所以每个电路和模块都有唯一的地址,在信息的传输过程中,I2C总线上并接的每一模块电路既是主控器(或被控器),又是发送器(或接收器),这取决于它所要完成的功能。CPU发出的控制信号分为地址码和控制量两部分,地址码用来选址,即接通需要控制的电路,确定控制的种类;控制量决定该调整的类别(如对比度、亮度等)及需要调整的量。这样,各控制电路虽然挂在同一条总线上,却彼此独立,互不相关。

I2C总线在传送数据过程中共有三种类型信号, 它们分别是:开始信号、结束信号和应答信号。

开始信号:SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据。

结束信号:SCL为低电平时,SDA由低电平向高电平跳变,结束传送数据。

应答信号:接收数据的IC在接收到8bit数据后,向发送数据的IC发出特定的低电平脉冲,表示已收到数据。CPU向受控单元发出一个信号后,等待受控单元发出一个应答信号,CPU接收到应答信号后,根据实际情况作出是否继续传递信号的判断。若未收到应答信号,由判断为受控单元出现故障。

目前有很多半导体集成电路上都集成了I2C接口。带有I2C接口的单片机有:CYGNAL的 C8051F0XX系列,PHILIPSP87LPC7XX系列,MICROCHIP的PIC16C6XX系列等。很多外围器件如存储器、监控芯片等也提供I2C接口。

3、总线基本操作

I2C规程运用主/从双向通讯。器件发送数据到总线上,则定义为发送器,器件接收数据则定义为接收器。主器件和从器件都可以工作于接收和发送状态。 总线必须由主器件(通常为微控制器)控制,主器件产生串行时钟(SCL)控制总线的传输方向,并产生起始和停止条件。SDA线上的数据状态仅在SCL为低电平的期间才能改变,SCL为高电平的期间,SDA状态的改变被用来表示起始和停止条件。

3.1、控制字节

在起始条件之后,必须是器件的控制字节,其中高四位为器件类型识别符(不同的芯片类型有不同的定义,EEPROM一般应为1010),接着三位为片选,最后一位为读写位,当为1时为读操作,为0时为写操作。

3.2、写操作

写操作分为字节写和页面写两种操作,对于页面写根据芯片的一次装载的字节不同有所不同。

3.3、读操作

读操作有三种基本操作:当前地址读、随机读和顺序读。图4给出的是顺序读的时序图。应当注意的是:最后一个读操作的第9个时钟周期不是“不关心”。为了结束读操作,主机必须在第9个周期间发出停止条件或者在第9个时钟周期内保持SDA为高电平、然后发出停止条件。

在I2C总线的应用中应注意的事项总结为以下几点 :

1)、严格按照时序图的要求进行操作,

2)、若与口线上带内部上拉电阻的单片机接口连接,可以不外加上拉电阻。

3)、程序中为配合相应的传输速率,在对口线操作的指令后可用NOP指令加一定的延时。

4)、为了减少意外的干扰信号将EEPROM内的数据改写可用外部写保护引脚(如果有),或者在EEPROM内部没有用的空间写入标志字,每次上电时或复位时做一次检测,判断EEPROM是否被意外改写。

添加:I2C 总线

在现代电子系统中,有为数众多的IC 需要进行相互之间以及与外界的通信。为了提供硬件的效率和简化电路的设计,PHILIPS 开发了一种用于内部IC 控制的简单的双向两线串行总线I2C(inter IC 总线)。I2C 总线支持任何一种IC 制造工艺,并且PHILIPS 和其他厂商提供了种类非常丰富的I2C 兼容芯片。作为一个专利的控制总线,I2C 已经成为世界性的工业标准。

每个I2C 器件都有一个唯一的地址,而且可以是单接收的器件(例如:LCD 驱动器)或者可以接收也可以发送的器件(例如:存储器)。发送器或接收器可以在主模式或从模式下操作,这取决于芯片是否必须启动数据的传输还是仅仅被寻址。I2C 是一个多主总线,即它可以由多个连接的器件控制。

早期的I2C 总线数据传输速率最高为100Kbits/s,采用7 位寻址。但是由于数据传输速率和应用功能的迅速增加,I2C 总线也增强为快速模式(400Kbits/s)和10位寻址以满足更高速度和更大寻址空间的需求。

I2C 总线始终和先进技术保持同步,但仍然保持其向下兼容性。并且最近还增加了高速模式,其速度可达3.4Mbits/s。它使得I2C 总线能够支持现有以及将来的高速串行传输应用,例如EEPROM 和Flash 存储器。

四、I2S总线

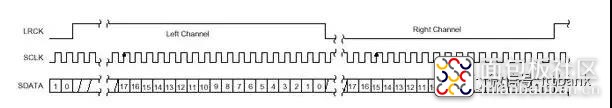

I2S有3个主要信号:

1、串行时钟SCLK,也叫位时钟(BCLK),即对应数字音频的每一位数据,SCLK都有1个脉冲。SCLK的频率=2×采样频率×采样位数

2、帧时钟LRCK,用于切换左右声道的数据。LRCK为“1”表示正在传输的是左声道的数据,为“0”则表示正在传输的是右声道的数据。LRCK的频率等于采样频率。

3、串行数据SDATA,就是用二进制补码表示的音频数据。I2S(Inter-IC Sound Bus)是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准。在飞利浦公司的I2S标准中,既规定了硬件接口规范,也规定了数字音频数据的格式。

I2S有3个主要信号:

1.串行时钟SCLK,也叫位时钟(BCLK),即对应数字音频的每一位数据,SCLK都有1个脉冲。SCLK的频率=2×采样频率×采样位数

2. 帧时钟LRCK,用于切换左右声道的数据。LRCK为“1”表示正在传输的是左声道的数据,为“0”则表示正在传输的是右声道的数据。LRCK的频率等于采样频率。3.串行数据SDATA,就是用二进制补码表示的音频数据。

有时为了使系统间能够更好地同步,还需要另外传输一个信号MCLK,称为主时钟,也叫系统时钟(Sys Clock),是采样频率的256倍或384倍。一个典型的I2S信号见图3。(图3 I2S信号)图3

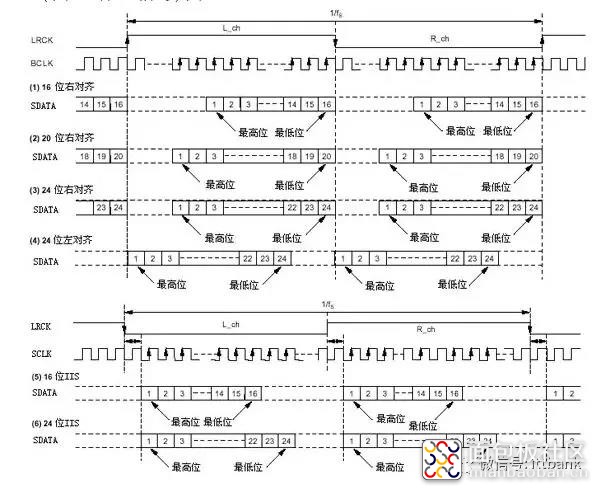

I2S格式的信号无论有多少位有效数据,数据的最高位总是出现在LRCK变化(也就是一帧开始)后的第2个SCLK脉冲处。这就使得接收端与发送端的有效位数可以不同。如果接收端能处理的有效位数少于发送端,可以放弃数据帧中多余的低位数据;如果接收端能处理的有效位数多于发送端,可以自行补足剩余的位。这种同步机制使得数字音频设备的互连更加方便,而且不会造成数据错位。

随着技术的发展,在统一的 I2S接口下,出现了多种不同的数据格式。根据SDATA数据相对于LRCK和SCLK的位置不同,分为左对齐(较少使用)、I2S格式(即飞利浦规定的格式)和右对齐(也叫日本格式、普通格式)。这些不同的格式见图4和图5。(图4 几种非I2S格式)图4(图5 几种I2S格式)图5

为了保证数字音频信号的正确传输,发送端和接收端应该采用相同的数据格式和长度。当然,对I2S格式来说数据长度可以不同。

五、SSP 总线

SSP 总线兼容SPI,SSI 和Microwire 总线的接口。

/4

/4

文章评论(0条评论)

登录后参与讨论