2. 测试执行:执行上一个阶段中定义的测试用例

3. 问题报告:检查和报告在测试执行期间检测到的所有问题

可以使用问题电子表格来记录在测试阶段检测到的每个问题。每当注册新问题时,都会向开发团队报告,并且能够追踪哪些问题已解决,哪些问题仍有待审查。

4. 测试结束:确定测试阶段何时完成,并创建测试结果文档,其中将包含成功执行的测试的摘要以及有关测试的更多相关信息。

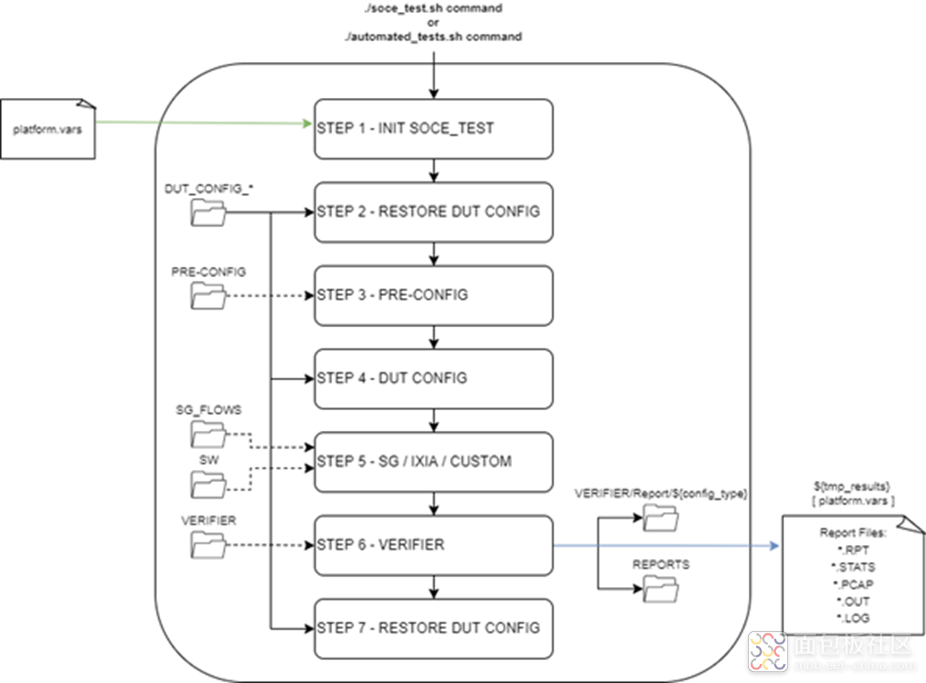

为了优化测试执行过程,我们使用了虹科SoC-e测试工具,以进行自动化测试。该工具考虑了以下内容:

l DUT配置过程

l 流量注入和嗅探

l 记录从 DUT 返回的流量

l 验证保存的日志

l 将 DUT 设置为原始状态

该工具的第一步与DUT 配置的执行有关。这是通过名为 Platform.vars 的输入配置文件完成的。通过该文件,用户可以配置不同的参数,如 DUT SSH 参数、主机 PC 的 IP 地址或网络接口。

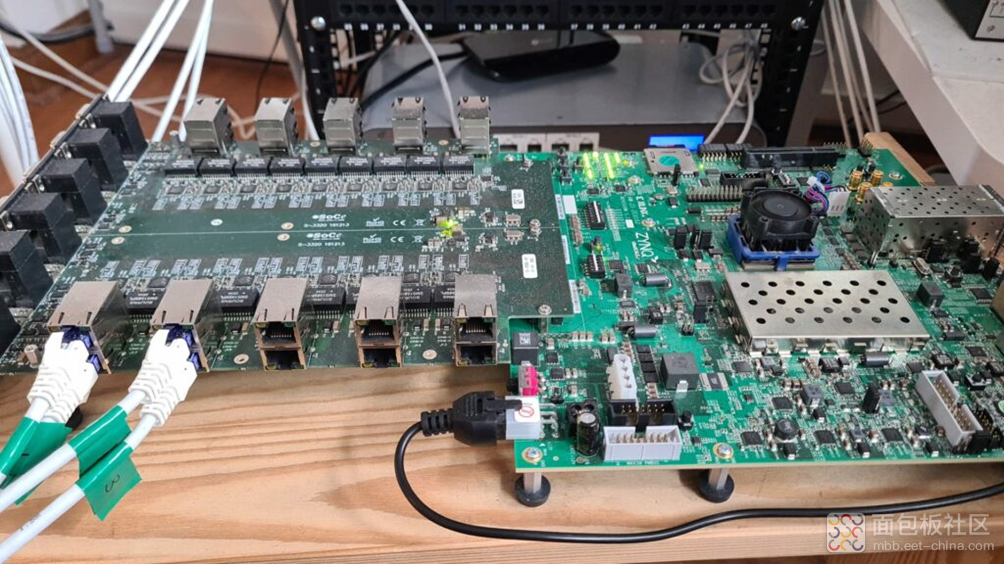

第二步,完成TS(测试站)和 DUT之间的流量注入和嗅探。我们有不同的第三方设备用作测试站,但最常用的设备之一是IXIA Novus One Plus。流量可以通过 IXIA 的 Python API 轻松发送。数据包操作是通过 Scapy Python 模块完成的。尽管 Scapy 允许传输该工具生成的所有流量,但它是使用不同的工具tcpreplay执行的。这使我们能够克服由 Scapy 引起的带宽和准确性方面的某些限制。在此步骤中,测试提供了自定义流量的灵活性,以验证不同的 DUT 功能。可扩展性不是问题,因为该工具支持添加额外的流量和测试端口。

第三步,该工具使用测试站或通过 Linux tcpdump 软件登记来自 DUT 的流量。

第四步,SoC-e 测试工具验证上一步中存储的信息(统计、寄存器转储(dump)等),以检查一切是否正常。通过这两个步骤,SoC-e 测试工具为测试用例的验证提供了一个很好的解决方案。

最后,第五步,也是最后一步。最后一步的主要目的是将 DUT 配置恢复到其原始状态,因为它可能在测试期间被修改。

作者: 虹科工业智能互联, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3988237.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/4

/4

文章评论(0条评论)

登录后参与讨论