百佳泰协助客户取证多年,常常遇到客户为了出货压力而跟时间赛跑,在检测结果显示不通过的原因往往是在产品设计、进料检验、制程初期就必须解决的难题,面对这样的困境不仅浪费时间也增加开发成本,若能在每个时期的产品质量做好严谨的把关,就可以减少许多出货前的烦恼。

谈到不良品分析之前,首先要了解到:整个产线在进行生产时会面临到的各个检验以及管控环节,在一个完整的品管流程中,基本上都会包含如下四个确认机制:

★本文重点:产品开发与进料、制程管控上应注意的事项,如能确实留意前中段的设计细节与料件特性、加工掌控,在出货时对于成品的把握度就会大幅提升。

Step 1.新产品开发在开发初期,工程师必须针对产品各零组件做审慎的测试与交叉比对,决定何种零组件是由自家制造亦或是透过外购方式取得,并确认料件的设计、组装及彼此间的匹配性,较常见的注意事项包含:

A.零组件的选用

在组装的部分除了注意Connector、Raw Cable、Paddle Card的特性质量、机构强度之外,也需要定义在加工区所披覆的胶水种类,包含胶水特性与量产时能符合加工便利性、含水量、固化时间等因素,都需要在产品设计初期就纳入考虑。

B.组件特性损耗余裕度

在裸线料件选用时必须替连接器及加工段预留损耗余裕度,以Type C Gen2的budgets为例,Host与 Device的容许损耗为8.5dB,成品线则为6dB @5GHz,此时若选择的裸线特性在5GHz时已超过5dB,那么加上连接器与加工造成的损失,就很有可能超出规范。

USB Type C to C Gen2 Loss Budget(资料源:USB IF)

USB Type C to C Gen2 Loss Budget(资料源:USB IF)

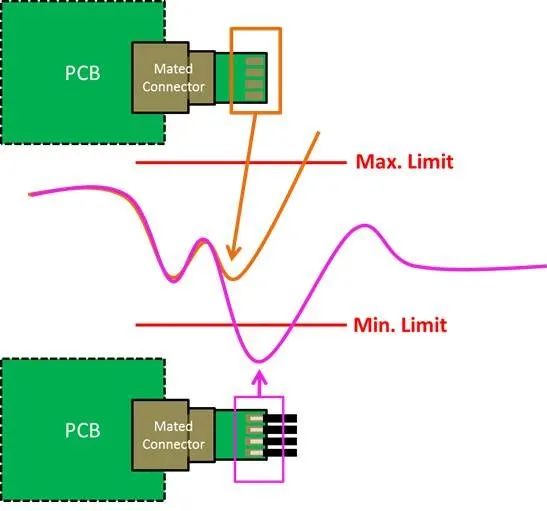

C.Paddle Card控制

PCB Layout厂在接到案件之后,照着规范设定的阻抗进行了Trace以及Pad的设计,线材商在设计完成后取得Paddle card并将裸线实际焊接、上胶,才发现原本设定好的特性阻抗因为加工后的电容效应往下掉,反而造成阻抗不连续面的增加(如下图所示),这代表制造商与Layout厂在发包时并没有讨论后续的加工以及对应的影响,而正确的作法是,先将特性阻抗在加工后会产生的差异估算进去,进行Layout时先提高特性阻抗的设计,使加工后的波形落入好球带。

Paddle Card焊接前后差异(资料源: Allion)

Paddle Card焊接前后差异(资料源: Allion)

D.制程设计

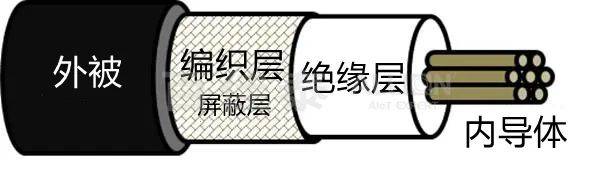

Coaxial Cable结构(资料源: Allion)

Coaxial Cable结构(资料源: Allion)

针对所有零组件进行验收是一件相当重要的事情,若是预计要进行量产的零组件结构、特性与预期规划不符时,趁着尚未制作之前必须要将问题抓出来,以免进入生产后造成的时间、成本损失,其中和特性较为相关的常见问题包含:

A.Raw Cable

(EX. 若屏蔽层、地线、线材排列组合有误可能造成串扰不良)

(EX.波形是否平滑且失真较小)

(若验收时衰减量大于评估值则可能造成最终成品线特性不良)

(若抽线时绝缘层包覆不均或线缆长度差异过大也有可能造成此项不良)

(EX.影响EMI特性)

B.Connector

(EX.端子偏移容易造成高频特性不良,尤其串扰)

(EX.毛边容易使损耗变大)

(EX.间距不符使的与Paddle Card对位困难)

C.Paddle Card

(EX. 特性阻抗于焊接后会变低,进而影响测试结果)

(EX. 不良的接地回路容易使串扰不良)

(过近时容易影响特性阻抗与串扰)

(EX. 尺寸不符会造成组装困难,进而影像高频特性)

Step 3.制程品质管控在确认一切就绪并进入生产流程时,必须要确保在整个生产流程中所有的制程皆如事前所规划并进行设备调适,因为各种设备的理想参数与现实状况中一定存在些微误差,倘若设备的参数与设置不协调,也可能造成最终成品特性不符预期,以下列出常见状况:

经过上述说明后,百家泰以实际测试时所遇到的几个常见不良案例与各位进行分享,在下述范例中皆简单说明该项目的Fail Item以及判断原因,并列出优化后的数据改善度:

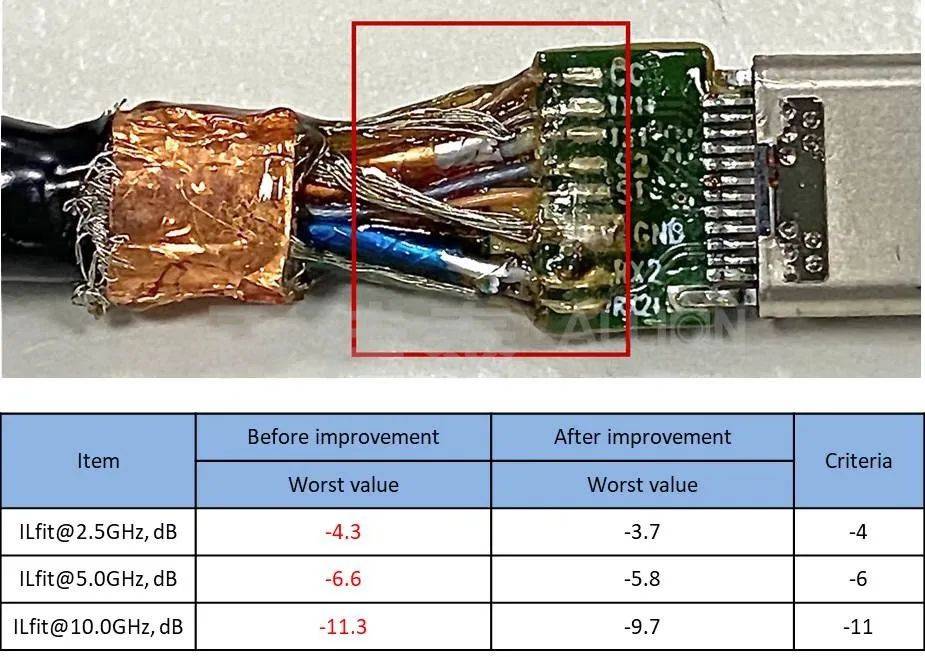

案例1 (资料源: Allion)

(资料源: Allion)

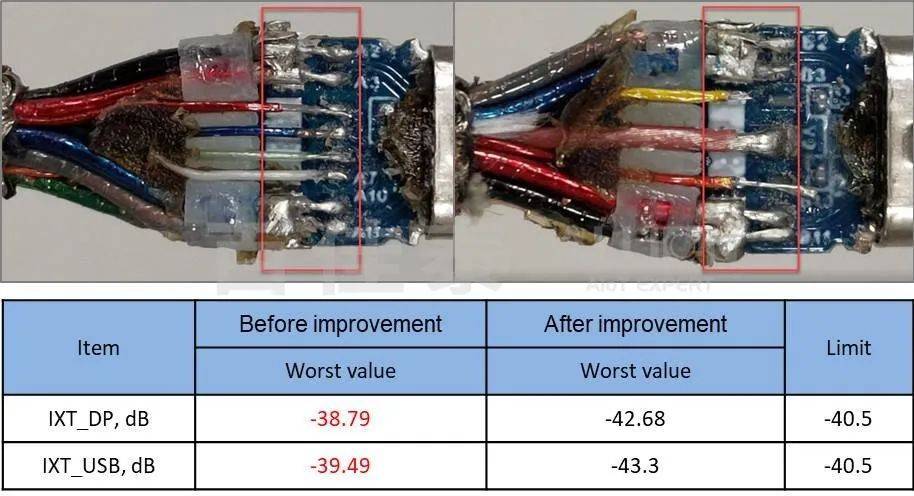

控制焊点的锡量与间距,避免距离过近而发生串音现象。

(资料源: Allion)

(资料源: Allion)

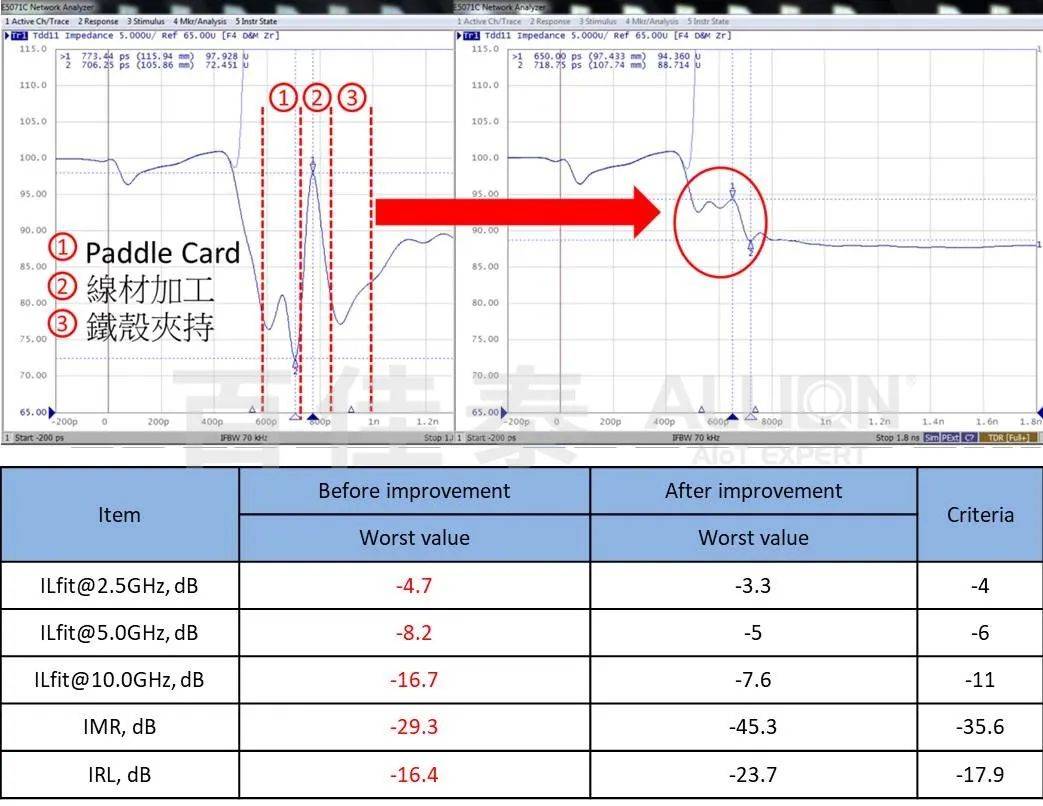

零组件与加工段阻抗不连续面过大且多,进而影响IL Fit、 IMR、IRL等项目不良。

(资料源: Allion)

(资料源: Allion)

高频量测不良的原因有很多可能性,即便是相同的项目都可能由不同的单一/复合因素导致,

作者: 百佳泰测试实验室, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-400317.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/4

/4

文章评论(0条评论)

登录后参与讨论