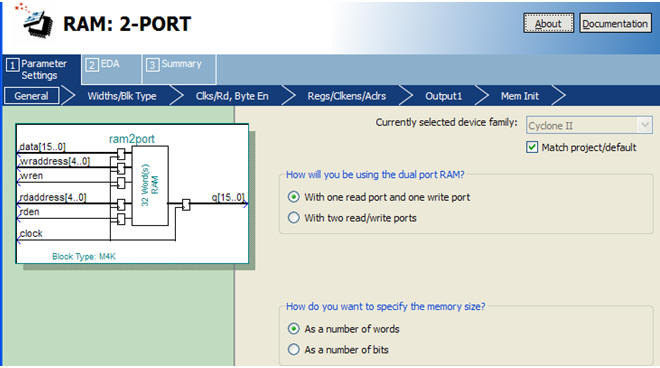

运用Quartus II软件的MegaWizard配置的双端口RAM如下:

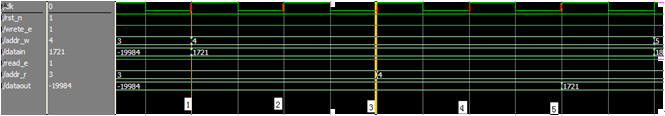

由于双端口RAM的数据输入和输出都用寄存器打了一拍,因此数据写入RAM中需要两个时钟周期,而数据读出需要三个是中周期。以下是仿真波形图:

在第1个时钟周期写入输入数据的地址和数据(地址为4,数据为1721),那么在第2个时钟周期数据1721才真正写入RAM中地址为4的单元中,那么在下一个时钟周期才可以读取地址4中的数据1721。在第3个发送读取地址信号,数据需要在第5个时钟周期才能输出地址4中的数据。

因此可以总结出:RAM的数据写入和读取只需要一个时钟周期,在实际应用的时候通常会用输入输出寄存器打一拍,相应的数据输入输出会滞后一个时钟周期。

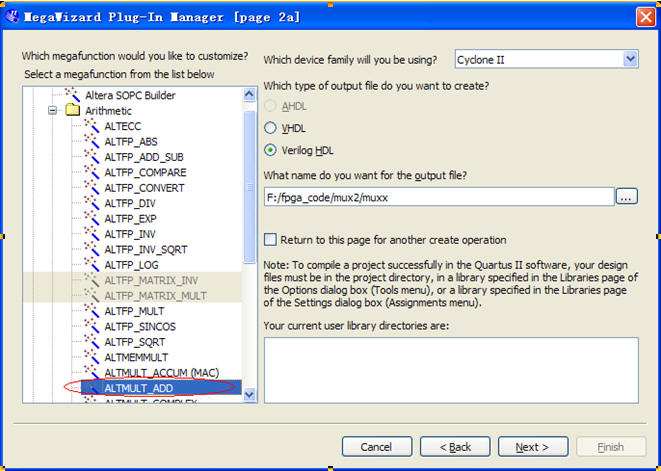

在Quartus II中配置乘法器如下所示:

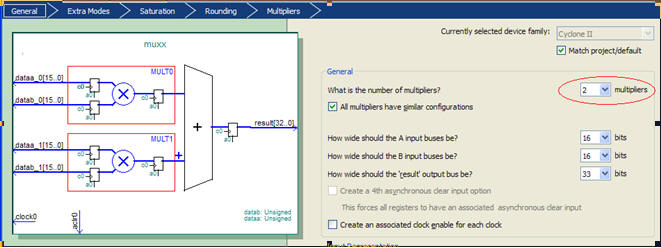

这里选择的是ADD,实际上点击Next就会出现下面对话框:

从上图可以看到,这里的加法器实际上先进行乘法运算,将乘法运算的结果相加。同时,可以选择乘法器的数量,最多可以选择4个。这里只分析乘法器,因此乘法器数量选择1。最后配置的乘法器如下图所示:

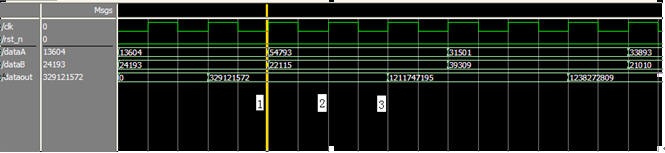

下面是仿真的波形图:

从上图可以看到,在第1个时钟沿输入待相乘的两个数据,在第2个时钟沿乘法器进行乘法运算,在第3个时钟周期可以读取计算结果。注意,乘法器的aclr0信号在为“0”时计算才有效。

/4

/4

文章评论(0条评论)

登录后参与讨论