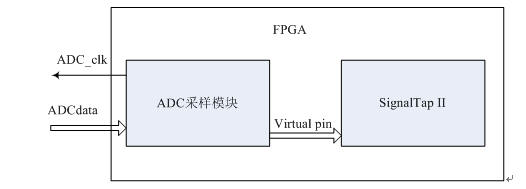

总体实现的功能框图如下图所示:

图中的clock信号和复位信号没有画出。这个设计很简单,作为初学者的我,主要是学习熟悉一下Signal Tap II 和virtual pin 的使用。对于初学者来说,很多时间都花在软件使用上,而且很多资料都只是理论性的给出软件的优点、参数,很少给出具体的用法,所以只能看很多资料然后摸索吧。

这里测试的ADC芯片为AD9820。代码如下:

module adc8test(clk,rst_n,adcin,adclk,adcout);

input clk;

input rst_n;

output adclk;

output [7:0] adcout;

input [7:0] adcin;

reg [7:0] adcin_r;

assign adclk = clk;

assign adcout = adcin_r;

always @(posedge clk or negedge rst_n) begin

if(!rst_n) adcin_r <= 8'd0;

else

adcin_r <= adcin;

end

endmodule

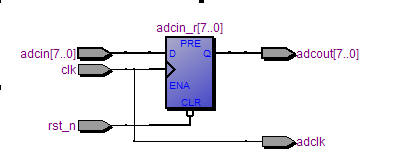

综合后的RTL视图如下所示:

ADC模块数据输出引脚不需要输出到FPGA外部,只需供Signal Tap II采样,因此可以设定为Virtual Pin。代码写好后先初始编译,然后再分配管脚和Virtual Pin。

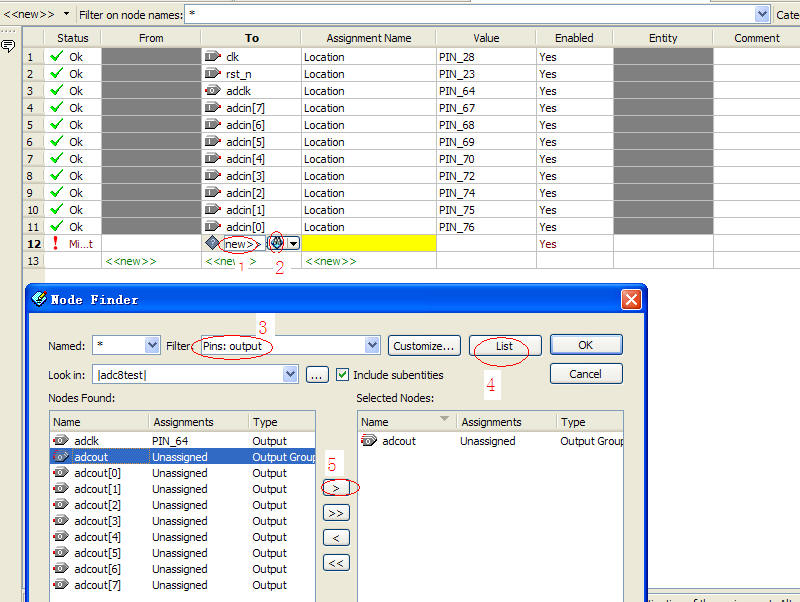

设定Virtual Pin:Virtual Pin的设置既可以采用输入TCL脚本的方式进行也可以在图形化界面操作,刚开始学习总是不太习惯TCL脚本,还是在图形化界面下操作吧。点击Assignment---->Assignment Edit,如下所示:

按照上图所示的操作步骤选择需要设定Virtual Pin的端口,然后点击OK,出现下面示意图:

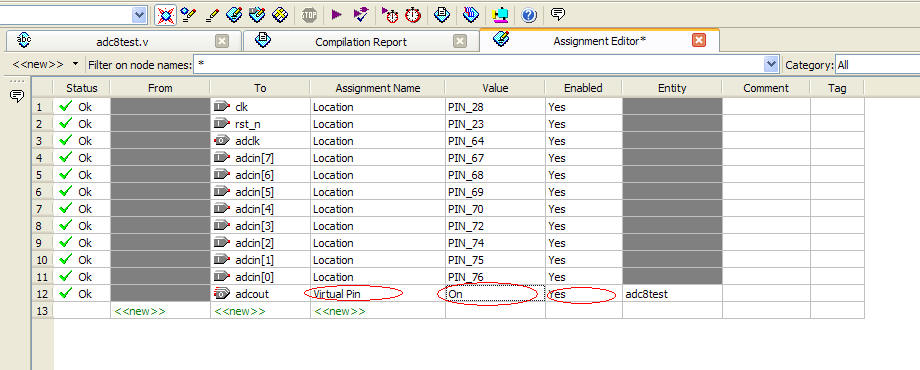

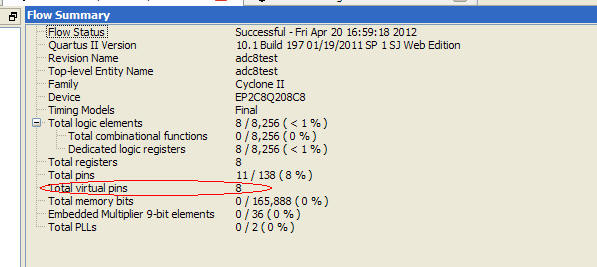

按照上图设定参数就OK了,然后点击保存从新编译。最后编译的结果如下图所示:

从编译结果中看到设定的Virtual Pin已经设置成功。

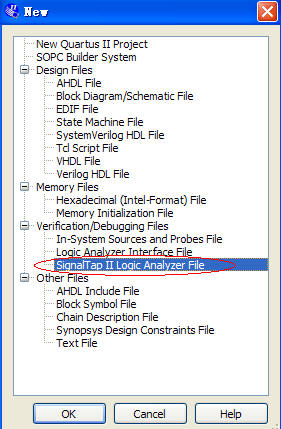

下面是设定Signal Tap II的过程:

点击File--->new,选择如下图所示的文件:

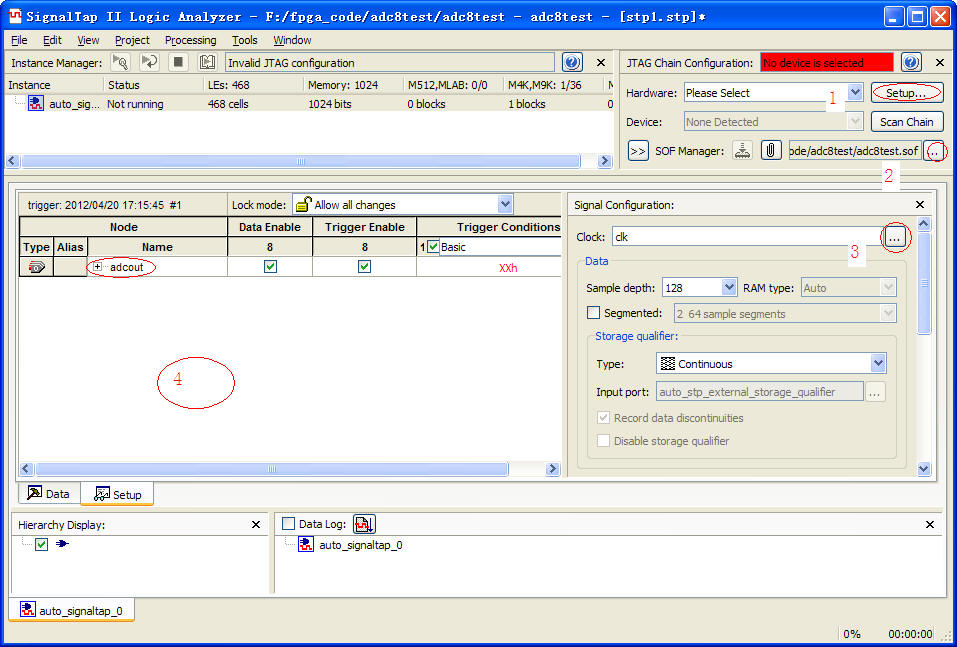

然后出现下面的设置界面:

按照图中的步骤设置即可,在步骤4中需要双击空白处选择需要采样的数据节点。这里需要选择刚刚设定的Virtual Pin;Clock的选择通常选择系统时钟;Trigger Conditions选择Basic。其它的配置选择默认就可以了,具体每个选项的意义,以后再讨论。

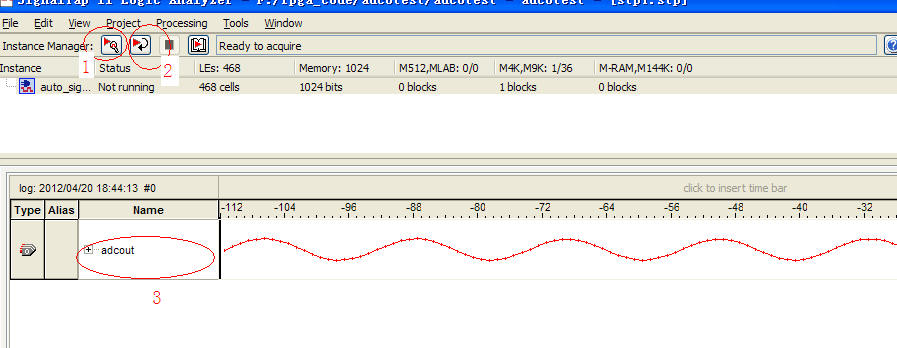

最后将代码下载到FPGA中,然后点击Tools--->Signal Tap II Logic Analyzer打开SignalTap II,出现下面的界面:

点击1或者2就可以采集到相应的数据,这里输入ADC的信号为1MHz的正弦信号,采样时钟为20MHz。在3处点击右键选择Bus Display Format选择显示数据的格式,这里选择的是Unsigned Line Char。

/4

/4

用户377235 2012-6-4 15:59

非常感谢,正用到这个,苦于无法解决。