才开始学习时序分析,头痛得紧啊,很多公式还是很不好理解,官方的数据手册给出了很多计算公式,初始看来不怎么好理解,还好官方给的培训视频中给出了些图示,这非常有助于时序分析各个公式的理解,现在分享下,呵呵!其实这些在官方给的培训视频中都可以找到。

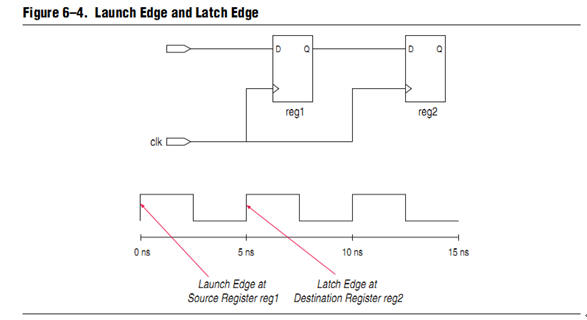

给出Launch Edge和Latch Edge的示意图:

在时序分析中有三种路径:Register to Register路径,Input Port to Internal Register和Internal Register to Output Port。

①、Register-to-Register路径。

在每一个路径中又分为Setup Time检查和Hold Time检查。

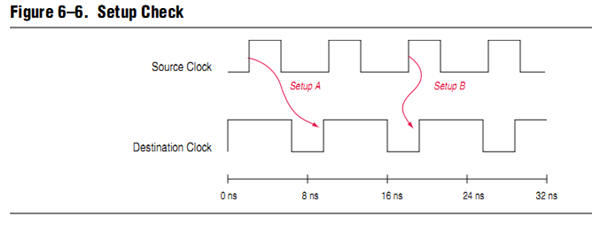

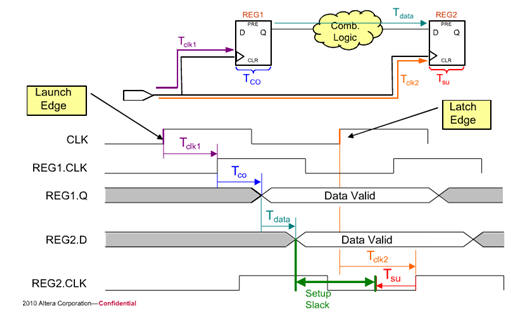

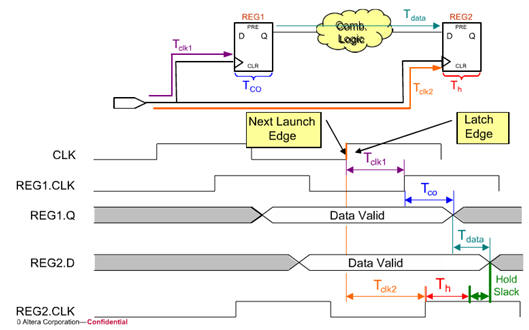

Setup时间检查是为了检查数据传输不能太慢,否则在目的寄存器的Latch Edge不能正确锁存数据。在每一个目的寄存器Latch Edge,TimeQuest analyzer采用与它最近的前一个时钟沿作为源寄存器的Launch Edge。如下图所示:

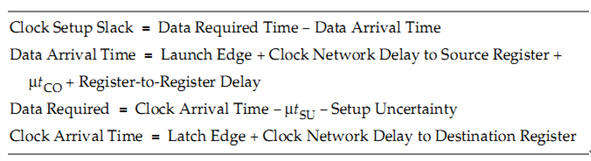

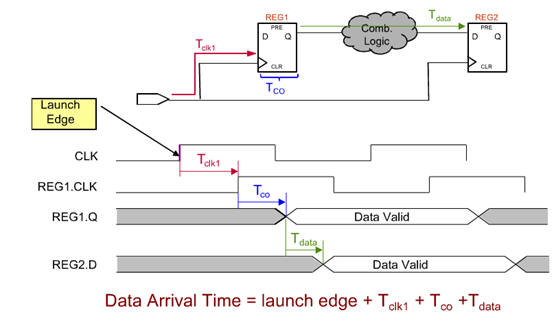

Slack的概念:由于setup时间检查的是数据传输不能太慢,那么数据传输的时间Data Arrival Time就必须在要求的时间Data Required Time内传输到目的寄存器。因此时间余量:slack=Data Required Time-Data Arrival Time。

在setup时间检查中有一下路径及其相关的slack时间计算。

在Quartus II的Handbook中并没有具体的给出示意图,理解起来可能比较麻烦,在官方给的培训视频中给出了示意图,这非常有助于理解。

Data Arrival Time的示意图如下所示

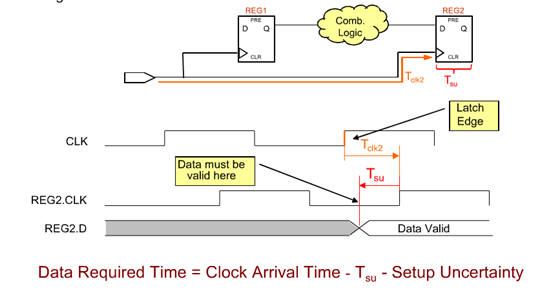

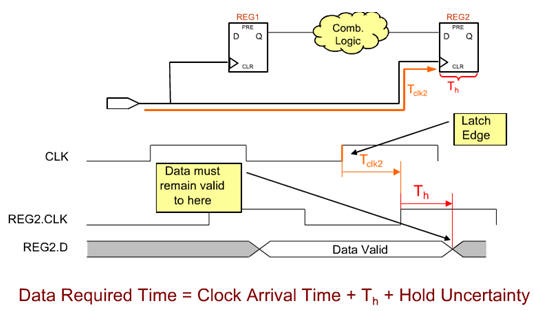

Data Required Time:

Setup slack:

通过上面给的示意图就可以很轻松的理解三个计算公式。

Hold Time时间检查,是为了检查数据传输不能太快,太快会影响前一次数据的锁存。Hole Time检查比较难理解,看了一些资料,到现在还没完全理解。下面只说说我的理解。

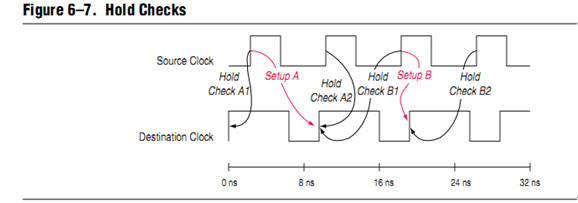

Hold Time检查建立在Setup Time检查的基础上,即每一个Setup Time 检查路径就有相应的Hold Time检查。但对每一个建立时间关系有两个保持时间检查。下图说明了建立时间检查的示意图。

在Quartus II的Handbook中有这么一段描述了建立时间检查。

The TimeQuest analyzer checks all adjacent clock edges from all setup relationships to determine the hold relationships. The TimeQuest analyzer performs two hold checks for each setup relationship. The first hold check determines that the data launched by the current launch edge is not captured by the previous latch edge. The second hold check determines that the data launched by the next launch edge is not captured by the current latch edge. From the possible hold relationships, the TimeQuest analyzer selects the hold relationship that is the most restrictive. The most restrictive hold relationship is the hold relationship with the smallest difference between the latch and launch edges and determines the minimum allowable delay for the register-to-register path.

这段话的大体意思是这样的,对于每一个建立时间关系TimeQuest analyzer进行两个保持时间检查,比如上图中的Setup A这个建立时间关系,就有Hold Check A1和Hold Check A2两个保持时间关系的检查; Setup B这个建立时间关系,就有Hold Check B1和Hold Check B2两个保持时间关系的检查。最后TimeQuest analyzer会选择一条最差的路径作为保持时间检查的路径。

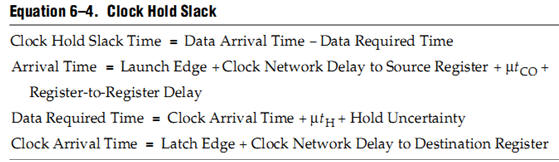

既然保持时间检查是检查数据传输不能太快,那么数据数据达到的时间就应该比数据要求到达的时间要长,因此有以下计算关系:

上式中Data Arrival Time和建立时间检查的Data Arrival Time计算公式相同,不同的是Data Required Time。

同理保持时间余量示意图为:

保持时间检查理解为数据变化不能太快更好理解些。从这个示意图可以看到,公式中的Data arrival Time的计算公式应该为:

Data arrival Time = Next Launch Edge + Clock Network Delay to Source Register + utco + Register to Register。

/4

/4

用户413283 2012-6-17 22:03