摘要:系统介绍EPP增强并口接口协议,简要介绍ST公司uPSD323X系列器件的特点及其开发环境PSDsoft EXPRESS;从硬件电路和软件编程两个方面,详细介绍使用uPSD323X系列器件实现EPP增强并口接口的设计方法。

关键词:EPP增强并口 uPSD323X PSDsoft EXPRESS

引言

在IBM公司推出PC机时,并行端口已经是PC机的一部分。并口设计之初,是为能代替速度较慢的串行端口驱动当时的高性能点阵式打印机。并口可以同时传输8位数据,而串口只能一位一位地传输,传输速度慢。随着技术的进步和对传输速度要求的提高,最初的标准并行端口即SPP模式的并行端口的速度已不能满足要求。1994年3月,IEEE 1284委员会颁布了IEEE 1284标准.IEEE 1284标准提供的在主机和外设之间的并口传输速度,相对于最初的并行端口快了50~100倍。IEEE 1284标准定义了5种数据传输模式,分别是兼容模式、半字节模式、字节模式、EPP模式和ECP模式。其中EPP模式、ECP模式为双向传输模式。EPP模式比ECP模式更简洁、灵活、可靠,在工业界得到了更多的实际应用。本文介绍的一种基于uPSD323X的EPP增强并口的设计核心是,使用uPSD323X内部的CPLD实现EPP接口。

1 EPP接口协议介绍

EPP(Enhanced Parallel Port,增强并行端口)协议最初是由Intel、Xirocm、Zenith三家公司联合提出的,于1994年在IEEE1284标准中发布。EPP协议有两个标准:EPP1.7和EPP1.9。EPP接口控制信号由硬件自动产品,整个数据传输可以在一个ISA I/O周期完成,通信速率能达到500KB/s~2MB/s。

EPP引脚定义如表1所列。

表1 EPP接口引脚定义

| 对应并口引脚 | EPP信号 | 方 向 | 说 明 |

| 1 | nWrit | 输出 | 指示主机是向外设写(低电平)还是从外设读(高电平) |

| 2~9 | Data0~7 | 输入/输出 | 双向数据总线 |

| 10 | Interrupt | 输入 | 下降沿向主机申请中断 |

| 11 | nWait | 输入 | 低电平表示外设准备好传输数据,高电平表示数据传输完成 |

| 12 | Spare | 输入 | 空余线 |

| 13 | Spare | 输入 | 空余线 |

| 14 | nDStrb | 输出 | 数据选通信号,低电平有效 |

| 15 | Spare | 输入 | 空余线 |

| 16 | Ninit | 输出 | 初始化信号,低电平有效 |

| 17 | nAStrb | 输出 | 地址数据选通信号,低电平有效 |

| 18~25 | Ground | GND | 地线 |

1.1 EPP接口时序

EPP协议定义了4种并口周期:数据写周期、数据读周期、地址写周期和地址读周期。数据周期用于计算机与外设间传送数据;地址周期用于传送地址、通道、命令、控制和状态等辅助信息。图1是EPP数据写的时序图。图1中,nIOW信号实际上在进行EPP数据写时并不会产生,只不过是表示所有的操作都发生在一个I/O周期内。在t1时刻,计算机检测nWait信号,如果nWait为低,表明外设已经准备好,可以启动一个EPP周期了。在t2时刻,计算机把nWrite信号置为低,表明是写周期,同时驱动数据线。在t3时刻,计算机把nDataStrobe信号置为低电平,表明是数据周期。当外设在检测到nDataStrobe为低后读取数据并做相应的数据处理,且在t4时刻把nWait置为高,表明已经读取数据,计算机可以结束该EPP周期。在t5和t6时刻,计算机把nDataStrobe和nWrite置为高。这样,一个完整的EPP数据写周期就完成了。如果就图1中的nDataStrobe信号换为nAddStrobe信号,就是EPP地址写周期。

图2是EPP地址读周期。与EPP写周期类似,不同的是nWtrite信号置为高,表明是读周期,并且数据线由外设驱动。

从EPP读、写周期可以看出,EPP模式的数据传输过程是一个信号互锁的过程。以EPP写周期为例子,当检测到nWait为低后,nDataStrobe控制信号就会变低,nWait状态信号会由于nDataStrobe控制信号的变低为而高。当计算机检测到

nWait状态信号变高后,nDataStrobe控制信号就会变高,一个完整的EPP写周期结束。因此,EPP数据的传输以接口最慢的设备来进行,可以是主机,也可以是外设。

1.2 EPP增强并口的定义

EPP增强并口模式使用与标准并口(SPP,Standard Paralled Port)模式相同的基地址,定义了8个I/O地址。基地址+0是SPP数据口,基地址+1是SPP状态口,基地址+2是SPP控制口。这3个口实际上就是SPP模式下的数据、状态和控制口,保证了EPP模式和SPP模式的软硬件兼容性。

基地址+3是EPP地址口。这个I/O口中写数据将产生一个连锁的EPP地址写周期,从这个I/O口中读数据将产生一个连锁的EPP地址读周期。在不同的EPP应用系统中,EPP地址口可以根据实际需要设计为设备选择、通道选择、控制寄存器、状态信息等。给EPP应用系统提供了极大的灵活性。

基地址+4是EPP数据口。向这个I/O口中写数据将产生一个连锁的EPP数据写周期,从这个I/O口读数据将产生一个连锁的EPP数据写周期。基地址+5~+7与基地址+4一起提供对EPP数据口的双字操作能力。EPP允许主机在此个时钟周期内写1个32位双字,EPP电路再把32位双字拆为个字节依次从EPP数据口中送出去。也可以用其所长6位字方式进行数据传送。

2 uPSD323X及其开发环境PSDsoft EXPRESS

ST公司的uPSD323X是带8032内核的Flash可编程系统器件,将于8032 MCU、地址锁存器、Flash、SRAM、PLD等集成在一个芯片内。其主要特点如下:具有在线编程能力和超强的保密功能;2片Flash保存器,1片是128K或者256K的主Flash存储器,另一片是32K的从Flash存储器;片内8K的SDRAM;可编程的地址解码电路(DPLD),使存储器地址可以映射到8032寻址范围内的任何空间;带有16位宏单元的3000门可编程逻辑电路(CPLD),可以实现EPP接口等及一些不太复杂的接口和控制功能;2个异步串口、I2C接口、USB接口、5通道脉冲宽度调节器、50个I/O引脚等。由于uPSD323X采用的是8032内核,因此可以完全得到Keil C51编程器的PSDsoft EXPRESS是ST公司针对PSD系列产品(包括uPSD)开发的基于Windows平台的一套软件开发环境。经过不断升级,目前最新版是PSDsoft EXPRESS 7.9。它提供非常容易的点击设计窗口环境用户不需要自己编程,也不需要了解HDL语言,只有点击鼠标即可完成对地址锁存器、Flash、可编程逻辑电路等外设的所有配置和写入。它支持所有PSD器件的开发,使用PSDsoft EXPRESS工具对uPSD323X系列器件的可编程逻辑电路的操作简单、直观。PSDsoft EXPRESS工具可以在ST网站(www.st.com/psd)免费下载。

3 用uPSD323X实现EPP接口设计

3.1 硬件接口

EPP增强并口的速度最高可达到500KB/s~2MB/s,这对外设的接口设计提供了一个很高的要求,如果外设响应太慢,系统的整体性能将大大下降。用户可编程逻辑器件,系统的整体性能将大大降低。用户可编程逻辑器件,如FPGA(Field Programmable Gates Array,现场可编程门阵列)和CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件),可以实现EPP增强并口的接口设计,这种实现方案可以达到并口中的速度极限,并且保密性好。ST公司的uPSD323X内部集成了可编程逻辑电路(CPLD),因此使用uPSD323X可以很好地实现EPP增强并口的接口设计。

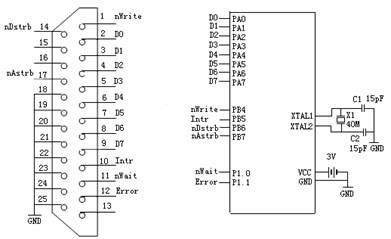

EPP接口(EPP1.7)外设硬件接口原理如图3所示。在本设计中,uPSD323X通过中断的方式接收PC机并口的数据,并且当外设准备好数据上传到PC机时,PC机采用的也是中断方式接收外设的数据。

在上述硬件电路的基于上实现EPP并口通信还需做两部分的工作:一部分工作是在PSDsoft EXPRESS工具中完成对CPLD 的数据的锁存;另一部分工作是在KEIL C51环境下编写中断服务程序,实现EPP数据的读取和发送。

在PSDsoft EXPRESS工具中,将PA端口(EPPD0~EPPD7)配置成带有时钟上升沿触发的寄存器类型(PT clocked register)的输入宏,PB0(nWait)配置成上升沿触发的D类型寄存器(D-type register)的输出宏,PB3(nWrite)、PB4(nDstrb)、PB2(nAstrb)配置成CPLD逻辑输入(logic input)口。NDstrb信号和nAstrb信号各自取反再相与后的值作为输入宏单元和输出宏单元的时钟。上述对PA、PB端口的配置用方程式表示如下:

PORTA EQUATIONS:

=======================

!EPPD7_LD_0=nAstrb & nDstrb;

EPPD0.LD=EPPD3_LD_0.FB;

!EPPD3_LD_0=nAstrb & nDstrb;

EPPD1.LD=EPPD3_LD_0.FB;

!nWait_C_0=nAstrb & nDstrb;

EPPD2.LD=EPPD3_LD_0.FB;

EPPD3.LD=EPPD3_LD_0.FB;

EPPD4.LD=FPPD7_LD_0.FB;

EPPD5.LD=EPPD7_LD_0.FB;

EPPD6.LD=EPPD7_LD_0.FB;

EPPD7.LD=EPPD7_LD_0.FB;

PORTB EQUATIONS:

=======================

nWait.D:=1;

nWait.PR=0;

nWait.C=nWait_C_0.FB;

nWait.OE=1;

nDstrb.LE=1;

nAstrb.LE=1;

EPP数据的锁存过程如下:以计算机向外设传输数据(即EPP数据写周期)为例子,计算机首先检测nWait信号,如果nWait为低计算机把nWrite信号置为低,表明是写周期,同时将数据放到数据总线上,然后置低nDstrb信号。此时,nDstrb信号会出现一个上升沿,此上升沿会将PA端口的数据锁存到输入宏;同时,此上升沿使nWait信号变高,表示外设正忙阻计算机发数年。当计算机检测到nWait信号为高后就会将数据握手信号nDstrb变高,EPP数据写周期结束。上述EPP数据的锁存和nWait握手信号的产生都由硬件产生,因此数据传输速度快。整个数据传输过程可以在一个I/O周期内完成,锁存到输入宏的数据的读取和nWait信号的清除则在外部中断0服务程序软件完成。

3.3 中断服务程序的功能描述及流程

由硬件原理图可以看出,EPP并口的nDstrb和nAstrb信号线分别连到uPSD323X的外部中断定和外部中断1引脚。当发生EPP数据读写时,nDstrb信号就会产生一个下降沿,引起外中断定中断。当发生EPP地址读写时,nAstrb信号就会产生一个下降沿,引起外中断1中断。外部中断0和外部中断1的中断服务程序的功能是相同的,只不过前者接收或发送的是数据而后者是地址、命令等。以外部中断0的中断服务程序为例,详细介绍数据正向传输(计算机向外设发送数据)和反向传输(外设向计算机传送数据)时中断服务程序的功能。外部中断0中断服务程序流程如图4所示。

(1)数据正向传输

当发生EPP数据写周期时,即数据正向传输时,计算机首先检测nWait信号。如果nWait为低,表示外设已准备好接收数据。计算机把nWrite信号置为低,表明是写周期,同时将数据放到数据总线上,然后置低nDstrb。NDstrb信号就会产生一个下降沿,此下降沿一方面将PA端口的数据锁存到输入宏并使nWait信号变高,表示外设正忙另一方面引起外部中断0中断,在外部中断0的中断服务程序中读取输入宏锁存的数据,然后将nWait信号清零通知计算机现在外设已经准备好可以再次接收数据了。

(2)数据反向传输

外设准备好数据需要上传到计算机时,uPSD323X就会将数据放到PA端口,同时置低Intr信号线,向计算机申请一个中断,计算机中由一个硬件驱动程序来处理并口的硬件中断。驱动程序在并口中断服务程序中,通过读取EPP数据口获得外设上传的数据。由于EPP接口的握手信号由硬件产生,当计算机读取EPP数据口时同样会检测nWait信号。如果nWait为低,计算机把nWrite信号置高,表明是读周期,然后置低nDstrb,nDstrb信号就会产生一个下降沿。此下降沿使nWait信号变高,同时引起uPSD323X外部中断定中断。在外部中断0的中断服务程序中,为确保计算机将PA端口的数据取走,需不断检测nDstrb是否为高。当nDstrb为高时,表示计算机已将PA端口听数据读走,然后中断服务程序将nWait置低,EPP数据读周期结束。

结语

本文系统地介绍了EPP增强并口协议,并给出使用ST公司的uPSD323X系列器件实现EPP增强并口的接口方法。此方案不需要外接门电路,保密性好,成本低。

/3

/3

文章评论(0条评论)

登录后参与讨论