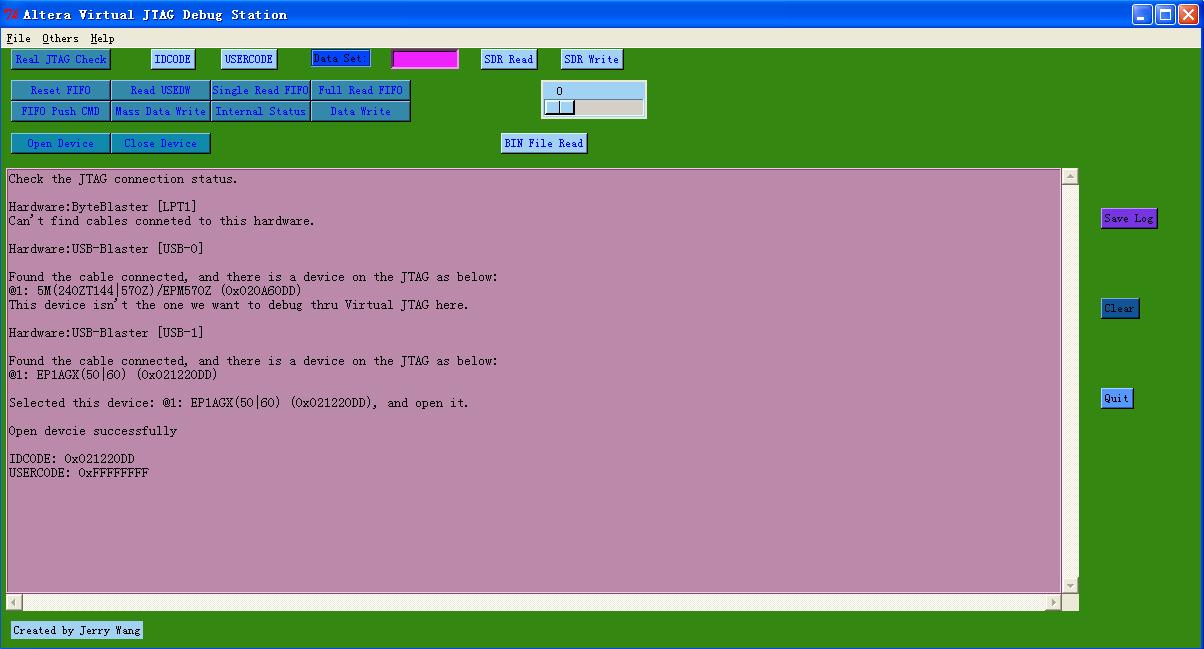

我们知道一个JTAG链通过菊花链的方式可以挂多个FPGA或者CPLD,同时同一台电脑上可以同时插有多种,或者一种多根电缆的情况。那么象这种情况,在Virtual JTAG调试的时候如何处理呢?由于以前没有这样玩过,这次在实验室为了调试方便,在一台电脑上插了3根电缆,其中一根Byteblaster两根USB Blaster电缆,我们来看看Virtual JTAG测试平台是如何识别的吧

从上图我们发现,平台还是能够识别出这三根电缆的,那么到底具体是如何做的呢,其实就是下面这句话即可

foreach hardware_name [get_hardware_names]

foreach语句会遍历找到所有插在本电脑的电缆。

同时我们发现,这三根电缆那些电缆连有器件或者没有,且能识别分别连的是什么器件。这里有个问题是,电缆[usb-1]多连的JTAG上有2片FPGA,这里只列出了一个器件。这是因为当时写TCL程序的时候遍历了电缆,而每根电缆上多连的器件没有遍历,所以默认找到的是器件1.我们同样可以使用foreach去遍历每根电缆上所有器件。

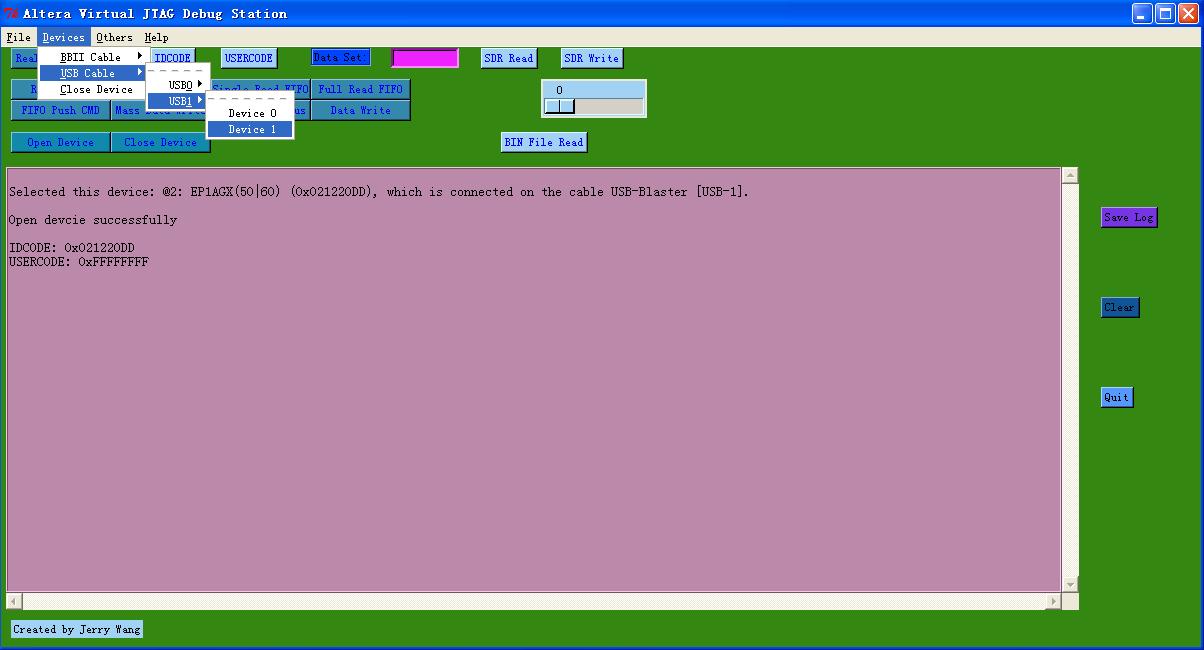

为了调试方便,把Virtual JTAG平台稍做修改,由于Virtual JTAG每次只能打开一个”device“,那么就设计一个菜单可以选择当前打开的是哪个电缆上的哪一个器件,如下图所示

coyoo 2014-4-9 12:11

用户1739054 2014-4-9 11:40

coyoo 2014-4-9 11:08

用户1739054 2014-4-9 10:30

用户1739054 2014-4-9 10:06

coyoo 2014-3-27 11:59

用户1739054 2014-3-27 11:54

coyoo 2014-3-27 11:01

用户1739054 2014-3-27 10:55

coyoo 2014-3-26 14:36