基于FPGA的TDC那些事之设计资源LAB

王敏志

概述

详细了解ALTERA FPGA的LAB结构,在着重详细了解StratixII之后高端器件LAB的基础上比较ALTERA各个系列器件LAB的异同。展示了可以利用ALTERA LAB哪些特性来进行TDC设计。

LAB

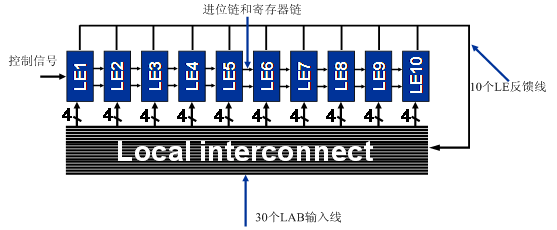

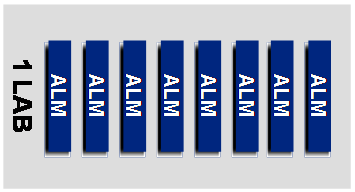

LAB即Logic Array Blocks,由数个LE、LE进位链、LAB控制信号、寄存器链以及本地互连信号等组成。ALTERA最早的FPGA是由10个LE组合成一个LAB,比如Cyclone。从CycloneII开始,16个LE组成一个LAB,高端器件从StratixII开始最小逻辑单元不叫LE而叫ALM,8个ALM组成一个LAB。图1是10个LE组成的LAB,CycloneII等由16LE组成的LAB和图1所示的结构一样,只是本地互连线以及反馈连线的数量有区别而已,而StratixII及之后的高端器件的LAB结构示意图如图2所示。

图1:10个LE组成一个LAB

图2:由8个ALM组成一个LAB

ALM和LE

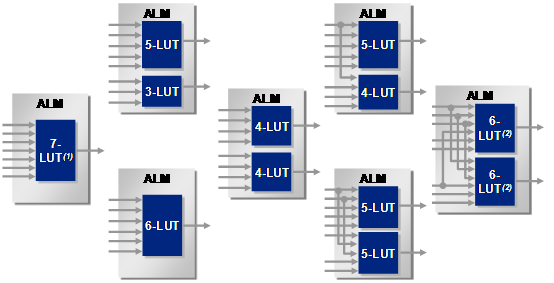

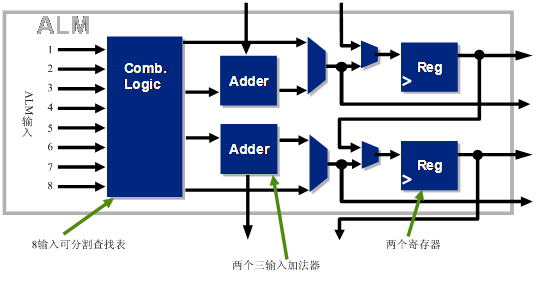

ALM即Adaptive Logic Module的缩写,我们知道一个LE就是一个4输入查找表和一个寄存器组成,而一个ALM可以如图3所示,进行功能自适应,其中图中间的4输入功能后向兼容LE(一个ALM等同2个LE)。

图3:8输入ALM的可分割且自适应结构

图3这种自适应功能在TDC设计中不是我们关注的焦点,反而由于这样自适应的存在,增加了FPGA编译器的灵活度,进而增加了TDC设计的难度(TDC设计的精髓就是simplicity和linearity)。TDC的关键部件是Delay-Line,利用LE来实现Delay Line要比用ALM实现Delay Line要方便得多。所以我们需要深入了解LE特别是ALM的内部结构,然后才能着手进行TDC的设计。

LE的操作模式只有普通模式(Normal)和算术模式(Arithmetic)两种,而ALM的操作模式有四种,分别是普通模式、扩展LUT模式、动态算术模式以及共享算术模式。目前还不清楚这些操作模式对TDC设计的影响,做到有个了解即可。

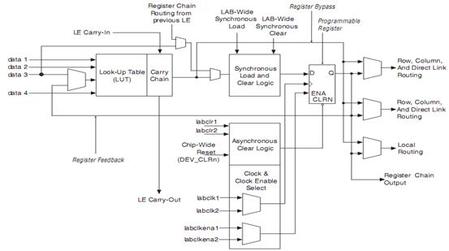

图4:LE的内部结构

图4展示的是LE的内部结构,需要关注的是LE内部没有如ALM里那样的专门加法器,如果要实现加法器,则是通过LUT完成。这里需要关注LE的一个特点是图中的四个data输入端口,LUT的这四个输入路径相对较简单,再加上4输入LUT功能简单,所以在实现TDC功能的时候也比较简单,基本无需人工干预。图5是在QuartusII里的ChipPlanner工具里观察一个LE的视图,进一步验证了LE简单的功能结构。

图5:在ChipPlanner里观察到的LE结构

图6是ALM的示意图,对比图6和图4、图5可以看到一个ALM除了相当于两个LE以外,中间还特别增加了两个专用加法器。

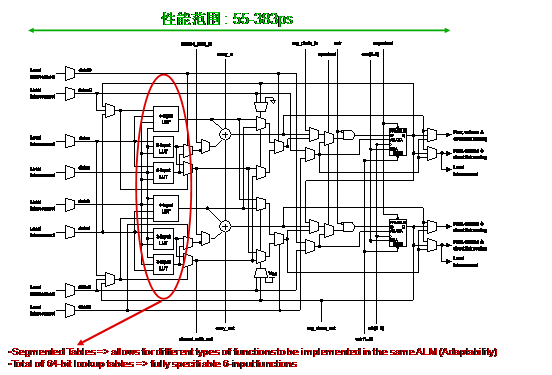

图6:ALM

图7是ALM的内部结构,图上方是ALTERA内部培训资料上给出的一个性能指标,这个55ps到383ps的指标对于TDC设计至关重要,资料中没有解释这个时间参数具体含义,而且ALTERA的公开资料上也很难查到类似这样的参数。我们可以想象一下假如用户要在FPGA内部实现一个Delay Line,其每个延时单元的延时时间如果是55ps,那么利用FPGA实现TDC是不是成为了可能了呢?事实上这确实是事实。已经有人在Cyclone系列FPGA上实现了精度达到10ps的TDC,本人也在高端器件ArriaGX上实现了相同的功能。所以回过头来理解这个55ps应该是Carry-in到Carry-out等进位链延时时间,而几百皮秒的时间应该是ALM输入到输出端口的延时时间。由于ALM有各种不同的输入及输出,所以这个时间参数才会有不同的数值,就算路径相同,那么如果位置不同,这个时间也应该有微小的差别。

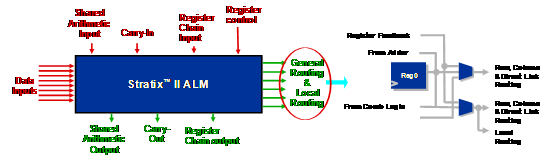

仔细观察图7,可以总结出ALM的输入包含了8个数据输入,1个进位链,一个共享算术输入,一个寄存器链输入以及寄存器控制信号;而ALM的输出则包含了图7最右方的两路数据输出,每路数据输出提供了3个驱动(一个信号只驱动通用路径,另一个信号可驱动通用和本地路径),每一个ALM最多可有4个逻辑输出(2个组合逻辑输出,2个寄存器输出),另外还有进位链输出,共享算术输出以及寄存器链输出。图8示意了图7中所有可能的输入和输出。

图7:ALM内部结构

图8:ALM的输入输出示意图

比较图7和图4,我们发现ALM的数据输入路径要比LE的数据输入路径要复杂一些,所以在进行TDC设计的时候经常需要进行部分人工干预,通常用户可以通过QuartusII软件里的ECO模块手动的修改某些路径以调整Delay Line的输入路径。这种手动干预,特别是在单FPGA多TDC通道的时候更加重要,否则的话各TDC通道之间“Skew”会非常大。

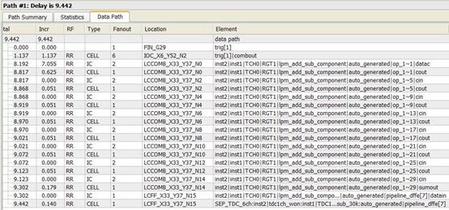

最后对于上述图7中的时间参数,利用ALTERA的TiemQuest工具可分析出这个时间,如图9所示。只不过这个时间的范围比图7所示的要大得多,根据数据路径不同会有不同,图9显示的最大延时时间是625ps,最小延时时间是51ps。图9的数据路径是从datac到ALM的输出,通过手动改变数据路径,比如将datac改为dataa或者datab,那么这个延时时间超过700ps,如果将datac改成dataf,那么这个延时时间大概是400多皮秒。图9中最小的延时时间是51ps,比较符合图7给出的时间参数。另外,需要说明的是,图7培训资料针对的是StratixII器件,而上述利用TimeQuest分析的是基于ArriaGX。根据ALTERA的信息,物理上这二者没有分别,因为这二者的DIE是一样的,只是有可能因为工具对二者处理的不同才导致这个参数的差别。

图9:ALM内部延时时间参数

结论

本文比较了低端器件的LE以及高端器件的ALM的异同,进而分析在不同器件上实现TDC功能时所需要注意的事项,尤其是需要进行manually modification。

coyoo 2016-2-25 10:36

用户1867027 2016-2-25 10:08

coyoo 2015-7-31 09:10

用户377235 2015-7-30 16:16

你好~ 如果一个进位链的延时是50ps,时钟频率是250Mhz的话 被测脉宽肯定小于一个时钟周期也就是小于4ns 但是这样也得需要80个进位链 一个slice一个进位链,这就需要80个slice 这种可行吗?

用户377235 2015-7-12 00:35

用户889149 2013-5-24 19:26

用户1587968 2013-2-22 20:04