看夏宇闻的第二版 《Verilog HDL 数字设计与综合》,学习verilog

下面为书中第7节的实例改编,书中的实例不可综合,更改后,ISE综合已OK,

开发板尚未拿到,只能软件仿真,呵呵,盼高手斧正。。。。

verilog 源码如下, 激励测试代码可以采用书上原有的,把时间参数修改下就OK了.

`define TRUE 1'b1

`define FALSE 1'b0

module TrafficCtrl(hwy, cntry, Xsig, clock, clear);

output [1:0] hwy;

output [1:0] cntry;

input Xsig; // if true, car in cntry; else no car .

input clock;

input clear;

// declare hwy, cntry are registers

reg [1:0] hwy, cntry;

// traffic light state

parameter RED = 2'd0,

YELLOW = 2'd1,

GREEN = 2'd2;

// state define //hwy cntry

parameter S0 = 3'd0, //GREEN RED

S1 = 3'd1, //YELLOW RED

S2 = 3'd2, //RED RED

S3 = 3'd3, //RED GREEN

S4 = 3'd4; //RED YELLOW

parameter DELAY0 = 4'd0,

DELAY1 = 4'd1,

DELAY2 = 4'd2,

DELAY3 = 4'd3,

DELAY4 = 4'd4,

DELAY5 = 4'd5,

DELAY6 = 4'd6;

// inner state variable

reg [2:0] state;

reg [2:0] next_state;

reg [3:0] stateChgDelay;

reg pllDiv2; //时钟分频---下载测试前根据时钟再考虑PLL分频

task TrafficClockDelay (

input clkDiv,

inout [3:0] delay);

begin if(clkDiv)

begin case(delay)

DELAY0: ;

DELAY1: delay = DELAY0;

DELAY2: delay = DELAY1;

DELAY3: delay = DELAY2;

DELAY4: delay = DELAY3;

DELAY5: delay = DELAY4;

DELAY6: delay = DELAY5;

default:delay = DELAY0;

endcase end end endtask always @(

posedge clock)

if (clear)

begin state = S0; // reset control state

pllDiv2 = 1'b0;

end else begin state = next_state;

pllDiv2 = ~pllDiv2;

end always @(state)

begin hwy = GREEN; // default value

cntry = RED;

case (state)

S0: ; // using default

S1: hwy = YELLOW;

S2: hwy = RED;

S3:

begin hwy = RED;

cntry = GREEN;

end S4:

begin hwy = RED;

cntry = YELLOW;

end default: ; endcase end always @(pllDiv2,state, Xsig)

begin TrafficClockDelay(pllDiv2,stateChgDelay);

case (state)

S0:

if(Xsig)

begin next_state = S1;

stateChgDelay = DELAY3; // yellow to red delay

end else next_state = S0;

S1:

begin if (DELAY0==stateChgDelay)

begin next_state = S2;

stateChgDelay = DELAY2; // red to green delay

end end S2:

begin if (DELAY0==stateChgDelay)

next_state = S3;

end S3:

if(Xsig)

next_state = S3;

else begin if (DELAY0==stateChgDelay)

begin next_state = S4;

stateChgDelay = DELAY3; // yellow to red delay

end end S4:

begin if (DELAY0==stateChgDelay)

next_state = S0;

end default: next_state = S0;

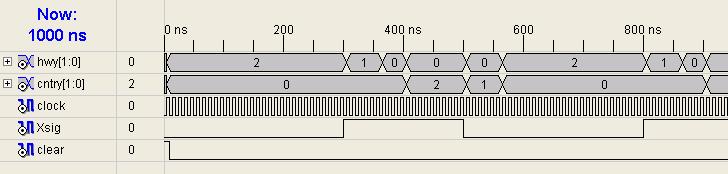

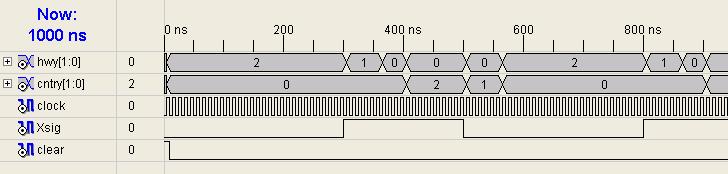

endcase endendmodule附软件仿真结果:

/4

/4

文章评论(0条评论)

登录后参与讨论