44. SI仿真时,提示can’t open xx/xx/xx/cycle.msm是怎么回事?

答:肯定是.brd文件的路径或文件名本身有空格。

45. SI仿真时,提示“part with invalid parameter values exist in the topology”怎么解决?

答:可能是TL的velocity参数没添加上。

46. Allegro布线时,等长走线很慢、很卡?

答:肯定是开了constraints manager,关掉即可。

47. Orcad使用层次原理图作图时,对于顶层原理图中的block跟其所对应的子原理图中port修改后如何快速同步?

答:当修改了原理图中的port时,回到顶层原理图,找到其所对应的block,右键选择synchronize up(向上同步),即可将port更新到block。Synchronize down则刚好相反。

48. Constraints Manager里等长布线时,Relative Propagation Delay里没有显示走线长度及误差信息?

答:可以试试打开Online DRC,并且Update DRC.

49. 如何查看Packetage使用了哪几个pad?

答:在allegro里找到Tools->Quick Reports->PadStack Usage Report,在里面搜索即可。

50. orcad/pspice安装报runtime error r6034错误或缺少.dll文件的解决方法

答: Microsoft Visual C++ Runtime library

Runtime Error!

Program :D:\Cadence\SPB_15.7\tools\capture\capture.exe

R6034

An application has made an attempt to load the C runtime library incorrectly.

Please ccontact the application's support team for more information!

解决方法:

1.在"我的电脑"上右键,选择属性,然后选择“高级”,再点击进入“环境变量”

2.在"系统变量"中找到"PATH"项,我的PATH键值如下:

原来的:

E:\MentorGraphics\9.3PADS\SDD_HOME\common\win32\bin;E:\MentorGraphics\9.3PADS\SDD_HOME\common\win32\lib;%SystemRoot%\system32;%SystemRoot%;%SystemRoot%\System32\Wbem;%QUARTUS_ROOTDIR%\bin;e:\MENTOR~1\LICENS~1;%MGC_HOME%/bin;%MGC_HOME%/lib;%MGC_HOMEBS%\bin;%MGC_HOMEBS%\lib;%CDSROOT%\tools\bin;%CDSROOT%\tools\libutil\bin;%CDSROOT%\tools\fet\bin;%CDSROOT%\tools\pcb\bin;%CDSROOT%\tools\specctra\bin;%CDSROOT%\tools\PSpice;%CDSROOT%\tools\PSpice\Library;%CDSROOT%\tools\Capture;%CDSROOT%\OpenAccess\bin\win32\opt

修改后的:

%CDSROOT%\tools\bin;%CDSROOT%\tools\libutil\bin;%CDSROOT%\tools\fet\bin;%CDSROOT%\tools\pcb\bin;%CDSROOT%\tools\specctra\bin;%CDSROOT%\tools\PSpice;%CDSROOT%\tools\PSpice\Library;%CDSROOT%\tools\Capture;%CDSROOT%\OpenAccess\bin\win32\opt;E:\MentorGraphics\9.3PADS\SDD_HOME\common\win32\bin;E:\MentorGraphics\9.3PADS\SDD_HOME\common\win32\lib;%SystemRoot%\system32;%SystemRoot%;%SystemRoot%\System32\Wbem;%QUARTUS_ROOTDIR%\bin;e:\MENTOR~1\LICENS~1;%MGC_HOME%/bin;%MGC_HOME%/lib;%MGC_HOMEBS%\bin;%MGC_HOMEBS%\lib

也就是把所有cadence的变量全部放到前面就行了。

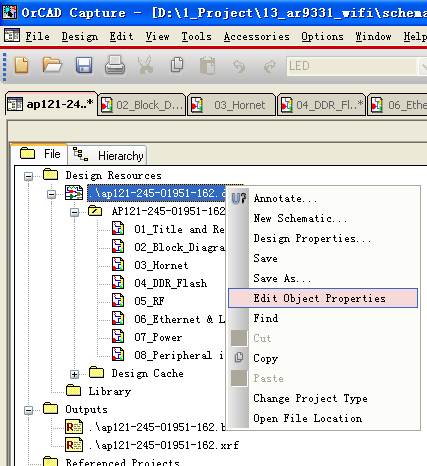

51. orCAD里面怎样批量修改器件的属性?

答:在project页面里选中”xxx.dsn”,右键选择Edit Object Properties,进去后再右键选择pivot可切换列表布局。

52. LP Wizard做PCB库的时候为什么做出来的库没有焊盘的?

答:肯定是没设置allegro里Pad的路径了,导致LP Wizard用skill调用allegro时找不到焊盘。

53. 做PCB库时,一般需要在哪些层做处理?

答:

无电气层外框 (Packetage Geometry->Place_Bound_Top)

器件高度 (Setup->Areas->Package Height)

装配层外框 (Packetage Geometry->Assembly_top)

元件丝印层外框 (Packetage Geometry->Silkscreen_top)

参考编号在丝印层(Ref Des->Silkscreen_top)和装配层(Ref Des->Assembly_top)

元器件类型 (Device Type->Assembly_Top)可选

54. 做PCB库时,如果修改了焊盘,那怎样将封装库里焊盘更新到最新状态?

答:打开.dra,Tools->Padstack->Refresh即可。

55. 快速切换act层跟alt层?

答:在env里设置快捷键添加以下文本即可用F2键快速切换了。

alias F2 pop swap

56. 用Allegro SI仿真的时候,DDR3跑的是800MHz,所以我CLK设的是400MHz,您所在Stimulus Edit中的Switch At选BOTH,这样跑出来的才是正确的。打开switch at的方法是:在Stimulus State栏中选Custom选项,Stimulus Type里面选择SYNC,在下面的Stimulus Editing栏就可以看到Switch At选项。

57. 当使用层次式设计时,导出物料清单要选中use occurrences(preferred) ,而不是use instances(使用当前属性)。否则可能出现器件编号不对的状况。

58. 当back annotation反标失败的时候,可再重新对整个design来一次annotation,甚至是先复位所有编号,再无条件编号,平铺式选instances跟occurrences没关系,层次式必须选择occurrences。然后brd导出logic,orcad再反标一次即可。

59. 铺静态铜完成后最好fix下,否则split planes时可能会导致之前的覆铜丢失。

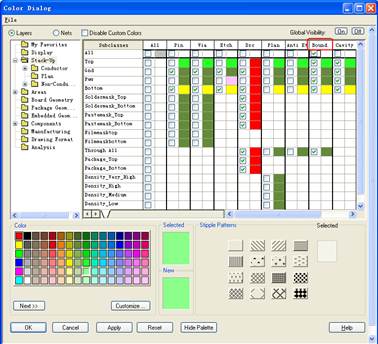

60. Allegro老是提示dynamic shapes里有out of date shapes怎么办?

答:肯定是用画anti etch线的方法分割电源层,但分割得太碎,导致一些外面的dummy net的shapes被自动删掉而留下一些boundaries,没分割一次,boundary就增多,所以可以看到out of date shapes会增多。这时单纯删除shape是不行的,要在color/visibility里将bound.这一栏显示才行。

61. 不小心将所有覆铜删掉后,导致之前打的接到低上的过孔全都变成dummy net了,有没有办法可以批量修改这些过孔的网络接到地呢?

答:

a) 先铺上GND属性的dynamic copper;

b) 选中所有过孔,然后移动到板外面,不要选中rip up,最好用ix 命令,方便待会儿移回到原来的位置;

c) 然后再用ix命令移回到原来的位置,此时刚才的无网络连接属性的过孔将会自动打上网络属性。

/4

/4

用户1161977 2013-12-12 11:38

用户377235 2013-11-25 22:32

用户315552 2013-8-3 01:44

用户403664 2013-7-22 11:12