首先,我将用一个简单的例子来说明一下,“低级建模”的最基本思路:

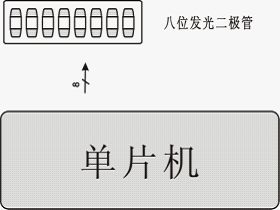

(一)利用C语言驱动八位发光二极管:

(如果我说C语言和单片机是形影不离的哈,估计没有人会反对吧?)

我们以流水灯作为例子,因为它是最经典的实验。假设我要实现流水灯效果,那么我只要建立一个简单的“流水灯函数”函数,“Flashing”。

void Flashing(){ ...... }

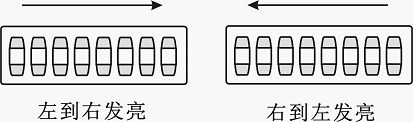

如果要实现自左向右或者自右向左发光的流水灯,可以使用C语言创建两个简单的函数,“Flashing_To_Right”和“Flashing_To_Left”。

void Flashing_To_Right() { ...... }

void Flashing_To_Left() { ...... }

假设我要实现流水灯效果:

1. 永远自右向左发亮。

2. 永远自左向右发亮。

3. 流水灯永远跑来跑去。

那么可以这样写:

while( 1 ) { Flashing_To_Left(); } //1

while( 1 ) { Flashing_To_Left(); } //2

while( 1 ) { Flashing_To_Left(); Flashing_To_Right(); } //3

对于C语言来说,这些任务都非常的简单。几乎是入门级的实验,但是将这些实验带入到V语言的环境下。确实一个记得思考的问题。

(二)利用V语言驱动八位发光二极管:

我们先看一段非常傻瓜的一段代码:

module Flashing ( CLK, RSTn, Data_Out );

input CLK, RSTn;

output [7:0]Data_Out;

reg [7:0]Counter;

always @ ( posedge CLK or negedge RSTn )

if( !RSTn )

Counter <= 8'd0;

else if( Counter == 200 )

Counter <= 8'd0;

else

Counter <= Counter + 1'b1;

reg [7:0]i;

always @ ( posedge CLK or negedge RSTn )

if( !RSTn )

i <= 8'd0;

else if( Counter == 200 )

i <= i + 1'b1;

else if( i == 8 )

i <= 8'd0

reg [7:0]rData;

always @ ( posedge CLK or negedge RSTn )

if( !RSTn )

rData <= 8'b0000_0001;

else if( i < 8 )

rData <= { rData[6:0], 1'b0 };

else if( i == 8 )

rData <= 8'b0000_0001;

assign Data_Out = rData;

endmodule

没错,上面是实现流水灯的代码。如果我说我要求:“ 自左向右循环3次,自右向左循环5次,然后自左向右一次,自右向左一次,然后自左向右循环30次 ”。当你听到这样的要求,你可能会崩溃.... 如果按照上面的写法,你会写得很长很长。

相比之下,C语言要实现以上的要求,根本就是“小儿科”的功夫。

int i;

for( i = 0; i < 3; i++ ) Flashing_To_Right();

for( i = 0; i < 3; i++ ) Flashing_To_Left();

Flashing_To_Right();

Flashing_To_Left();

for( i = 0; i < 30; i++ ) Flashing_To_Right();

给自己5分钟的思考,想想我到底要表达什么?

在C语言上,有“顺序操作”或者“泛型编程”的概念。从上述的代码中,for循环利用i变量,控制循环次数,然后调用3次“Flashing_To_Right()”函数。相反的V语言是“并行操作”的概念,类似的方法完全行不通。这就是新手们常常遇到的问题。

方法行不通,但是不代表思路不行。“低级建模”最基本的思路就是“仿顺序操作”。“低级建模”不是什么困难的东西,它只是一中的“手段”而已,只要你了解它的基本构思,它会成为很有用的工具。

/1

/1

用户1373959 2010-6-4 21:48