例如:HY57V641620HG

4 Banks x 1M x 16Bit Synchronous DRAM

HY颗粒编号 2 ]( Z* o- b) v6 I7 H

! u: p0 m- Y" U& N* [

+ w8 a. x1 S8 U- s

HY XX X XX XX XX X X X X X XX 3 A0 {# A8 |5 J7 M* h# GHY

) N' v) {) B3 m' V( M

HY 57 V 64 16 2 O F TP-7-C

1 2 3 4 5 6 7 8 9 10 11 12

# g0 G! A7 ?$ I: v4 J0 C* u. B

& Y+ ^: O% P) Q+ K1、HY代表是现代的产品

9 \2 O0 r* J1 p/ P' ?6 ` r' P: L' s; j" I/ e/ u c6 E

2、内存芯片类型:(57=SDRAM,5D=DDR SDRAM);

* h( R* \+ a+ }' @& T _- J) u5 @) n% g3 [' W/ a

3、工作电压:空白=5V,V=3.3V,U=2.5V ( c& S9 |+ ^5 U/ K

3 ]( S P2 h6 c, O, v5 G F 4、芯片容量和刷新速率:64:64M 4K刷新;66:64M 2K刷新;28:128M 4K 刷新;56:256M 8K刷新;57:256M 4K刷新;12:512M 8K刷新;1G:1G 8K刷新

1 }5 j" x; ^( \9 @" \" } {$ p) d& U C+ V

5、代表芯片输出的数据位宽:40、80、16、32分别代表4位、8位、16位和32位 7 N0 u) M5 [. }5 n5 X* T

2 R16、BANK数量:1、2、3分别代表2个、4个和8个Bank,是2的幂次关系 & d9 R) ~7 G) x/ k& C, M# N! f

( I# Y. ?7 E* c) Q `" |,7、I/O界面:1 :SSTL_3、 2 :SSTL_2 : | k) u9 x* P2 L9 T

4 l$ ]( }4 D" T2 r+ G$ f$ N

8、芯片内核版本:可以为空白或A、B、C、D等字母,越往后代表内核越新

* e6 N9 z. _+ p8 Y- h5 I! X4 G. ~9 c7 j/ ]( o% @5 J! [/ g

9、代表功耗:L=低功耗芯片,空白=普通芯片

' L2 s: N! ?, t% U6 O) r- z' x+ m2 K/ J- n+ o1 o

10、内存芯片封装形式:JC=400mil SOJ,TC=400mil TSOP-Ⅱ,TD=13mm TSOP-Ⅱ,TG=16mm TSOP-Ⅱ 2 m3 a7 A# s2 ]+ Z Q6 ]

* Y) Z; U% H- {% x" o0 H" T4 Q+ ]

11、工作速度:55 :183MHZ、5 :200MHZ、45 :222MHZ、43 :233MHZ、4 :250MHZ、33 :300NHZ、L DR200、H DR266B、 K DR266A . A8 |4 @, |; Y% K

图 1-1 软件启动画面

图 1-2 新建工程

图 1-3 选择FPGA芯片

图1-4 新建原理图顶层文件

图 1-5 打开SOPC Builder开始定制NIOS II系统

图 1-6 启动画面

图 1-7给NIOS II系统起个名字但这名字还是不要和我们的工程名字相同

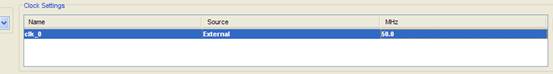

图 1-8选择系统的时钟源

图 1-9 点击NIOS II处理器

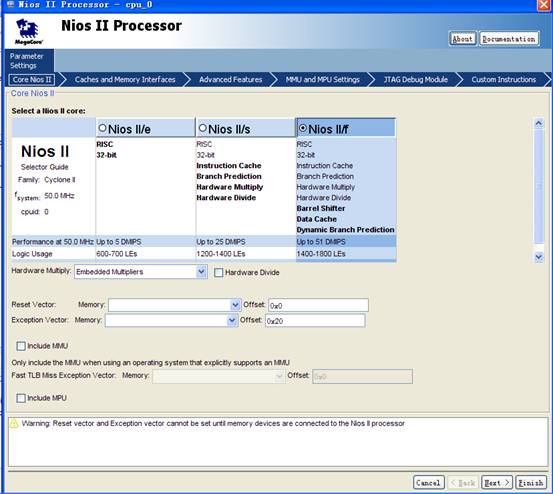

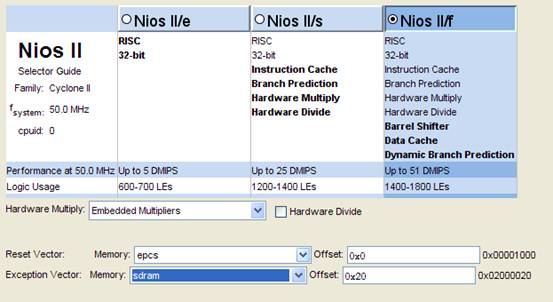

图 1-10 然后选择NIOS的类型

从上图中我们可以看出一共三种CPU提供选择,我们这里选择NIOS II/f快速型的CPU。

图 1-11 将Data Cache关闭

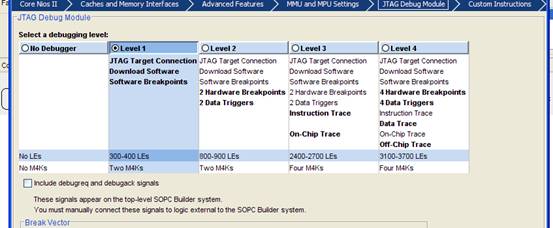

图 1-12 这里选择JTAG Debug Module

选择的等级越高占的资源越大,这里不需要调试很复杂选择Level 1就行了,然后点击finish就可完成NIOS处理器的定制。

图 1-13 定制SDRAM控制器模块

由于实验板上的SDRAM用了2块HY57V641620HG,然后地址线是共用的,数据线分开从而构成地址线12位的数据线为32位的SDRAM。

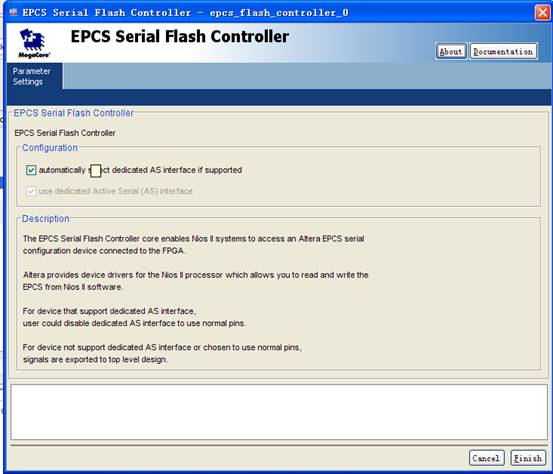

图 1-14 建立EPCS控制器

图1-15 建立SYSTEM ID

图 1-16 建立JTAG UART

图 1-17 设置复位地址和异常地址

图 1-18 将EPCS的起始地址锁定为0x00000000

然后就是自动分配地址,后面还有中断向量自动分配,也可以手动计算改。

图 1-19 然后就是开始编译

编译就要等上几分钟了。

通过上述的那些步骤我们就可以完成了一个最小系统的定制了。

简单的讲框架如下图所示:

图 1-20 最小系统框架

图 1-21 提示编译成功

图 1-22 在原理图中生成的顶层文件

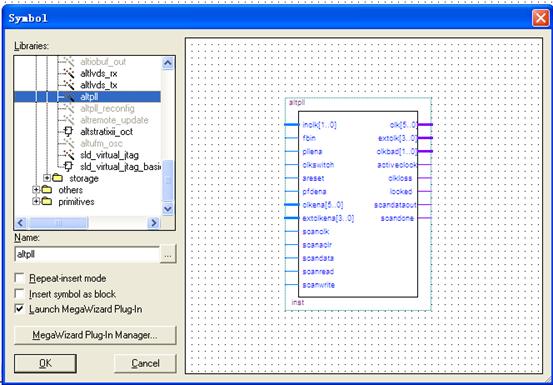

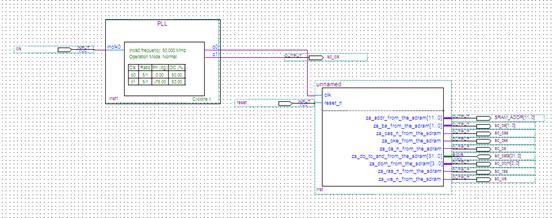

图 1-23 定制PLL锁相环

图 1-24 取名字为PLL

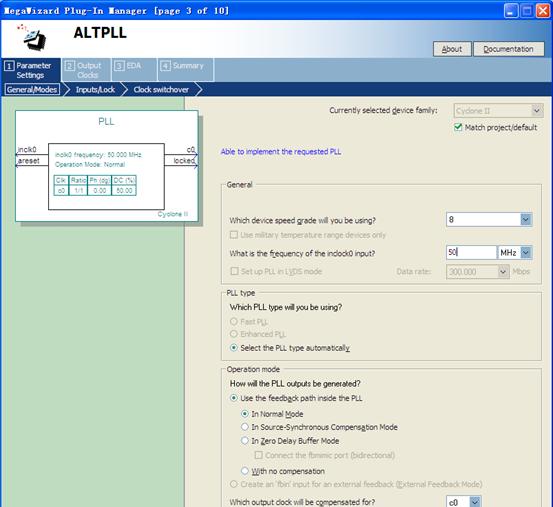

图 1-25 输入时钟为50MHZ

图 1-26 这个等到c1的时候按照上图填写,用来给SDRAM提供时钟,为啥现在还不知。

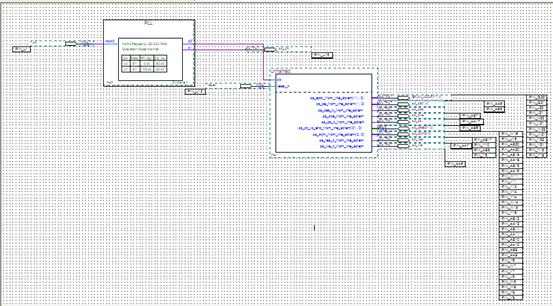

图 1-27 最小系统原理图

然后编译生成sof文件下载到芯片中。

图 1-28 分配好管脚的原理图

/4

/4

文章评论(0条评论)

登录后参与讨论