S3C6410时钟控制(1.1)系统时钟设定

一、S3C6410系统时钟控制的概述

S3C6410系统有三个PLL(APLL/MPLL/EPLL)和四个CLK(ACLK/HCLK/PCLK/SCLK),具体的说是,APLL——用于ARMCLK——用于CPU;

MPLL——用于HCLK和PCLK——HCLK用于AXI/AHB总线外设,PCLK用于APB总线外设;

EPLL——用于SCLK——用于其他外设,特别是音频相关的外设,还有UART/IIS/IIC等;

每个外设块的时钟信号都可以被启用或者禁用,由软件控制以减少电源消耗。

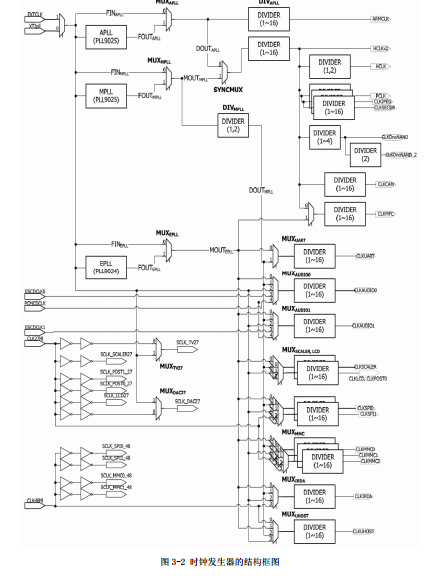

(1)下图是时钟发生器的体系结构。

(2)时钟源的选择,这个是硬件连接,详见S3C6410用户手册。

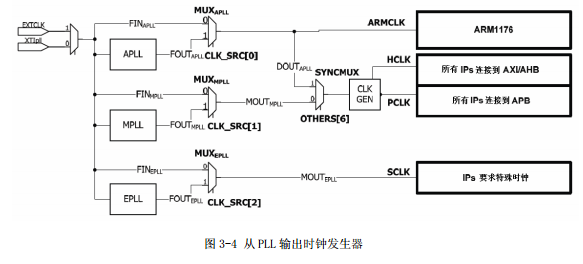

(3)PLL和CLK的结构关系,见下图

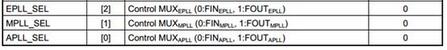

这里需要注意的是,APLL产生的时钟也可以通过SYNCMUX(OTHERS[6])的选择,作为HCLK和PCLK的输入源。另外CLK_SRC[0/1/2]控制选择三组时钟源是PLL还是FIN。

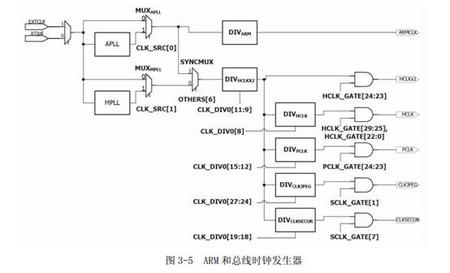

(4)ARM和AXI/AHB/APB总线发生器

AXI,AHB总线最高工作在133MHz频率下,APB总线最高工作在66MHz频率下。由于APB和AXI,AHB总线上二者工作频率不一致,在这两种总线上进行数据同步传输时会采用特殊逻辑单元,频率比率在 AHB 时钟和 APB 时钟之间必须有一个整数值;并且AHB总线和APB总线上的频率必须是偶数,则分频系数一般为奇数;AHB总线上的JPEG和安全相关子系统不能工作在133MHz,AHB总线专门为这样低频子系统提供低频工作时钟,通过设置DIV(CLKJPEG)和DIV(CLKSECUR)分频位来设置其工作频率。

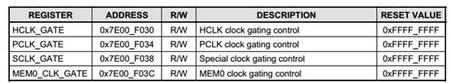

从以上的图中可以说明,HCLK_GATE,PCLK_GATE 和 SCLK_GATE 控制时钟操作。如果一个位被设置,则通过每个时钟分频器相应的时钟将会被提供,否则将被屏蔽。

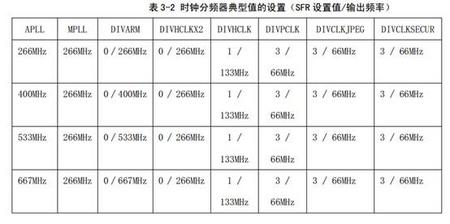

下图是提供的建议时钟分配方案:

(5)时钟比例的变化。时钟分频器产生的各种操作时钟从1状态变为2状态有一个变化的周期,这个周期还不是固定的,一般为10~20时钟周期,这个需要注意。

二、S3C6410系统时钟相关定时器

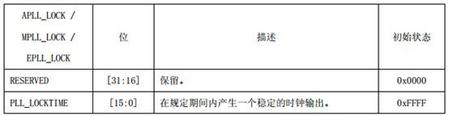

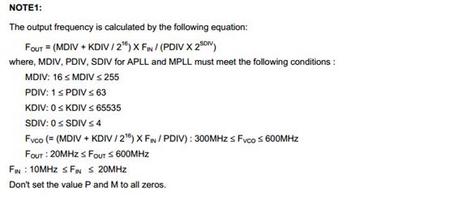

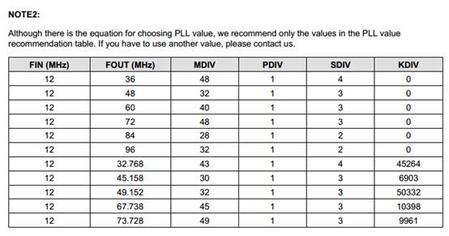

(1)PLL相关的寄存器,一类是控制寄存器,一类是锁存寄存器。

其中LOCK寄存器用来在时钟变化的周期,屏蔽输出,以产生一个稳定的输出,设定值为时间长度。

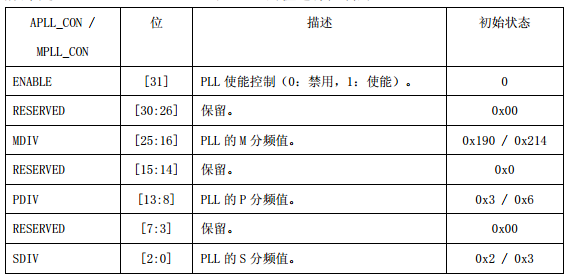

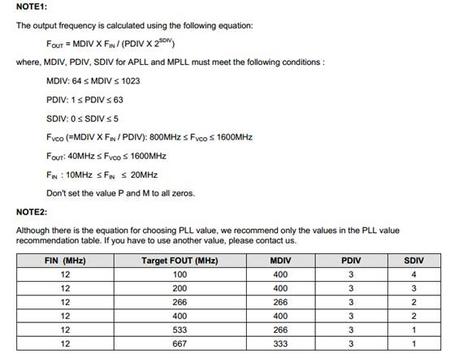

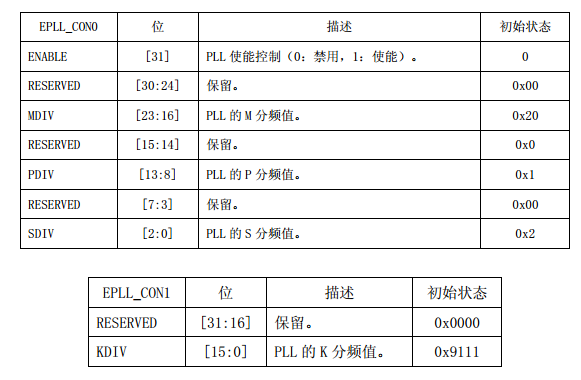

CON寄存器为控制寄存器,设定各种分频值,从而产生合适的频率。

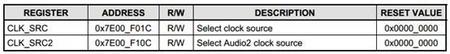

(2)时钟源控制寄存器,6410有很多时钟源,不仅有PLL、外部晶振、还有外部时钟或者GPIO的时钟源。时钟源控制寄存器控制了每一个时钟源多路选择器MUX,包括一些特殊外设,这里仅截取了最后3位。

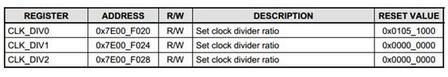

(3)时钟分频器控制寄存器,控制每一个分频器(divider)支持不同的频率要求,具体使用哪一个寄存器的哪一位,见详细的表格。其中CLK_DIV0 主要控制系统时钟和多媒体 IP 的特殊时钟,HCLKX2,HCLK 和 PCLK 的最大操作频率分别为 266MHz,133MHz 和 66MHz。NAND,SECUR 和 JPEG 的时钟操作不能超过 66MHz。MFC 和 CAM 时钟操作不能操过 133MHz;CLK_DIV1 控制MMC,LCD,TV 定标器和UHOST 时钟;CLK_DIV2 控制SPI,AUDIO,UART和IrDA 时钟。具体见用户手册。

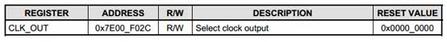

(4)时钟输出配置寄存器。可以将PLL/HCLK/48M/27M/RTC等时钟输出,也可对其进行分频等处理。可以用来监测系统时钟的设置或者供给其他芯片时钟。输出口GPF。

(5)时钟选通控制寄存器。可以禁止每一个IP的时钟工作,具体的见每一位。初始值为1,都是允许的。

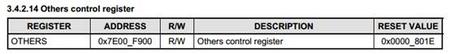

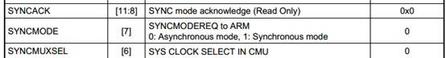

(6)其他寄存器

这里面基本的就是设定时钟的同步异步工作模式。

![]()

(不好意思,估计是截图太多,ednchina不支持,所以分成了两个)

/2

/2

用户403664 2014-4-23 10:28