Altera FPGA中的延时进位链-LCELL

在ALtera的FPGA中需要通过原语添加LCELL添加固定的延时,一般来讲,LCELL的延时相对比较固定,但是随着布线以及温度等影响,延时会有变化,所以通过LCELL设计延时进位链需要计算单个LCELL延时以及控制布线和位置约束。

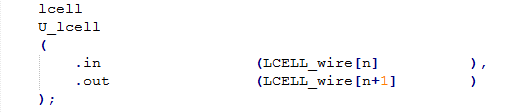

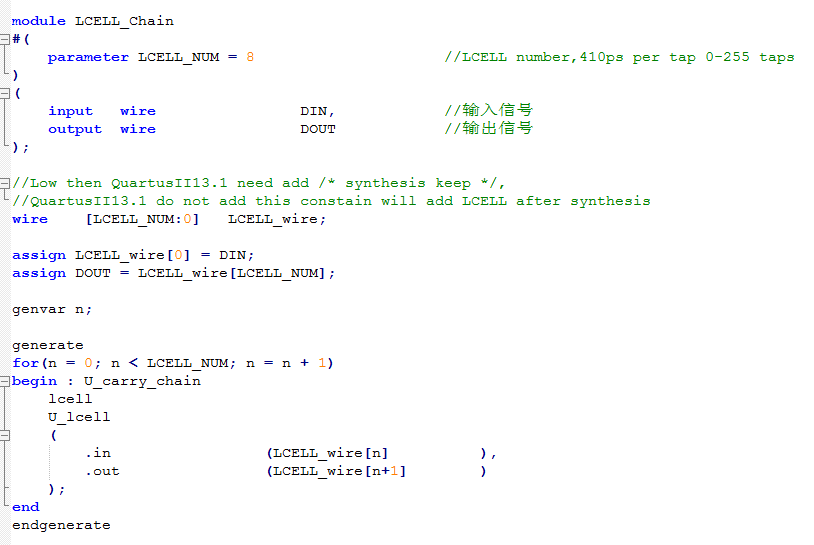

原语调用LCELL如下:

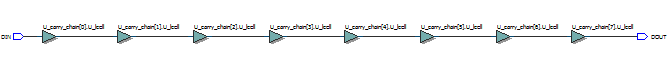

RTL View图如下:

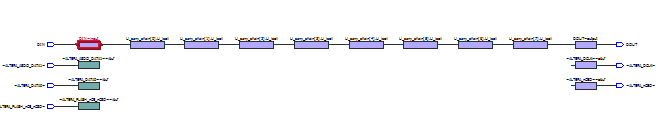

Post Fitting图如下:

实际上添加了8个LCELL:

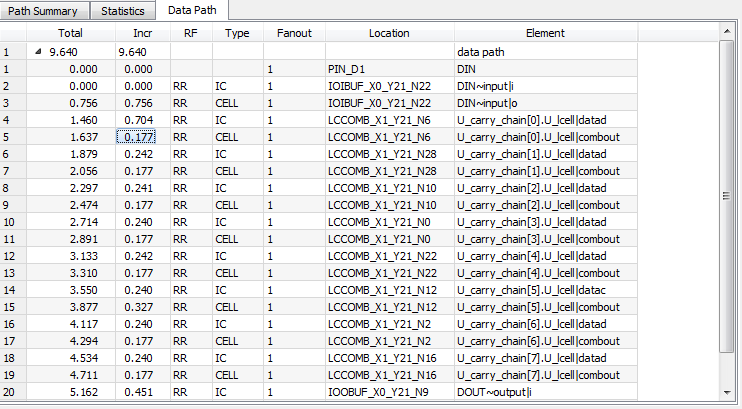

每个LCELL大约的延时为0.41ns,TimeQuest分析如下:

可以看到LCELL延时大约等于CELL+IC=0.41ns

整个延时链代码如下:

QuartusII13.1版本的软件不需要添加约束,如果添加Keep等原语约束的话,会额外增加LCELL数量

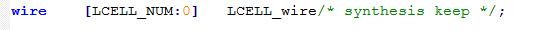

在低于QuartusII13.1以前的版本中需要添加约束或者设置来防止软件优化LCELL

1. 通过QuartusII中的设置实现

完成下列两个设置即可实现settings ->Analysis&Synthesis -> more settings:

"Remove redundant logic cells" , must be "off"

"Ignore LCELL buffers", must be "off"

2、通过在HDL中添加综合属性来实现

采用keep来约束wire防止自动优化。

/5

/5

sapphire 2024-3-17 16:20