Simulated waveforms &Machine instructions:

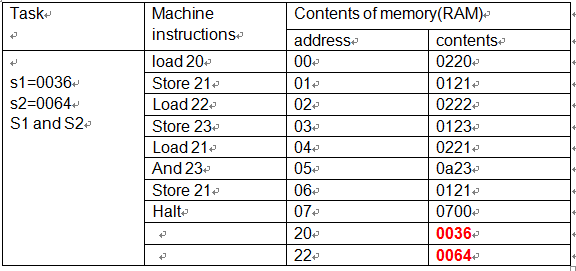

Just AND:

Machine instructions:

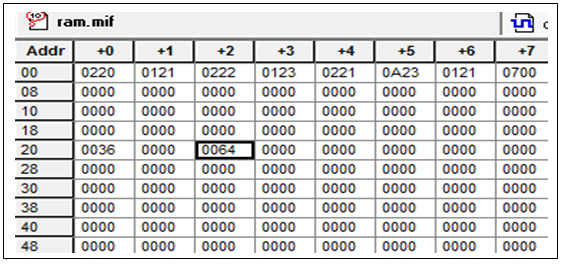

The ram.mif

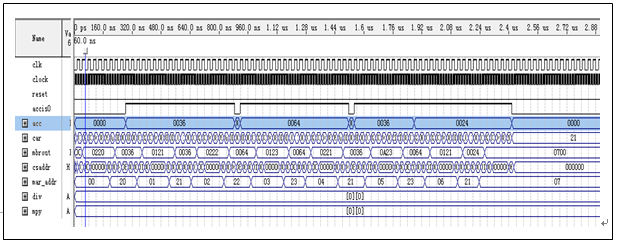

The waveforms and results

Explanation: If s1=0036,s2=0064 Then s1 and s2? From the waveform we can

find s1 and s2=0024.

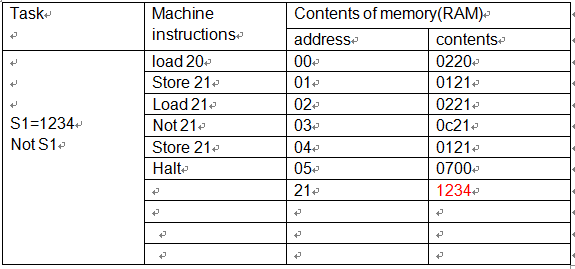

Just not

Machine instructions:

The ram.mif

The waveforms and results

Explanation: If s1=1234,then not s1=? From the waveform we find s1=EDCB

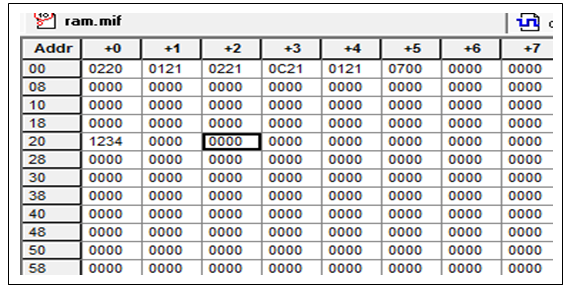

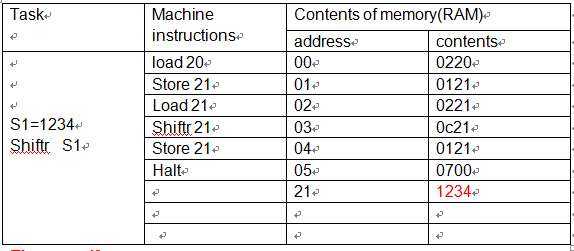

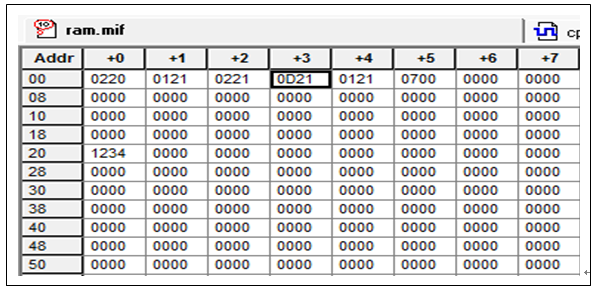

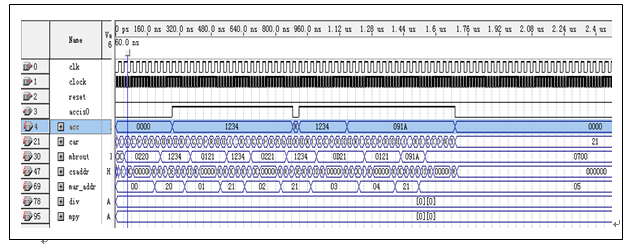

Just shiftr

Machine instructions:

The ram.mif

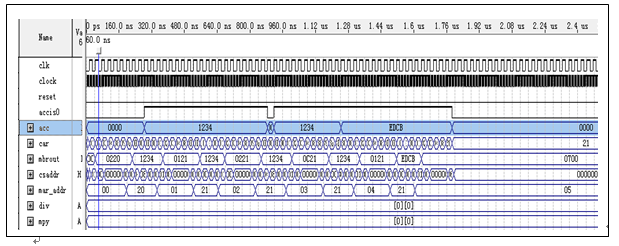

The waveforms and results

Explanation: If s1=1234,then shiftr s1=? From the waveform we find s1=091A.

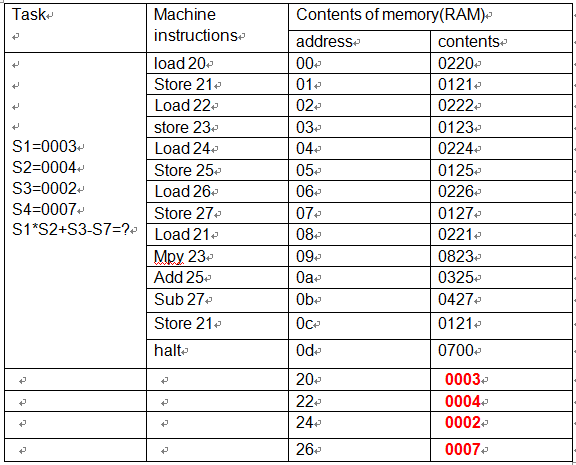

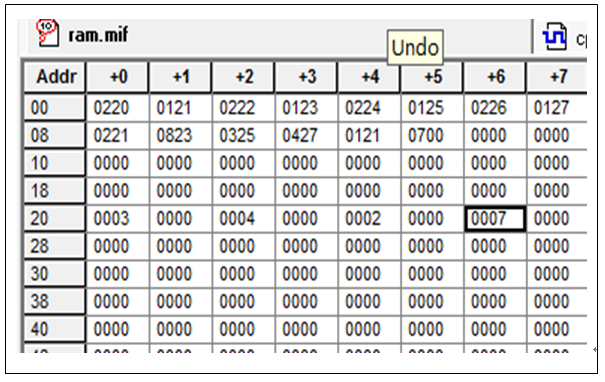

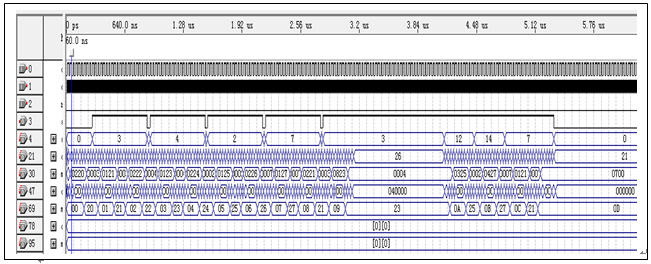

ADD,SUB,MPY

Machine instructions:

The ram.mif

The waveforms and results

Explanation: s1=3,s2=4,s3=2,s4=7, From the waveform we find 3*4+2-7=7.

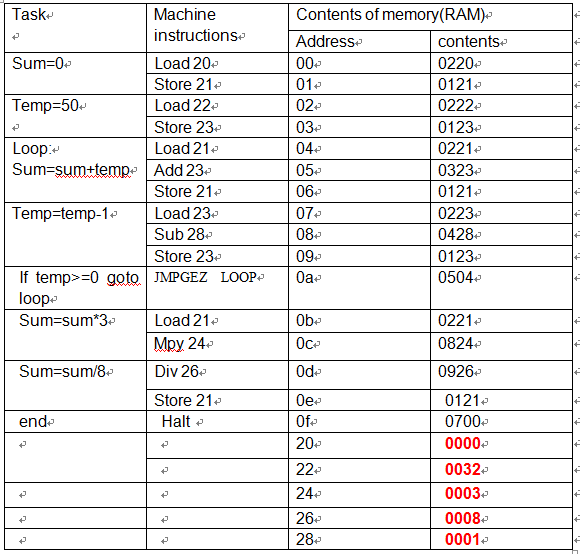

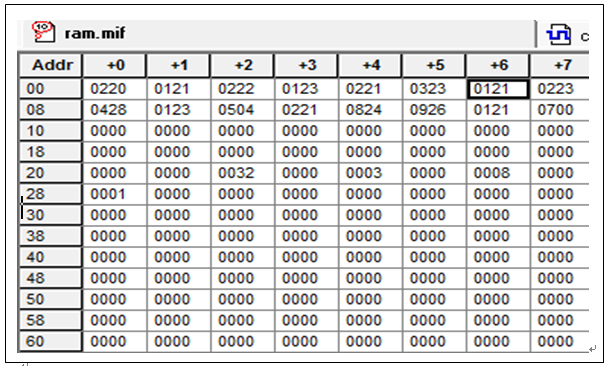

ADD,LOOP,MPY,DIV(1+2+…+49+50)*3/8

Machine instructions:

The ram.mif

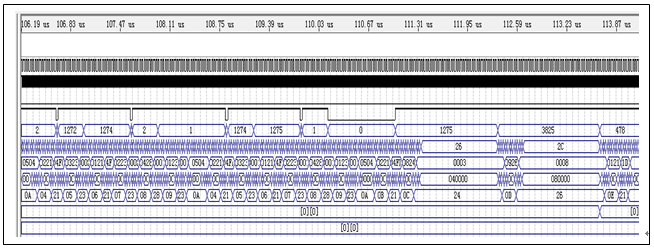

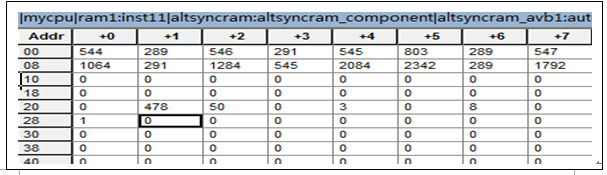

The waveforms and results

Explanation: From the waveform we find 1+2+…+49+50=1275, 1275*3=3825,

3285/8=478.

The contents of location 21 is 478

Conclusions:

1、From the experiment we learn what is cpu, how the cpu works.

2、Through using quartus2 ,I learn to program by myself, in the experiment I found two errors ,then I try to solve the problem. Errors 1: ACTION: Successfully run the Timing Analyzer or Fitter before running timing simulation. Solutions:start classic timing analyzer first; Errors 2: Error: Cannot run Timing Analyzer (quartus_tan) -- Fitter (quartus_fit) failed or was not run solutions: start fitter first.

3、Of course, in the meantime I meet multiple difficulties, I ask my classmates, we help each other.

4、Programming needs to be patient, we should remember it.

/4

/4

文章评论(0条评论)

登录后参与讨论