作者:一博科技高速先生成员 刘春

在前几期的文章“为什么DDR走线要走同组同层?”中,我们了解了信号在传输线上的传输速度以及微带线与带状线传输的时延差异。同时也有很多热情的网友对影响传输线时延情况给出了各自的见解,比如串扰,绕线,过孔,跨分割等等。本期我们就以不同模态下的串扰对信号时延的影响继续通过理论分析和仿真验证的方式跟大家一起进行探讨。

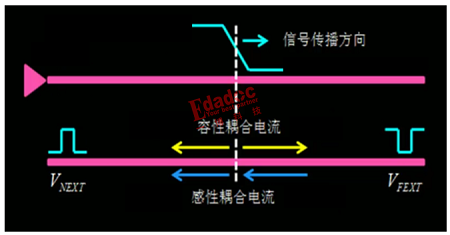

在开始仿真之前我们先简单的了解一下什么是串扰以及串扰是怎么形成的。如下图所示,当有信号传输的走线和相邻走之间间距较近时,有信号传输的走线会在相邻走线上引起噪声,这种现象称为串扰。

串扰形成的根本原因在于相邻走线之间存在耦合,如下图所示:

当信号在一走线上传输时,一部分能量会通过电场容性耦合和磁场感性耦合到相邻走线上,从而引起串扰噪声,并以耦合后产生串扰噪声方向的不同区分为近端串扰(VNEXT)和远端串扰(VFEXT)。如下图所示,以微带线为例,当传输信号为正跳变向前传输时,近端串扰会产生一个正跳变脉冲的串扰噪声,远端串扰则会产生一个负跳变脉冲的串扰噪声。而对于内层走线的串扰与微带线有所不同,内层走线的远端串扰几乎为0,这里关于串扰的详细机理就不再多做介绍了,感兴趣的朋友可以查找相关的资料进行更深入的了解。

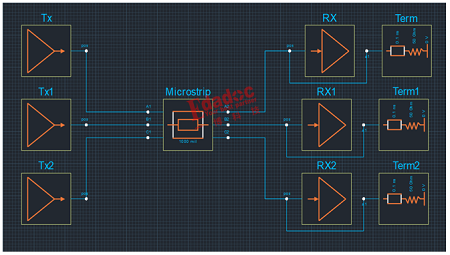

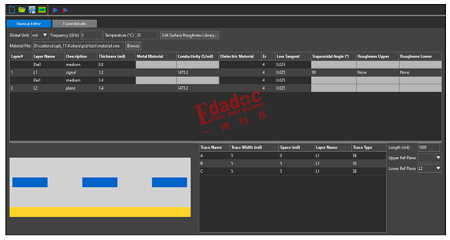

下面我们利用Sigrity中Sigrity Topology Explorer进行仿真验证。为了更好的体现不同模态下走线串扰对信号传输时延的影响,如下图所示,这里模拟了三条线长1000mil的相邻微带线A,B,C进行仿真。

其中,A和C作为干扰源信号,B作为被干扰信号,仿真验证对比下面三种工作状态下被干扰信号B的时延情况:

(1)no_crosstalk: A和C中没有信号;

(2)even_crosstalk: A和C与B同相;

(3)odd_crosstalk: A和C与B反相;

搭建仿真链路如下图所示:

叠层设置如下图所示,其中线宽:5mil;线距:5mil。

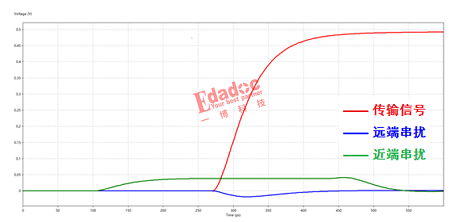

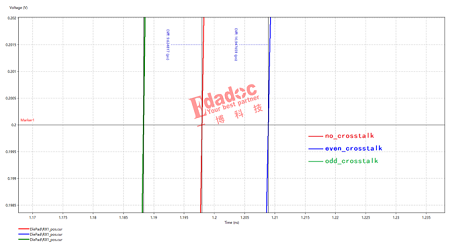

仿真结果:

even_crosstalk偶模工作状态下信号的传输时延比没有串扰no_crosstalk的工作状态下信号的传输时延慢了约10.9ps;

odd_crosstalk奇模工作状态下信号的传输时延比没有串扰no_crosstalk的工作状态下信号的传输时延快了约9.6ps。

那是什么造成这种传输的时延差异呢?相信大家心里已经有了答案,正是串扰造成的。这里我们根据前面对串扰的了解来进行分析造成该差异的原因。以没有串扰no_crosstalk的工作状态时延为参考,当信号处于even_crosstalk偶模工作状态时,干扰信号与被干扰信号同相跳变,使得干扰信号产生在被干扰信号上的远端串扰噪声与被干扰信号跳变方向相反,并叠加在被干扰信号上,致使被干扰信号的边沿跳变延迟到达,而当信号处于odd_crosstalk奇模工作状态时则与此相反,干扰信号产生在被干扰信号上的远端串扰噪声与被干扰信号跳变方向相同,并叠加在被干扰信号上,致使被干扰信号的边沿跳变提前到达。

从上面的仿真验证,我们知道串扰会影响信号的时延,那么我们该如何避免或减小这种影响呢?这里小编趁此机会又继续做了如下几种情况下的仿真验证:

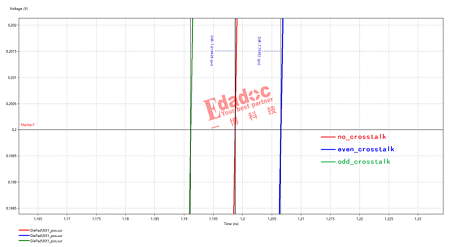

(1)其他条件不变,走线间距改成10mil,仿真结果如下图所示:

even_crosstalk偶模工作状态下信号的传输时延比没有串扰no_crosstalk的工作状态下信号的传输时延慢了约7.7ps;

odd_crosstalk奇模工作状态下信号的传输时延比没有串扰no_crosstalk的工作状态下信号的传输时延快了约7.6ps。

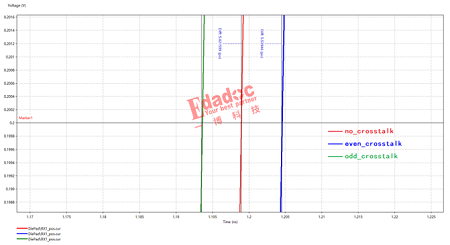

(2)其他条件不变,走线间距改成15mil,仿真结果如下图所示:

even_crosstalk偶模工作状态下信号的传输时延比没有串扰no_crosstalk的工作状态下信号的传输时延慢了约5.5ps;

odd_crosstalk奇模工作状态下信号的传输时延比没有串扰no_crosstalk的工作状态下信号的传输时延快了约5.4ps。

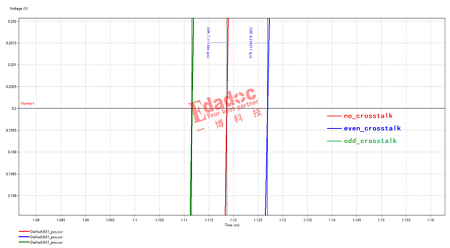

(3)其他条件不变,走线长度改成500mil,仿真结果如下图所示:

even_crosstalk偶模工作状态下信号的传输时延比没有串扰no_crosstalk的工作状态下信号的传输时延慢了约8.2ps;

odd_crosstalk奇模工作状态下信号的传输时延比没有串扰no_crosstalk的工作状态下信号的传输时延快了约7.1ps。

从上述仿真结果可知,对于相邻的微带线,拉开走线间距,可以减弱走线间电场和磁场的耦合,从而降低在被干扰信号上产生的远端串扰噪声,减小走线之间因串扰造成的时延差异;而减小走线的耦合长度,则可减小远端串扰噪声的积累,以减小走线之间因串扰造成的时延差异。

另外对于带状线而言,远端串扰近似为0,意味着远端串扰几乎不会对走线在内层信号时延有影响,需要关注的只是传输方向相反的信号之间的近端串扰对信号造成的时延影响,因此走线在内层可以减小走线之间因远端串扰造成的时延差异。

问题来了

在绕线等长设计中,如DDR等长中的蛇形绕线又是如何影响信号传输的时延的?

作者: 一博科技, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3860940.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/4

/4

文章评论(0条评论)

登录后参与讨论