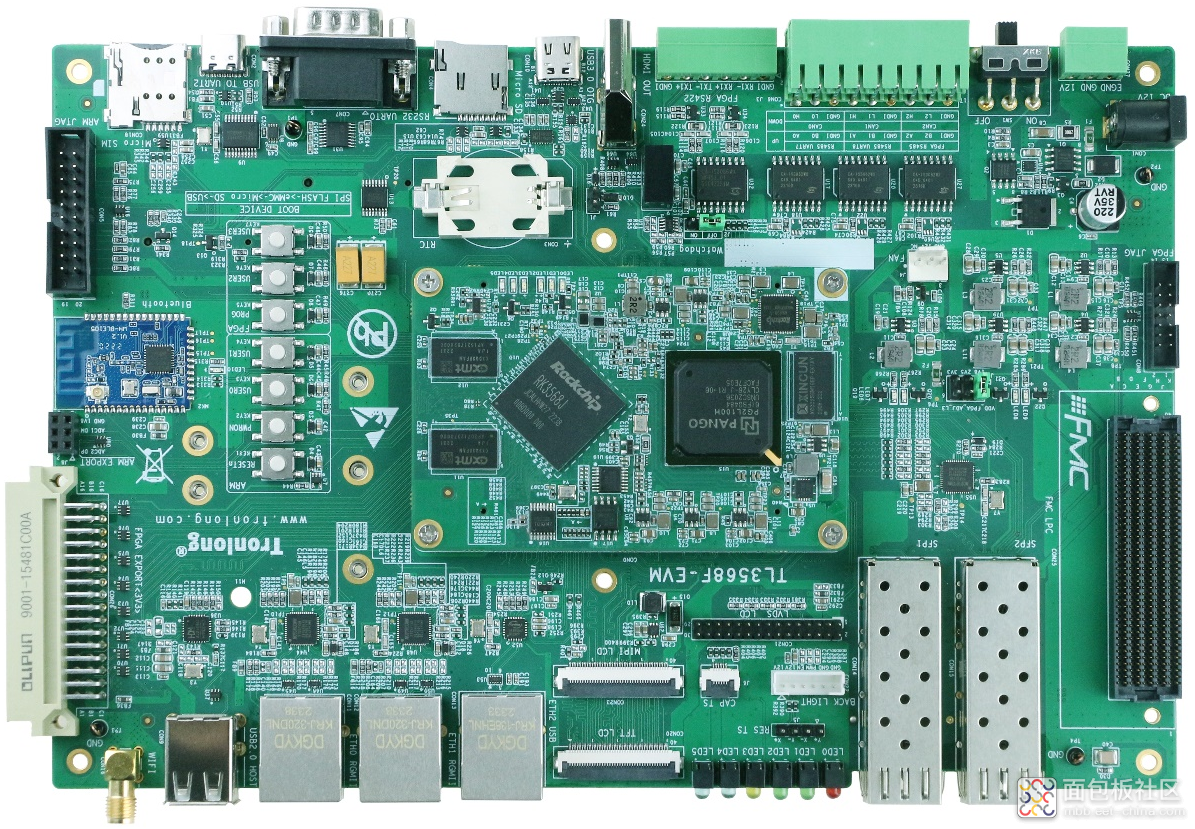

创龙科技TL3568F-EVM是一款基于瑞芯微RK3568J/RK3568B2四核ARM Cortex-A55处理器 + 紫光同创Logos-2 PG2L50H/PG2L100H FPGA设计的异构多核国产工业评估板,由核心板和评估底板组成,ARM Cortex-A55处理单元主频高达1.8GHz/2.0GHz。核心板ARM、FPGA、ROM、RAM、电源、晶振、连接器等所有元器件均采用国产工业级方案,国产化率100%。同时,评估底板大部分元器件亦采用国产工业级方案,国产化率约为99%(按元器件数量占比,数据仅供参考)。

核心板内部RK3568J/RK3568B2与Logos-2通过PCIe 2.0、FSPI、I2C、GPIO连接,经过专业的PCB Layout和高低温测试验证,质量稳定可靠,可满足各种工业应用环境要求。

评估板接口资源丰富,引出3路Ethernet、3路USB、3路CAN、RS422/RS485、2路SFP、FMC等通信接口,同时引出MIPI LCD、LVDS LCD、TFT LCD、HDMI OUT视频接口,支持多屏异显,板载WIFI、Bluetooth模块,支持选配4G/5G模块、SATA固态硬盘,方便用户快速进行产品方案评估与技术预研。

图1评估板正面图

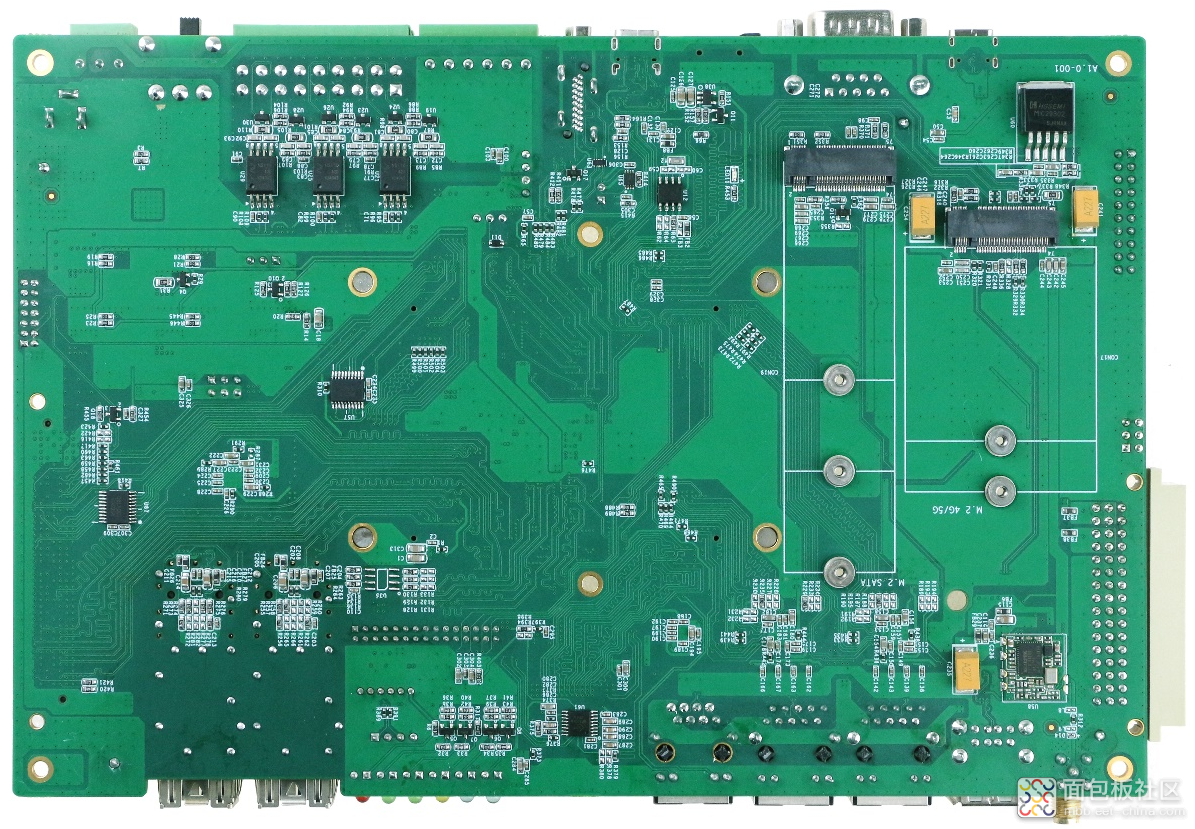

图2评估板背面图

图3评估板斜视图

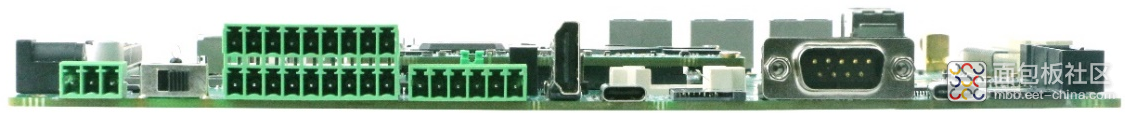

图4评估板侧视图1

图5评估板侧视图2

图6评估板侧视图3

图7评估板侧视图4

1 led_flash案例

1.1案例说明

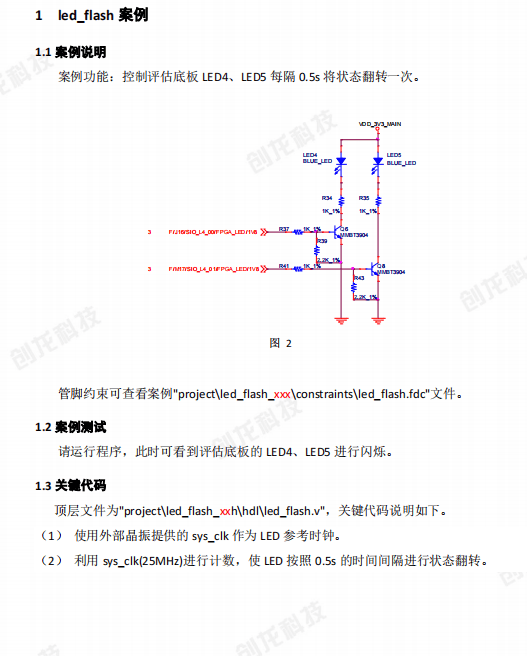

案例功能:控制评估底板LED4、LED5每隔0.5s将状态翻转一次。

管脚约束可查看案例"projectVled_flash_xxx\constraintsVed_flash.fdc"文件。

1.2案例测试

请运行程序,此时可看到评估底板的LED4、LED5进行闪烁。

1.3关键代码

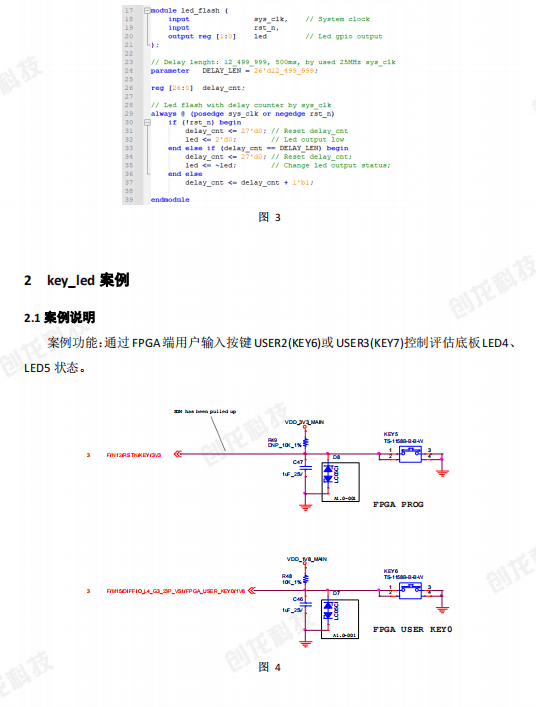

顶层文件为"project\Vled_flash_xxh\hdlVled_flash.v",关键代码说明如下。

(1)使用外部晶振提供的sys_clk作为LED参考时钟。

(2)利用sys_clk(25MHz)进行计数,使LED按照0.5s的时间间隔进行状态翻转。

2 key_led案例

2.1案例说明

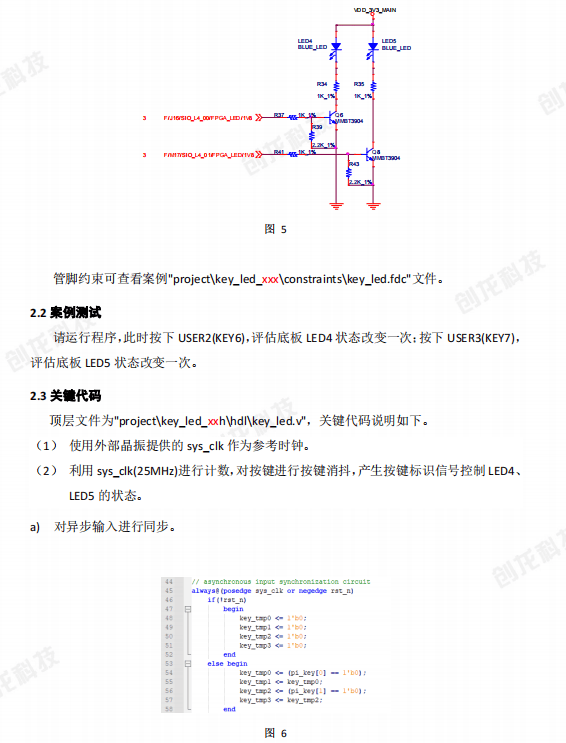

案例功能:通过FPGA端用户输入按键USER2(KEY6)或USER3(KEY7)控制评估底板LED4、 LED5状态。

管脚约束可查看案例"project\key_led_xxx\constraints\key_led.fdc"文件。

2.2案例测试

请运行程序,此时按下USER2(KEY6),评估底板LED4状态改变一次;按下USER3(KEY7), 评估底板LED5状态改变一次。

2.3关键代码

顶层文件为"project\key_led_xch\hdl\key_led.v",关键代码说明如下。

(1)使用外部晶振提供的sys_clk作为参考时钟

(2)利用sys_ck(25MHz)进行计数,对按键进行按键消抖,产生按键标识信号控制LED4、 LED5的状态。

a)对异步输入进行同步。

b)产生20ms计数器用于按键消抖。

c)对按键按下消抖后产生标志信号。

d)通过按键标识信号控制LED状态。

3 uart_rw_rs485 案例

3.1案例说明

案例功能:上位机向评估板FPGA RS485串口发送数据,评估板接收到数据后将数据 重新返回上位机。

管脚约束可查看案例"project\uart_rw_rs485_pg21xxh\constraints\uart_Nw_rs485.fdc"文 件。

3.2 案例测试

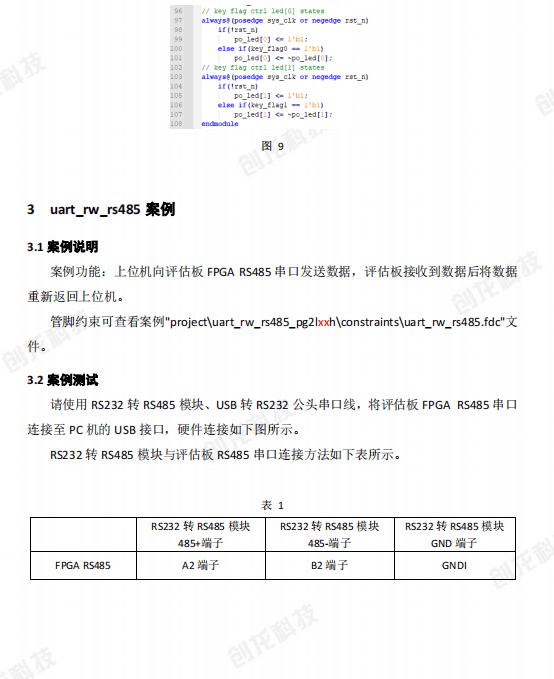

请使用RS232转RS485模块、USB转RS232 公头串口线,将评估板 FPGA RS485串口 连接至PC机的 USB接口,硬件连接如下图所示。

RS232转RS485模块与评估板 RS485串口连接方法如下表所示。

打开产品资料“4-软件资料\Tools\Windows\”目录下的串口调试助手.exe,打开PC机 设备管理器,确认FPGA RS485串口COM端口号,并按照下图步骤进行操作或设置。

程序加载后,上位机向评估板发送"Tronlong",评估板在接收到数据后,会将数据重 新返回给上位机。

3.3关键代码

顶层文件为"project\uart_w_rs485_pg2bxch\hdl\uart_rw_rs485.v",关键代码说明如下。

(1)端口定义。

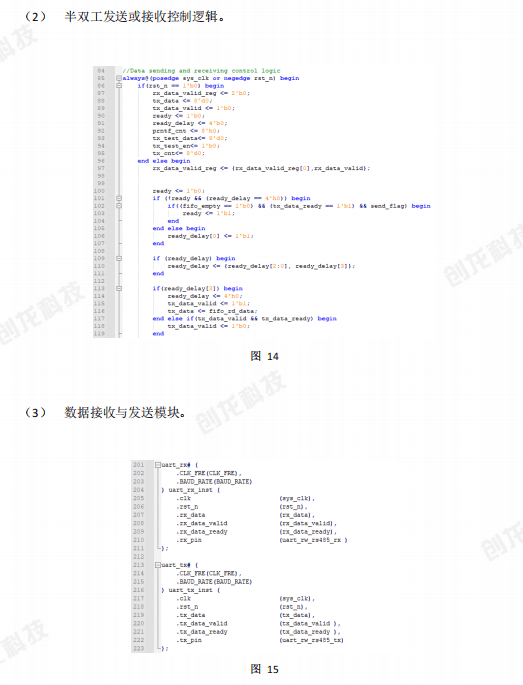

(2)半双工发送或接收控制逻辑。

(3)数据接收与发送模块。

(4)FIFO模块,实现对接收或发送的数据进行暂存缓冲。

4 uart_rw_rs422案例

4.1案例说明

案例功能:上位机向评估板FPGARS422串口发送数据,评估板接收到数据后将数据 重新返回上位机。

管脚约束可查看案例"project\uart_rw_rs422_pg21xxh\constraints\uart_Nw_rs422.fdc"文 件。

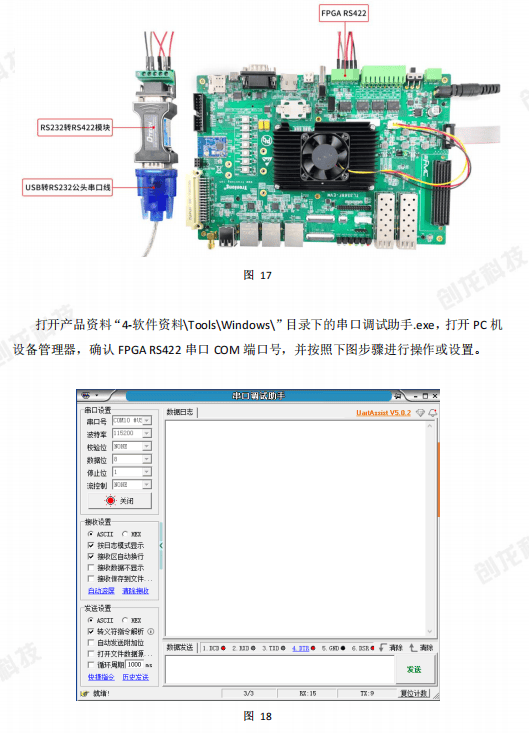

4.2案例测试

请使用RS232转RS422模块、USB转RS232公头串口线,将评估板FPGA RS422串口 连接至PC机的USB接口,硬件连接如下图所示。

RS232转RS422模块与评估板RS422串口连接方法如下表所示。

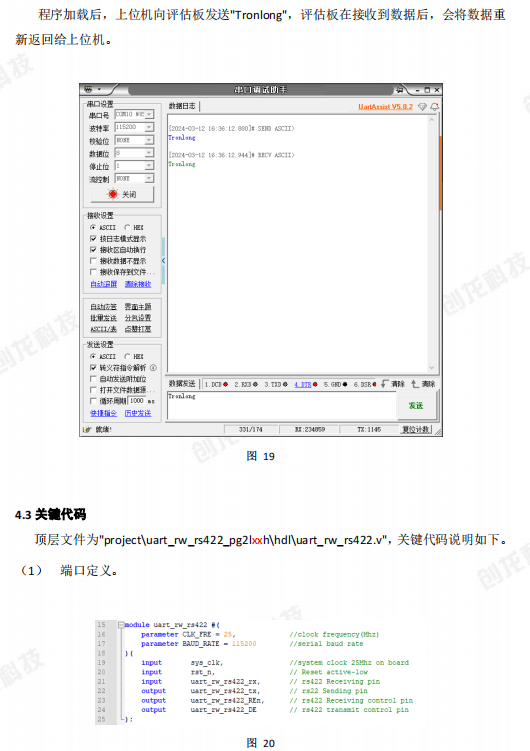

打开产品资料“4-软件资料\Tools\Windows\”目录下的串口调试助手.exe,打开PC机 设备管理器,确认FPGA RS422串口COM端口号,并按照下图步骤进行操作或设置。

程序加载后,上位机向评估板发送"Tronlong",评估板在接收到数据后,会将数据重 新返回给上位机。

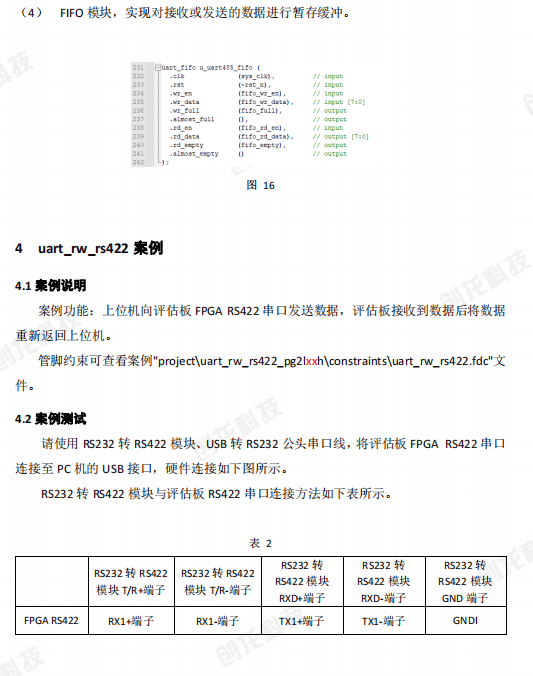

4.3关键代码

顶层文件为"project\uart_w_rs422_pg2lxch\hdl\uart_w_rs422.v",关键代码说明如下。

(1)端口定义。

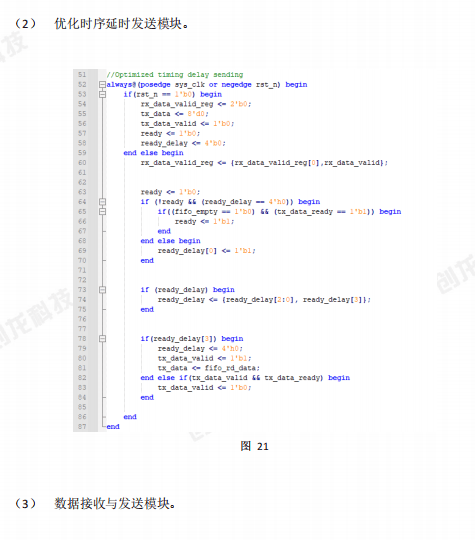

(2)优化时序延时发送模块。

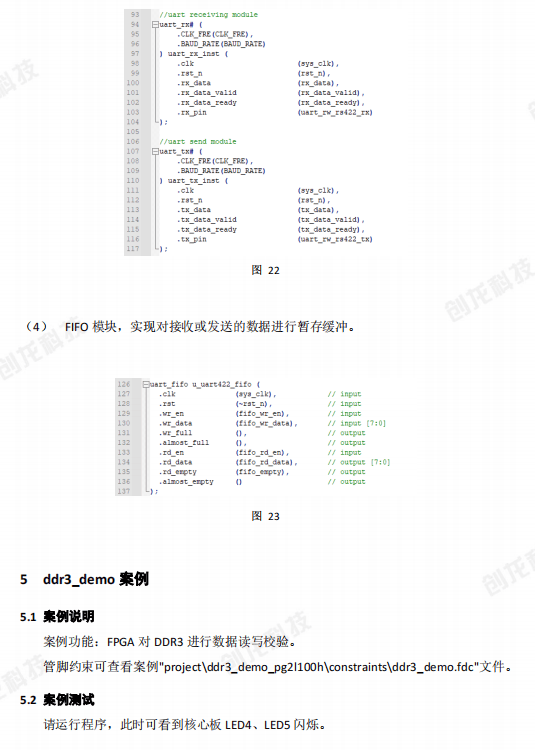

(3)数据接收与发送模块。

(4)FIFO模块,实现对接收或发送的数据进行暂存缓冲。

5 ddr3_demo案例

5.1案例说明

案例功能:FPGA对DDR3进行数据读写校验。 管脚约束可查看案例"project\ddr3_demo_pg21100h\constraints\ddr3_demo.fdc"文件。

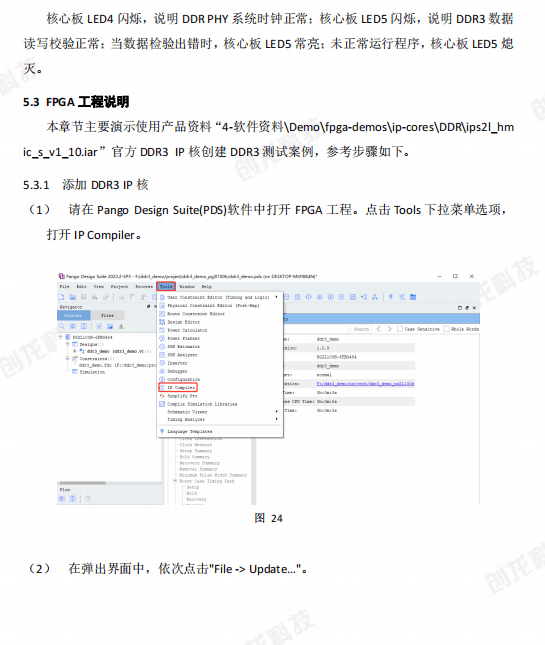

5.2案例测试

请运行程序,此时可看到核心板LED4、LED5闪烁。

核心板LED4闪烁,说明DDRPHY系统时钟正常:核心板LED5闪烁,说明DDR3数据 读写校验正常:当数据检验出错时,核心板LED5常亮:未正常运行程序,核心板LED5熄 灭。

5.3 FPGA工程说明

本章节主要演示使用产品资料“4-软件资料\Demo\fpga-demos\jp-cores\DDR\ips2l_hm ic_5_v1_10.iar”官方DDR3 IP核创建DDR3测试案例,参考步骤如下。

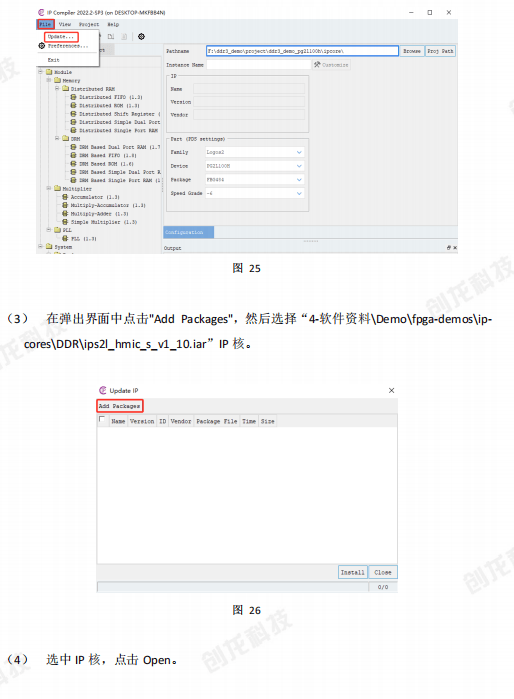

5.3.1添加DDR3 IP核

(1)请在Pango Design Suite(PDS)软件中打开FPGA工程。点击Tools下拉菜单选项, 打开IP Compiler。

(2)在弹出界面中,依次点击"File>Update."。

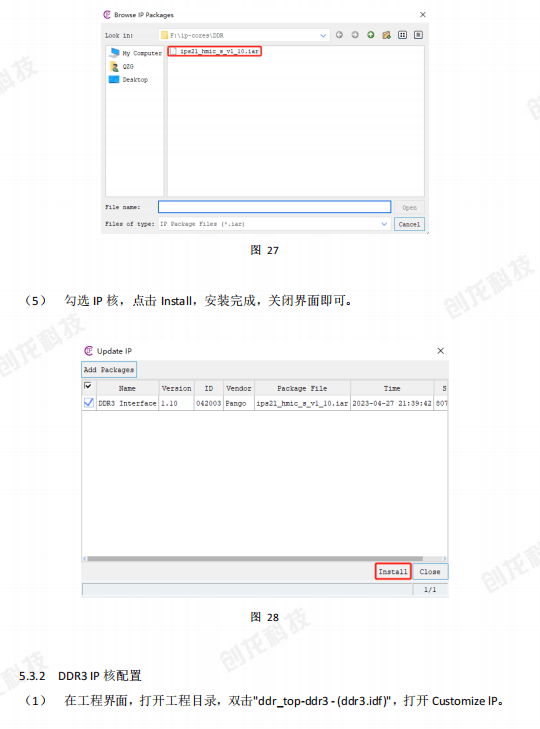

(3)在弹出界面中点击"Add Packages",然后选择“4-软件资料\Demo\fpga-demos\ip- cores\DDR\ips2I_hmic_s_v_10.iar”IP核。

(4)选中IP核,点击Open。

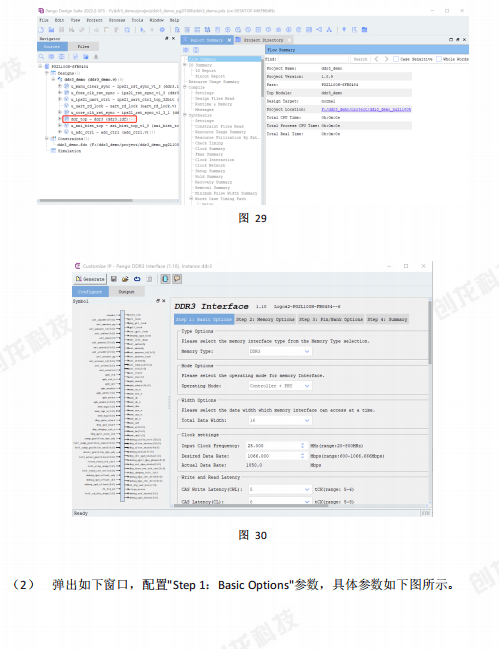

(5)勾选IP核,点击Install,安装完成,关闭界面即可。

5.3.2 DDR3 IP核配置

(1)在工程界面,打开工程目录,双击"ddr_top-ddr3-(ddr3.idfj",打开Customize IP。

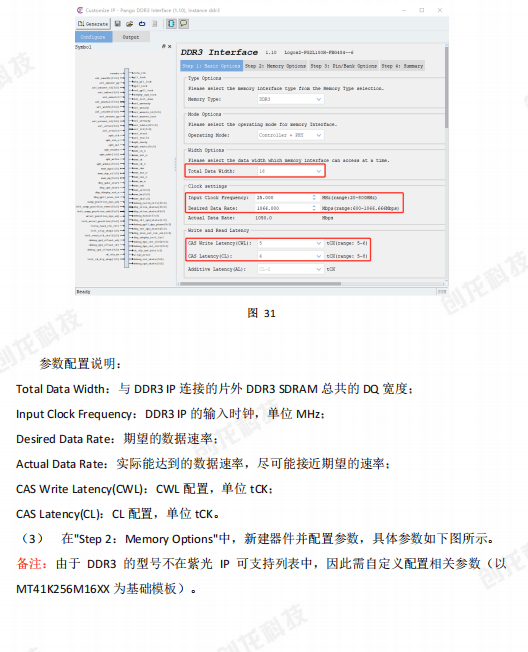

(2)弹出如下窗口,配置"Step 1:Basic Options"参数,具体参数如下图所示。

参数配置说明:

Total Data Width:与DDR3 IP连接的片外DDR3 SDRAM总共的DQ宽度:

Input Clock Frequency:DDR3 IP的输入时钟,单位MHz;

Desired Data Rate:期望的数据速率

Actual Data Rate:实际能达到的数据速率,尽可能接近期望的速率:

CAS WriteLatency(OWL):CWL配置,单位tCK:

CAS Latency(CL):CL配置,单位tCK。

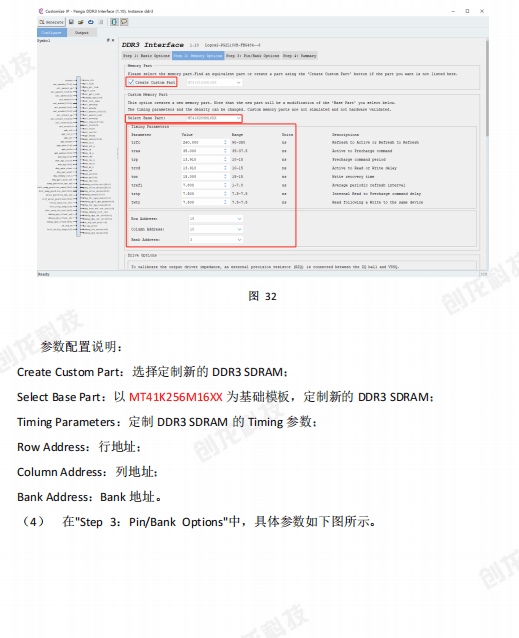

(3)在"Step 2:MemoryOptions"中,新建器件并配置参数,具体参数如下图所示 备注:由于DDR3的型号不在紫光IP可支持列表中,因此需自定义配置相关参数(以 MT41K256M16XX为基础模板)。

参数配置说明:

CreateCustom Part:选择定制新的DDR3 SDRAM:

Select BasePart:以MT41K256M16XX为基础模板,定制新的DDR3 SDRAM

TimingParameters:定制DDR3 SDRAM的Timing参数:

Row Address:行地址:

Column Address:列地址:

Bank Address:Bank地址。

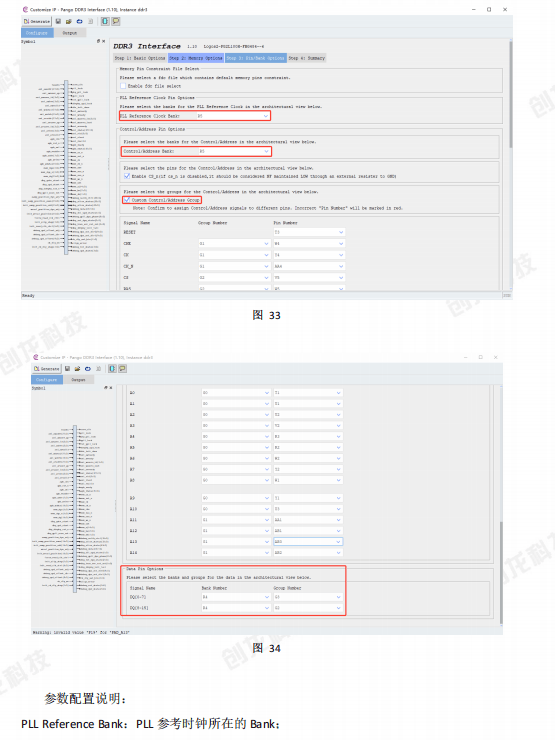

(4)在"Step 3:Pin/Bank Options"中,具体参数如下图所示。

参数配置说明:

PLL Reference Bank:PLL参考时钟所在的Bank:

Control/Address Bank:Memory接口的控制和地址线所在的Bank:

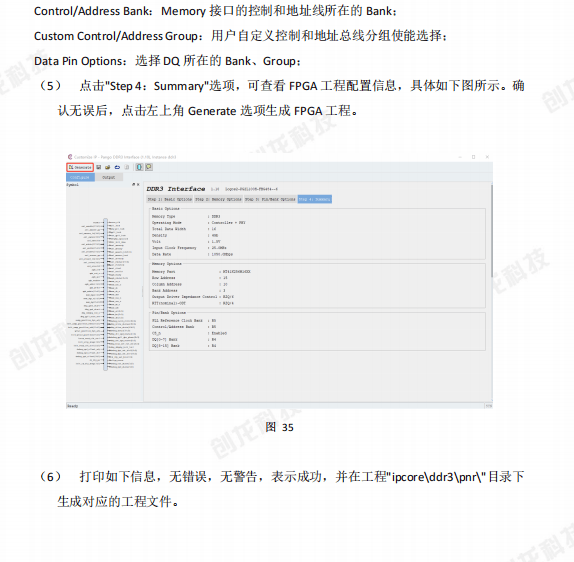

Custom Control/Address Group:用户自定义控制和地址总线分组使能选择: DataPinOptions:选择DQ所在的Bank、Group:

(5)点击"Step 4:Summary"选项,可查看FPGA工程配置信息,具体如下图所示。确 认无误后,点击左上角Generate选项生成FPGA工程。

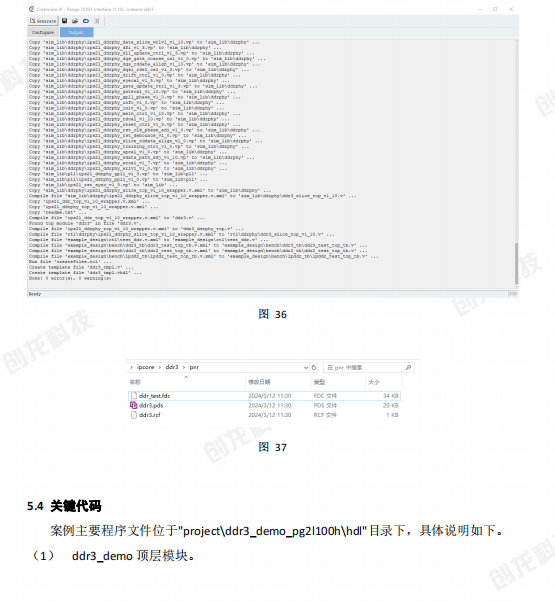

(6)打印如下信息,无错误,无警告,表示成功,并在工程"ipcore\ddr3\pnr\"目录下 生成对应的工程文件。

5.4关键代码

案例主要程序文件位于"project\ddr3_demo_pg21100h\hdl"目录下,具体说明如下

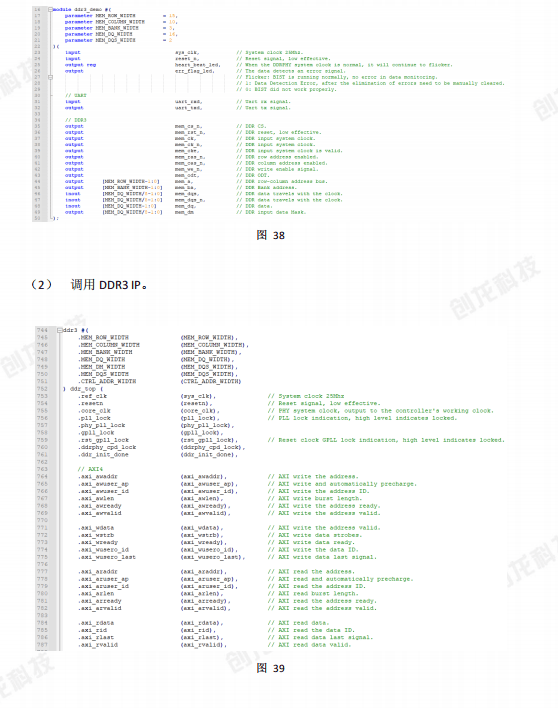

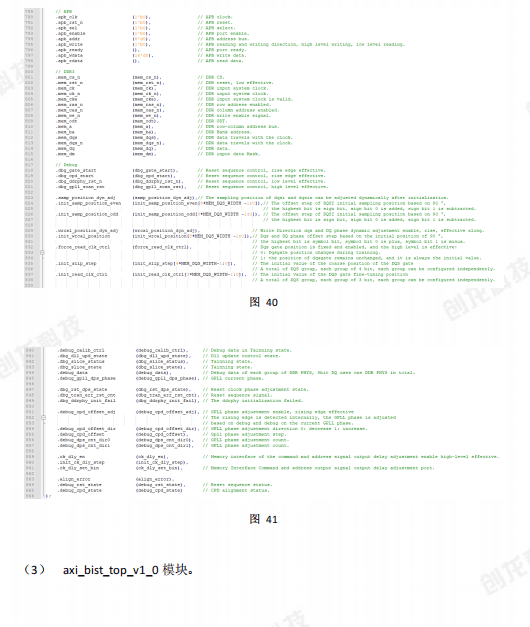

(1)ddr3_demo顶层模块。

(2)调用DDR3 IP。

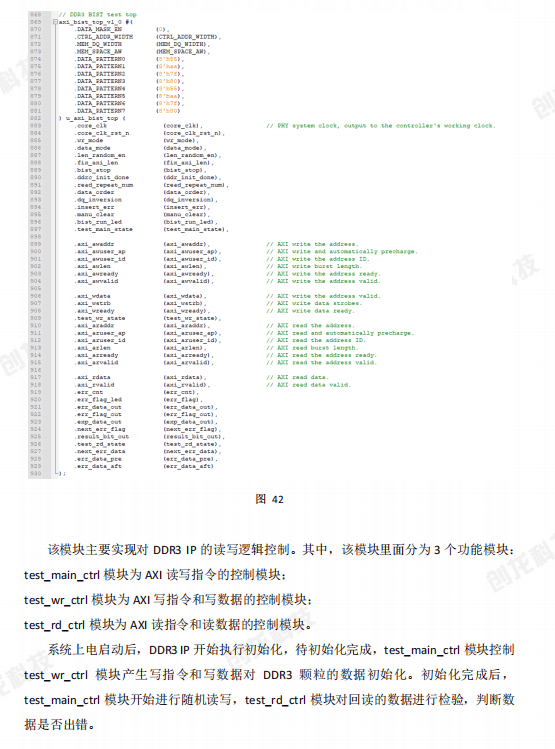

(3)axi_bist_top_v1_0模块。

该模块主要实现对DDR3 IP的读写逻辑控制。其中,该模块里面分为3个功能模块: test_main_ctrl模块为AXI读写指令的控制模块 test_wr_ctrl模块为AXI写指令和写数据的控制模块: test_rd_ctrl模块为AXI读指令和读数据的控制模块。

系统上电启动后,DDR3 IP开始执行初始化,待初始化完成,test_main_ctrl模块控制 test_wr_ctrl模块产生写指令和写数据对DDR3颗粒的数据初始化。初始化完成后, test_main_ctrl模块开始进行随机读写,test_rd_ctrd模块对回读的数据进行检验,判断数 据是否出错。

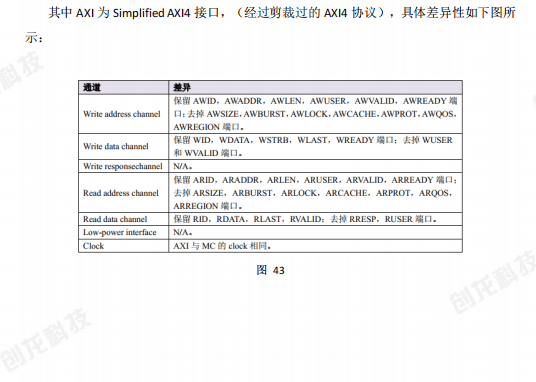

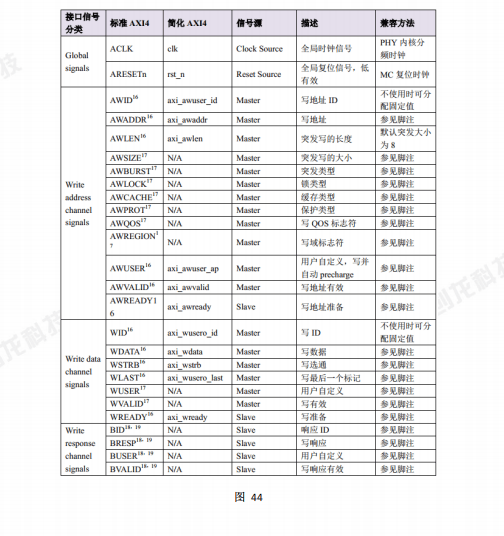

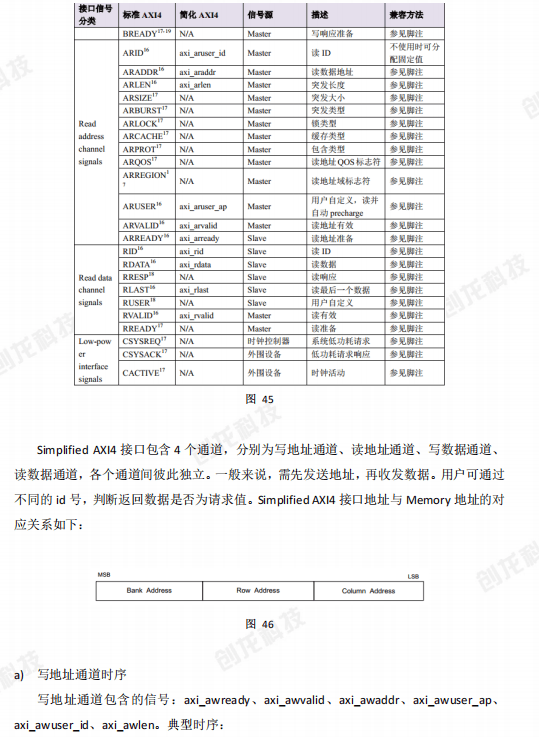

其中AXI为Simplified AX14接口,(经过剪裁过的AX14协议),具体差异性如下图所 示:

Simplified AX14接口包含4个通道,分别为写地址通道、读地址通道、写数据通道、 读数据通道,各个通道间彼此独立。一般来说,需先发送地址,再收发数据。用户可通过 不同的id号,判断返回数据是否为请求值。SimplifiedAX14接口地址与Memory地址的对 应关系如下:

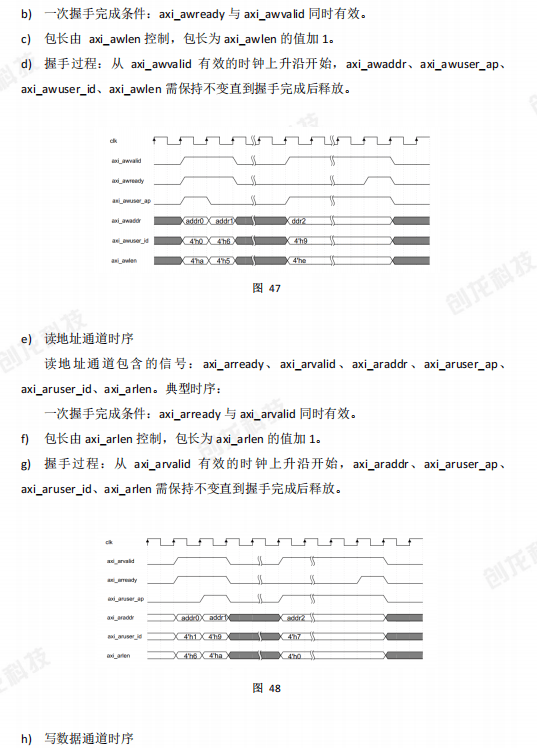

a)写地址通道时序

写地址通道包含的信号:axi_awready、axi_awalid、axi_awaddr、axi_awuser_ap、

axi_awuser_id、axi_awlen。典型时序:

b)一次握手完成条件:axi_awready与axi_awvalid同时有效。

c)包长由axi_awlen控制,包长为axi_awlen的值加1。

d)握手过程:从axi_awwalid有效的时钟上升沿开始,axi_awaddr、axi_awuser_ap、 axi_awuser_id、axi_awlen需保持不变直到握手完成后释放。

e)读地址通道时序

读地址通道包含的信号:axi_arready、axi_arvalid、axi_araddr、axi_aruser_ap、

axi_aruser_id、axi_arlen。典型时序:

一次握手完成条件:axi_arready与axi_arvalid同时有效。

f)包长由axi_arlen控制,包长为axi_arlen的值加1。

g)握手过程:从axi_arvalid有效的时钟上升沿开始,axi_araddr、axi_aruser_ap、 axi_aruser_id、axi_arlen需保持不变直到握手完成后释放。

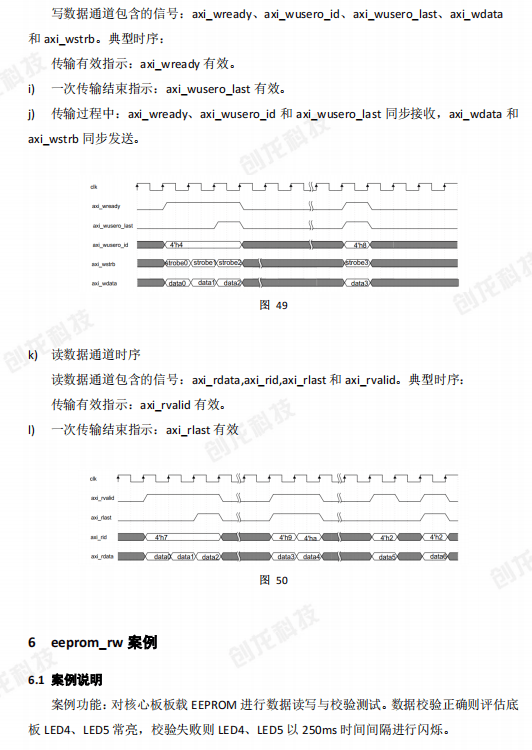

h)写数据通道时序

写数据通道包含的信号:axi_wready、axi_wusero_jd、axi_wusero_last、axi_wdata

和axi_wstrb。典型时序:

传输有效指示:axi_wready有效。

) 一次传输结束指示:axi_wusero_last有效。

j) 传输过程中:axi_wready、 axi_wusero_jid和axi_wusero_last 同步接收,axi_wdata和 axi_wstrb 同步发送。

k) 读数据通道时序

读数据通道包含的信号:axi_rdata,axi_rid,axi_rlast和axi_rvalid。典型时序:

传输有效指示:axi_rvalid 有效。

1) 一次传输结束指示:axi_rlast有效

6 eeprom_rw案例

6.1 案例说明

案例功能:对核心板板载EEPROM 进行数据读写与校验测试。数据校验正确则评估底

板LED4、LED5常亮,校验失败则LED4、LED5以250ms时间间隔进行闪烁。

管脚约束可查看案例"project\eeprom_W_pg2kxxh\constraints\eeprom_w.fdc"文件。

6.2案例测试

请运行程序,此时可看到评估底板LED4、LED5常亮,说明核心板板载EEPROM数据 读写、校验正常。

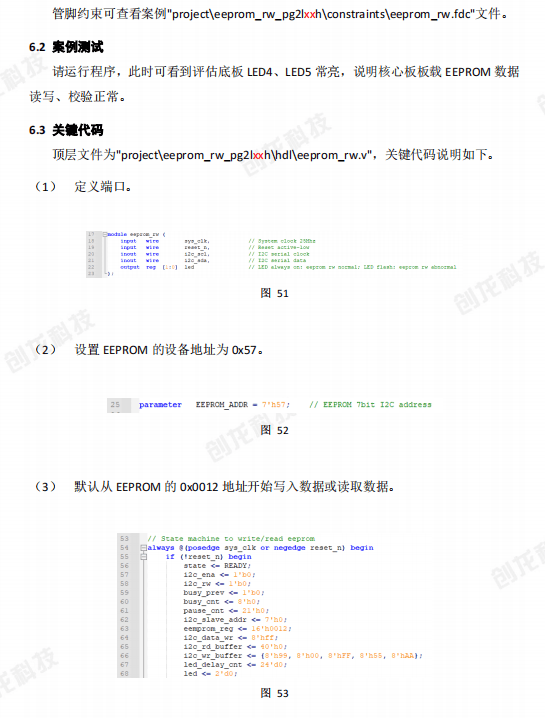

6.3关键代码

顶层文件为"project\eeprom_rw_pg2boch\hdl\eeprom_rw.v",关键代码说明如下。

(1)定义端口。

(2)设置EEPROM的设备地址为0x57。

(3)默认从EEPROM的0x0012地址开始写入数据或读取数据。

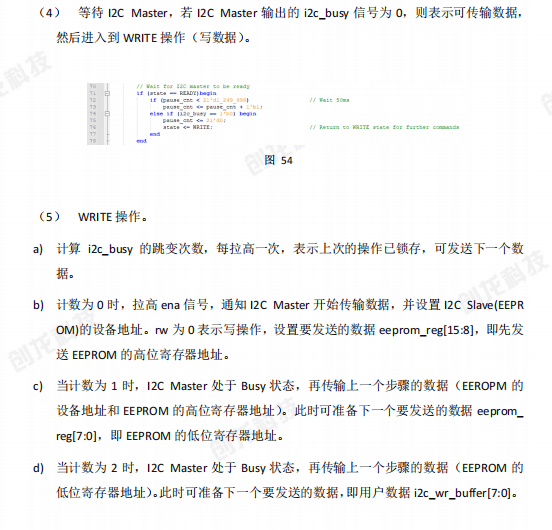

(4)等待I2C Master,若I2CMaster输出的i2c_busy信号为0,则表示可传输数据 然后进入到WRITE操作(写数据)。

(5)WRITE操作。

a)计算i2c_busy的跳变次数,每拉高一次,表示上次的操作已锁存,可发送下一个数 据。

b)计数为0时,拉高ena信号,通知12C Master开始传输数据,并设置I2C Slave(EEPR

OM)的设备地址。rw为0表示写操作,设置要发送的数据eeprom_reg[15:8],即先发 送EEPROM的高位寄存器地址。

c)当计数为1时,I2C Master处于Busy状态,再传输上一个步骤的数据(EEROPM的 设备地址和EEPROM的高位寄存器地址)。此时可准备下一个要发送的数据eeprom_

reg[7:0],即EEPROM的低位寄存器地址。

d)当计数为2时,12C Master处于Busy状态,再传输上一个步骤的数据(EEPROM的 低位寄存器地址)。此时可准备下一个要发送的数据,即用户数据i2c_wr_buffer[7:0]。

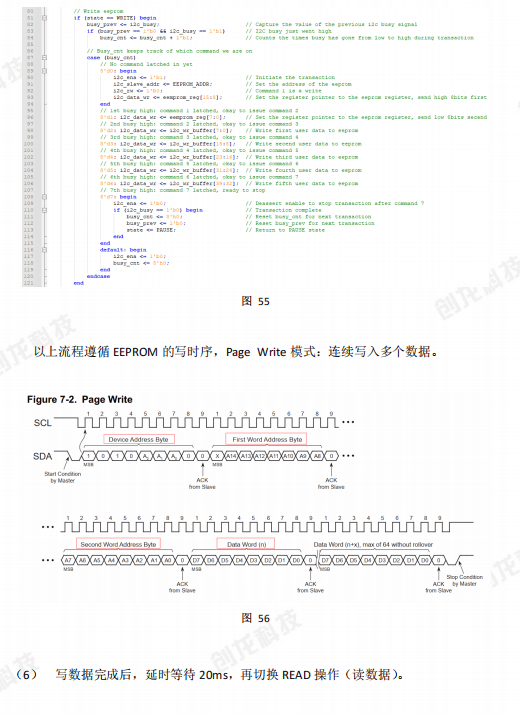

以上流程遵循EEPROM的写时序,Page Write模式:连续写入多个数据。

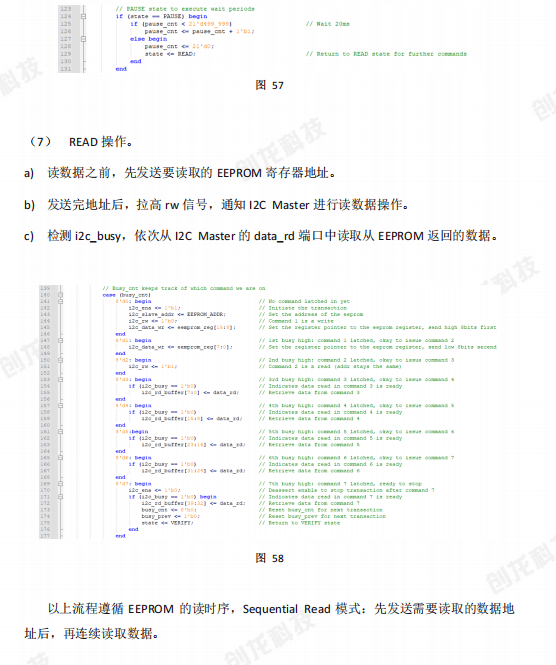

(7)READ操作。

a)读数据之前,先发送要读取的EEPROM寄存器地址。

b)发送完地址后,拉高rw信号,通知12C Master进行读数据操作。

c)检测i2c_busy,依次从12C Master的data_rd端口中读取从EEPROM返回的数据。

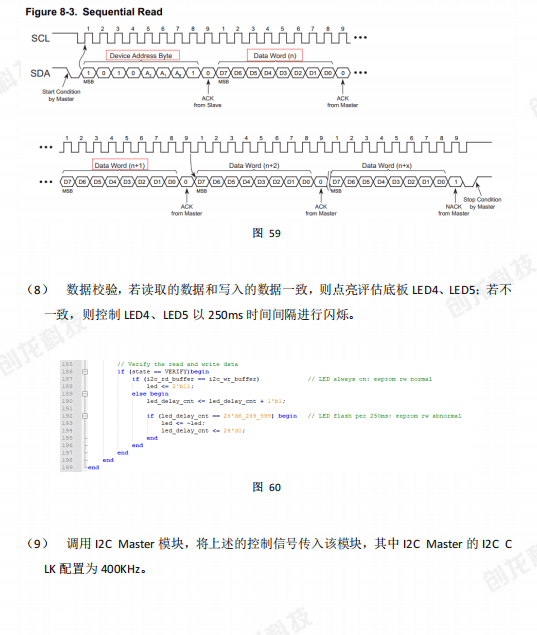

以上流程遵循EEPROM的读时序,Sequential Read模式:先发送需要读取的数据地 址后,再连续读取数据。

(8)数据校验,若读取的数据和写入的数据一致,则点亮评估底板LED4、LED5:若不 一致,则控制LED4、LED5以250ms时间间隔进行闪烁。

(9)调用12C Master模块,将上述的控制信号传入该模块,其中12C Master的12C C LK配置为400KHz。

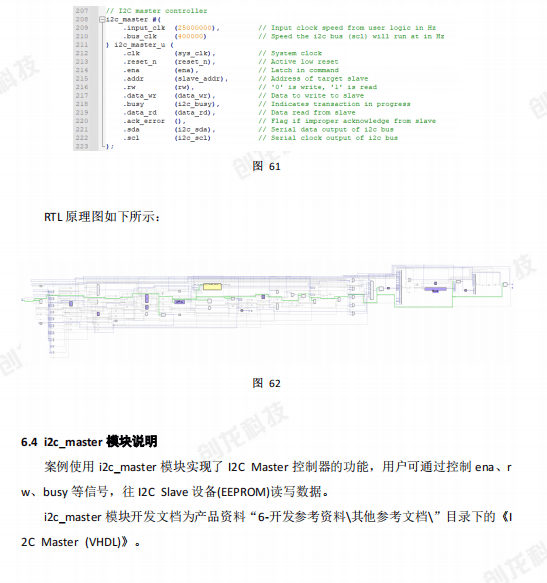

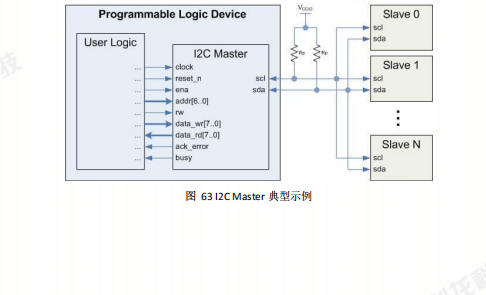

6.4 i2c_master模块说明

案例使用i2c_master模块实现了I2C Master控制器的功能,用户可通过控制ena、r w、busy等信号,往12C Slave设备(EEPROM)读写数据。

i2c_master模块开发文档为产品资料“6-开发参考资料\其他参考文档\”目录下的《 2C Master (VHDL)》。

/4

/4

文章评论(0条评论)

登录后参与讨论