承接上篇 “ 高频治具设计的现况与未来”文章之后,接下来接续的此篇文章将会对测试时所遇到的实际案例来与大家分享,藉以说明PCB治具设计过程中有可能被忽略掉的细节以及所需考虑的要点,验证百佳泰在高频治具设计上所积累的设计经验,而上一篇的高频治具设计的现况与未来文章中有提到百佳泰依据经验在高频测试时最常发生的五点Potential Risks:

A. Impedance not matching 阻抗不匹配

Ø 阻抗匹配(Impedance matching)是指为了使信号功率能从信号源(source)到负载(load)端得到最有效的传递,让信号在传递过程中尽可能不发生反射现象。

Ø 阻抗若不匹配时,会发生反射、造成能量与信号无法完整传递,以及辐射干扰等不良影响。

B. Crosstalk 串音干扰

Ø 两条信号线之间的耦合干扰现象,可分为近端及远程串音。

Ø 串音干扰发生时,会影响信号完整性。

C. Attenuation衰减

Ø 高频信号由Source传递至Load,传输过程信号的损失。

D. Return Loss 反射损失

Ø 高频信号因阻抗不匹配造成输入信号反射的现象。

E. ACR (Attenuation to Crosstalk Ration)衰减串音比

Ø 远程串音与衰减的差值。

Ø 当ACR发生时,即代表Crosstalk与Insertion Loss可能也有相应的问题发生,造成信号完整性可能会有所影响以及信号效率降低的不良情况产生。

百佳泰高频治具测试实际案例:

为协助您的产品从开发初期到上市都能拥有良好的质量,百佳泰搜集了实际测试中最常发生问题的以下三个Potential Risks,以此作为分享:

-Impedance not matching 阻抗不匹配

-Attenuation衰减

-Crosstalk 串音干扰

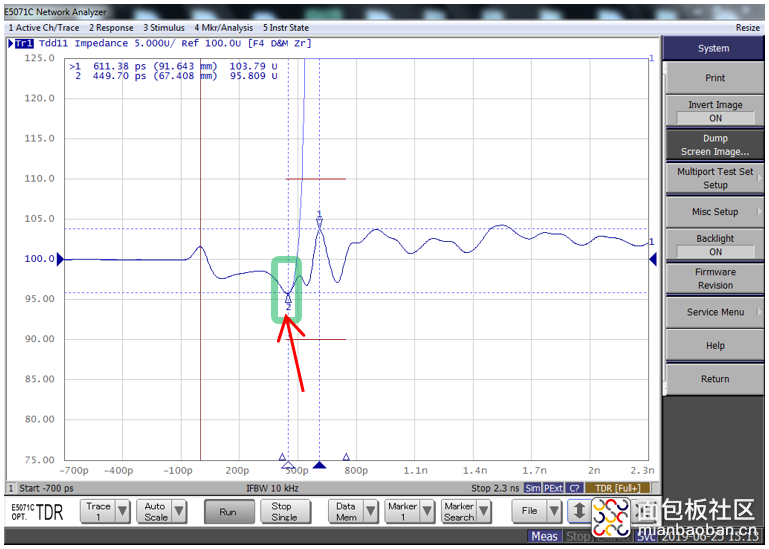

案例 1: A公司的HDMI 2.1 Receptacle Connector测试时,Receptacle端的CLK Trace阻抗就算为95.809Ω,但Insertion Loss表现不见得为佳。

Impedance: 95.809Ω(改善前):

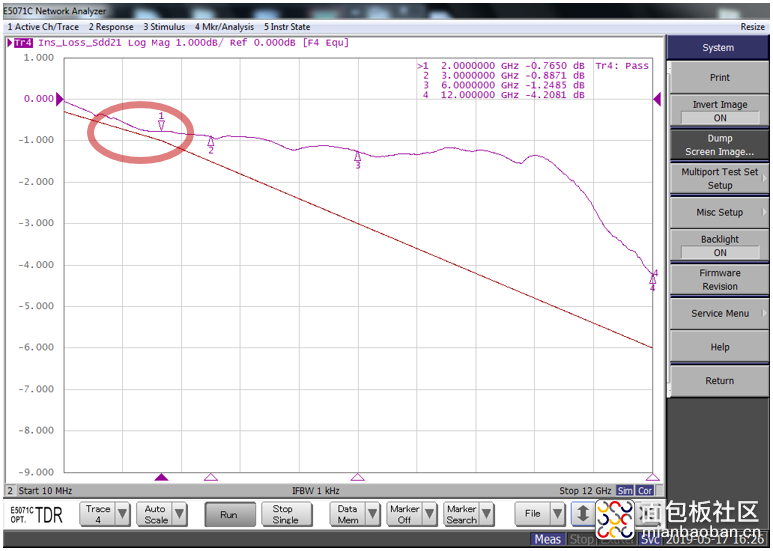

Insertion Loss(改善前):

解决方案: 如同上一篇文章所说过的第2点,客户连接器加工方式所造成的Insertion Loss影响,重新检视Receptacle端的焊接问题,即有所改善,所谓眼见不一定为凭,即为此例。

Insertion Loss(改善后):

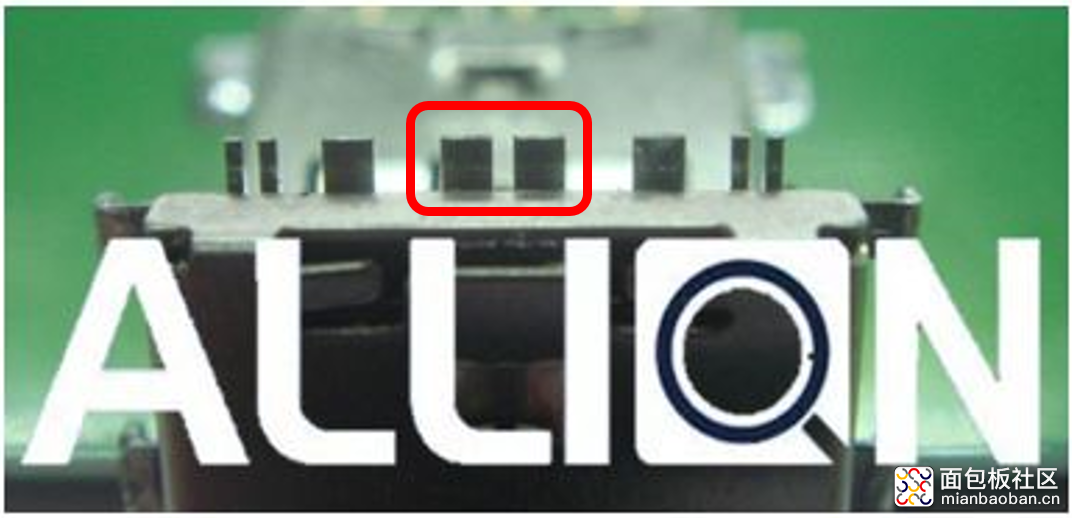

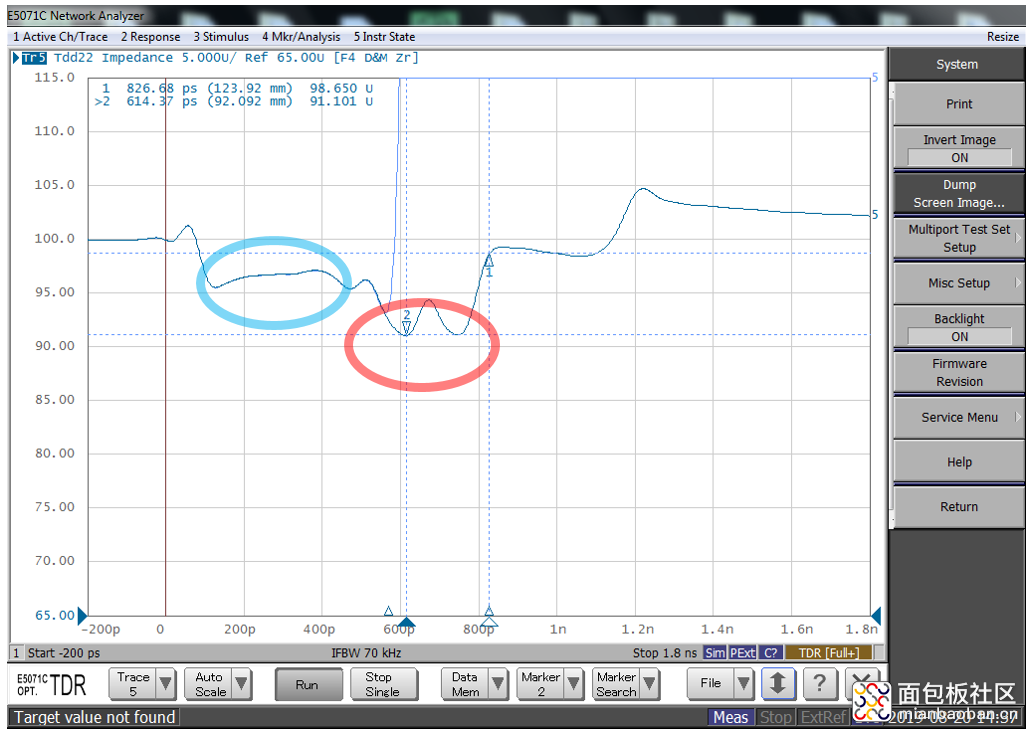

案例 2: B公司的USB3.0 Type A Receptacle connector 其D+ & D- pin SMD pad面积大,焊接时更要注意阻抗匹配的问题,否则容易造成接触面Impedance偏低的状况发生。

D+ & D- connector pin:

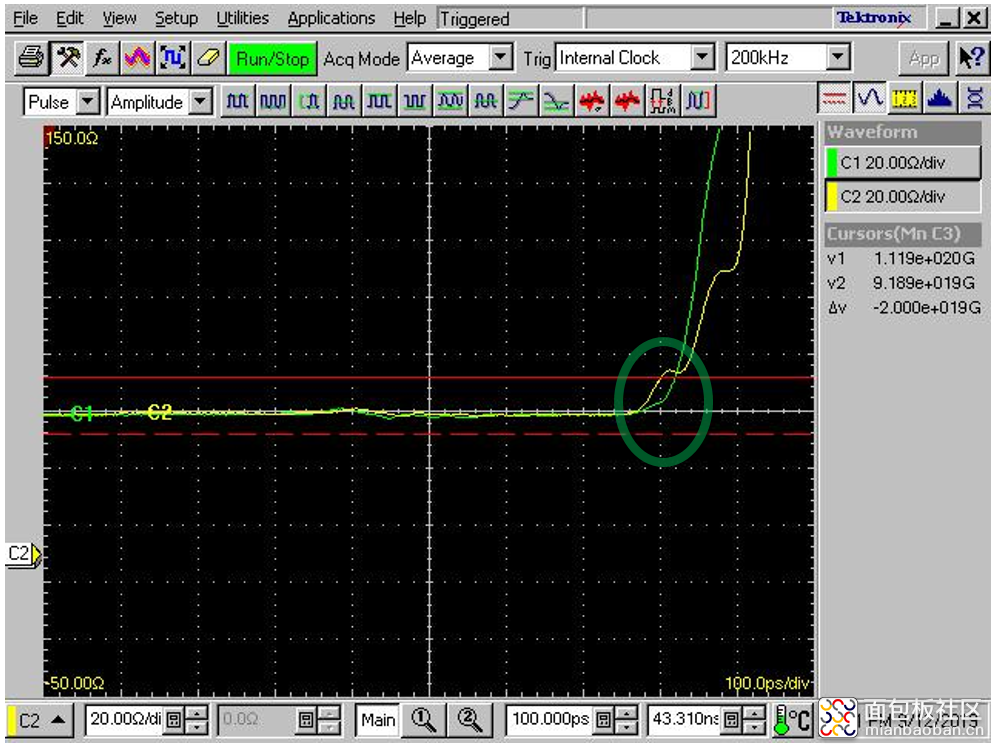

改善前:

解决方案: 此例的焊锡量要少,并确保connector pin与PCB pad平贴,才能减低connector pin与PCB pad接触面 阻抗不匹配的情况发生。

改善后:

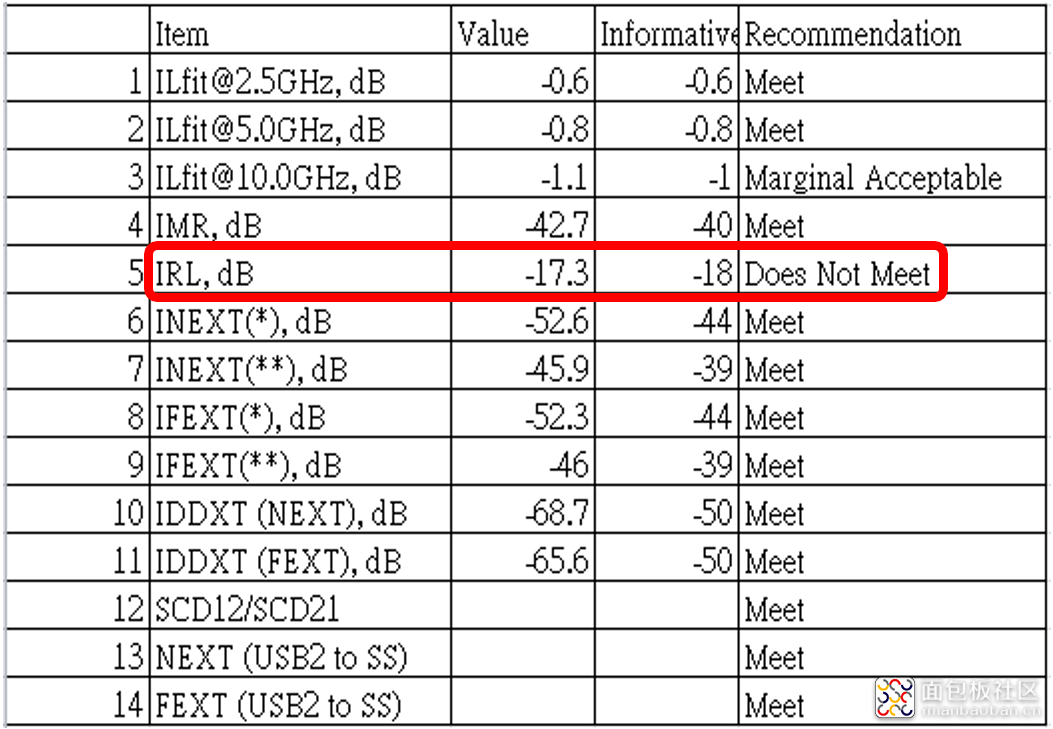

案例 3: C公司的TBT3的 Receptacle connector其RX2_P & RX2_N IRL(Integrated Return Loss)在标准附近未过,PCB阻抗设计或是connector内部设计都有可能是原因之一。

未达标准:

改善前:

解决方案: 经过比对确认,此案例虽然Trace设计阻抗为50Ω,但实际状况下阻抗却不见得会落在50Ω左右,故设计时可提高PCB设计阻抗以避免此风险。

改善后:

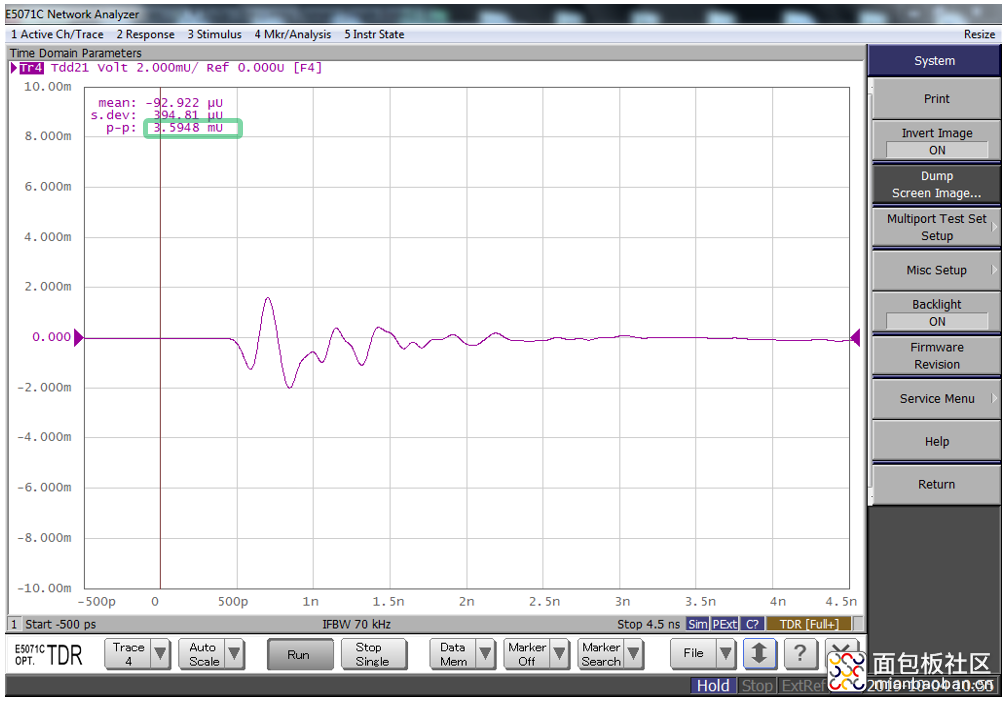

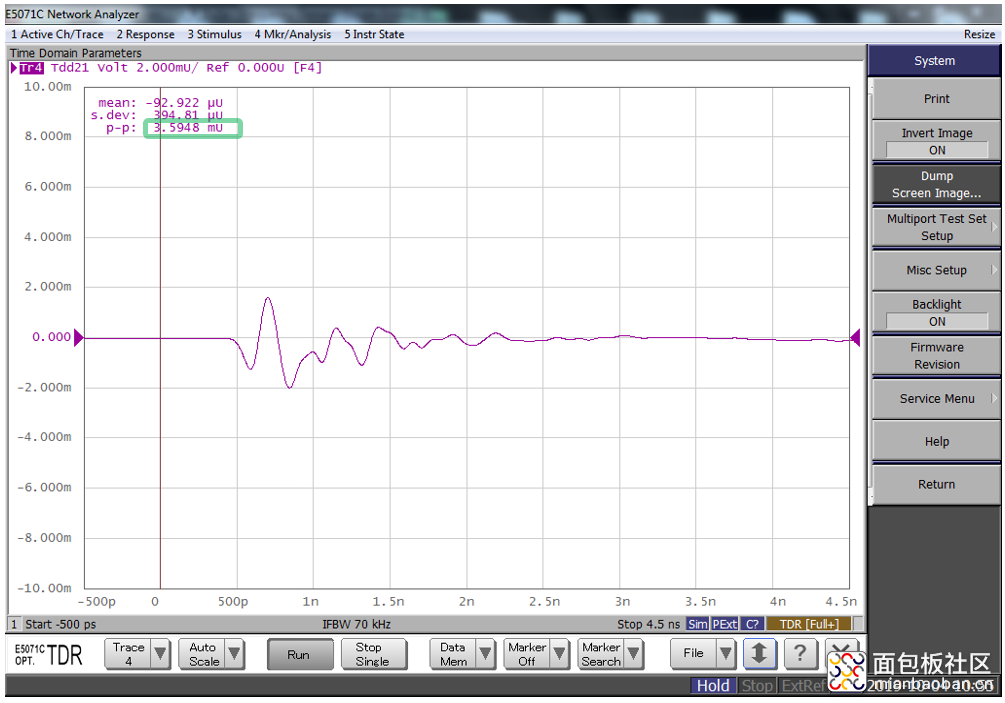

案例 4: D公司的USB3.0 Type A Receptacle connector 设计为pin脚为深入铁壳内的设计,测试过后此设计会造成Near End Crosstalk(SS:TX/RX)超过协会规范(3.6mV)而fail。

B 公司的连接器:

改善前: 4.1906mV

解决方案: 经过验证,其问题点为铁壳内部的GND所造成,加强内外部铁壳与PCB GND连接其信号完整性才会提高而通过规范。

改善后: 3.5948mV

全方位高频治具设计与测试服务

通过以上所举例出的的四个案例,都显示出高频设计上的一些不能轻忽的要点,从设计规划、治具焊接、再到加工方式,每一步的操作都会影响到高频性能。尤以焊接部分为例,轻则影响信号表现,重则阻抗不匹配或是IL 以及RL不佳而使高频信号失真,这是在高频版设计上所不能轻忽的。

/5

/5

curton 2020-1-10 19:49