引言

在逻辑电路中,为了克服短沟道效应,场效应晶体管(FET)从平面FET变为FinFET。以对于FinFETs的缩放,增加鳍高度以增加沟道宽度。然而,抑制模式倾斜对于进一步增加高度变得至关重要。 由于栅极(GAA)fe可以获得更大的沟道宽度,所以其应用比FinFETs更广泛。对于选择性SiGe蚀刻硅,目前湿法和干法蚀刻已被广泛研究。与湿法蚀刻相比,干法蚀刻在减圆方面具有优势。然而,圆的形成机理尚未阐明,了解这一机理对进一步还原圆具有重要意义。

实验与讨论

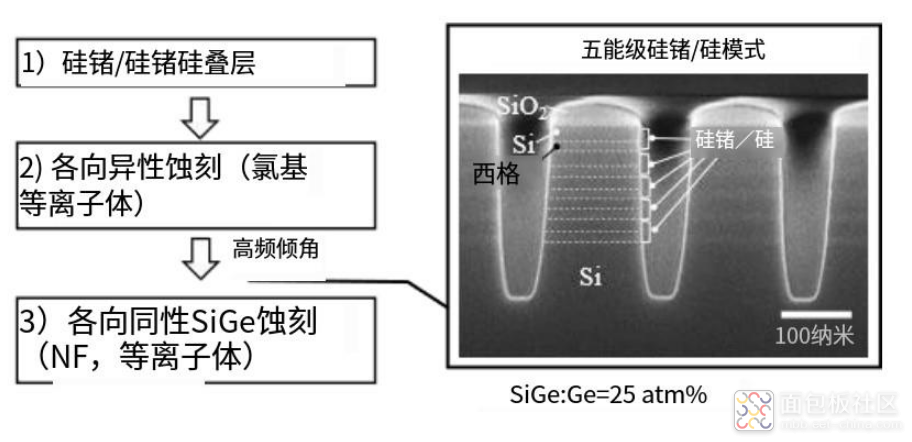

实验程序如图1所示。首先,对SiGe/Si堆叠层进行外延生长,并在这个SiGe/Si堆栈上创建了二氧化硅(sio2)空间图案。然后用氯气(cl2)基等离子体和电子回旋共振等离子体(ECR)蚀刻器对SiGe/Si堆栈进行各向异性蚀刻,并创建了5级堆叠的SiGe/Si图案。

在各向异性蚀刻过程中,英思特利用晶片偏置功率为450 W的高离子能量获得了垂直蚀刻轮廓。然后,在各向同性SiGe蚀刻之前,将这些图案浸在氟化氢水溶液(HF浸渍)中以去除天然氧化层。最后,使用无晶片偏置功率的ECR蚀刻器进行各向同性SiGe蚀刻。

图1:5层堆叠硅图案制备实验程序

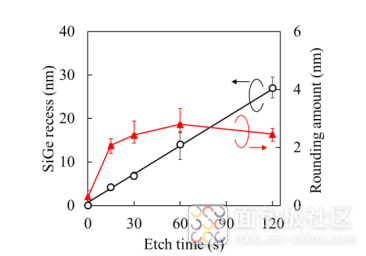

接下来,英思特利用透射电镜研究SiGe凹槽和圆化量对蚀刻时间的依赖性。图2显示了从15秒到120秒的不同蚀刻时间的结果。SiGe凹陷随时间的增加呈线性增加。这表明SiGe层是被三氟化氮等离子体连续蚀刻的。然而,随着刻蚀时间的增加,圆化量增加,并在15s后在约2.5 nm处饱和。这表明圆化主要形成于各向同性SiGe蚀刻的初始阶段,即蚀刻时间小于15s。我们还改变了同位素蚀刻条件,即增加工艺压力和增加晶片温度,并创建了一个超过20nm的SiGe凹槽。然而,在所有的蚀刻条件下,圆化量都在2.4~2.8nm范围内,由于各向同性的蚀刻条件,几乎保持不变。由此,得出圆化的主要原因不是由于各向同性蚀刻,而是它之前的过程导致的。

图2:各向同性SiGe蚀刻过程中SiGe凹槽和圆角量的蚀刻时间依赖性

结论

英思特研究了各向同性GAA-FET蚀刻后形成的圆机理。我们发现,SiGe/Si图案的圆化主要形成于各向同性SiGe刻蚀的初始阶段。根据这些结果,英思特提出了一个形成模型,在该锗层中,Ge的组成在各向同性刻蚀之前具有梯度,而由Ge组成引起的SiGe刻蚀速率的差异导致了圆化,各向同性蚀刻前凝胶层的形成是各向同性SiGe蚀刻后圆化形成的主要原因之一。

江苏英思特半导体科技有限公司主要从事湿法制程设备,晶圆清洁设备,RCA清洗机,KOH腐殖清洗机等设备的设计、生产和维护

/3

/3

文章评论(0条评论)

登录后参与讨论