全局时钟网络的特点:

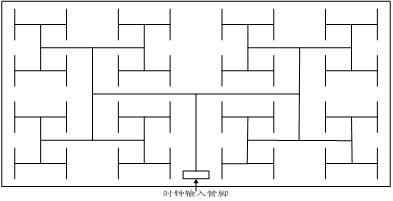

为了保证到芯片的各个角落的延时尽量相等,时钟分配树首先是走到芯片的中间,再向芯片的四周分布,如图所示。所以从时钟的源端到所驱动的触发器走过的路径比较长,延时比较大,但是到各个时序元件(触发器)时钟输入端等长,保证时钟偏斜(Tskew)很小。同时全局时钟网络局具有很强的驱动能力,而且在芯片设计的时候对时钟网络做了保护,尽量防止芯片内部的信号对时钟信号质量有影响,这样可以保证时钟信号引入的抖动(Tjitter)非常小。

要注意的一点就是:在Altera的FPGA内部具有多个全局时钟网络,在高端的FPGA(如Stratix)内部还有一些区域时钟,这些区域时钟只能驱动FPGA内部的某个区域内的逻辑,比如一个象限或者半个芯片,不能走到全片,在使用时需要注意。

/3

/3

文章评论(0条评论)

登录后参与讨论