500多名赛灵思设计工程师,历经4 年的研发时间,并有20余家IP和EDA合作伙伴参与产品研发和近百家客户参与了长达一年的试用版本测试,被赛灵思(Xilinx)称为可编程颠覆之作的 Vivado 设计套件终于走向前台,并通过其早期试用计划开始向客户隆重推出。赛灵思公司全球高级副总裁,亚太区执行总裁汤立人表示,Vivado 设计套件是面向未来十年 “All Programmable”器件而精心打造的,Vivado 设计套件要解决的实质问题,就是致力于加速其设计生产力,既加速IP集成、加速实现,使生产力加倍。

图一,赛灵思公司全球高级副总裁,亚太区执行总裁汤立人。

“All Programmable”器件时代

汤立人称,新的Vivado 设计套件是面向未来十年 “All Programmable”器件而精心打造。那么“All-Programmable”器件具体是指什么?汤立人解释,就 28nm 工艺而言,赛灵思开发出了许多类型的可编程技术,从逻辑和 I/O、软件可编程 ARM 处理系统、3D-IC、模拟混合信号(AMS)、系统到 IC 设计工具以及 IP 等。赛灵思将上述可编程技术进行不同组合,然后集成到”All-Programmable”器件中,如目前发货的基于堆叠硅片互联技术 (SSIT) 的 Virtex-7 2000T FPGA 和 Zynq-7000 可扩展处理平台 (EPP) 以及支持高级模拟混合信号(AMS)、高性能 SERDES 和 PLL 到可编程数据转换器资源的 FPGA。

总之,这是一个全面的系统级的器件。 “未来“All Programmable”器件要比可编程逻辑设计更多。他们将是可编程的系统集成,投入的芯片越来越少,而集成的系统功能却越来越多。”

汤立人还表示,在利用“All Programmable”器件创建系统的时候,设计者所面临的是一套全新的集成和实现设计生产力的瓶颈问题。一方面从集成的角度讲,其中包括集成算法C和寄存器传输级(RTL)的IP;混合了DSP、嵌入式、连接和逻辑域;验证模块和“系统”,以及设计和IP的重用等。实现的瓶颈包括芯片规划和分层;多领域和大量的物理优化;多元的“设计”与“时序”收敛;和后期的ECO和设计变更的连锁效应。正是为了解决集成和实现的瓶颈,使用户能够充分利用这些“All Programmable”器件的系统集成能力,赛灵思打造了全新Vivado设计套件。

Vivado设计套件是什么?

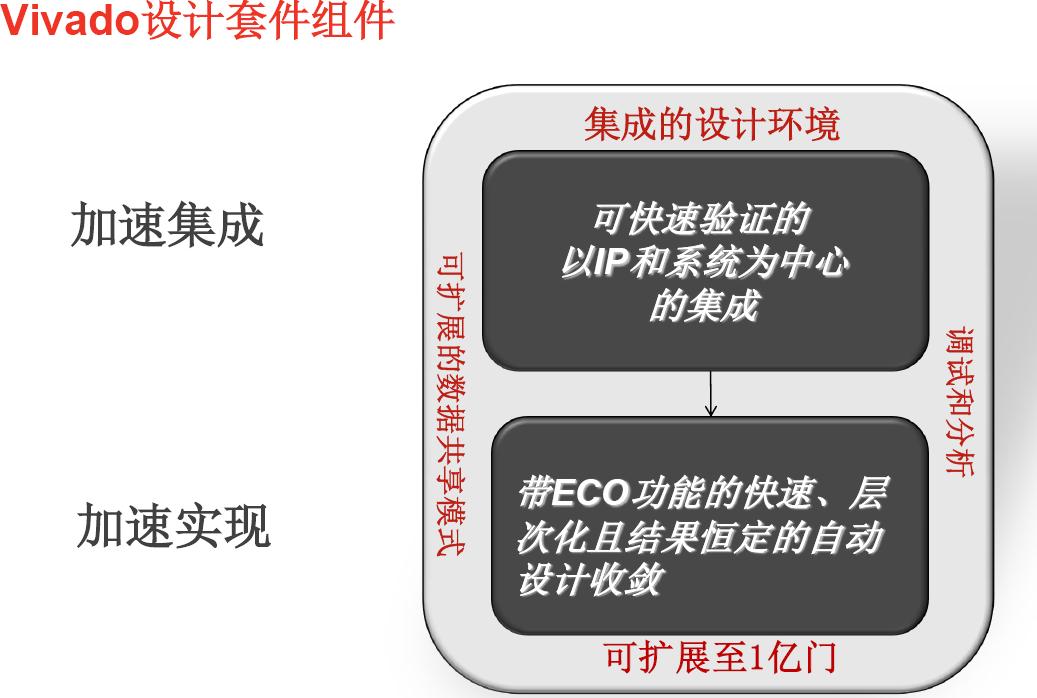

Vivado 设计套件包括高度集成的设计环境和新一代从系统到 IC 级的工具,这些均建立在共享的可扩展数据模型和通用调试环境基础上。这也是一个基于 AMBA AXI4 互联规范、IP-XACT IP 封装元数据、工具命令语言 (TCL)、Synopsys 系统约束 (SDC) 以及其它有助于根据客户需求量身定制设计流程并符合业界标准的开放式环境。赛灵思构建的Vivado 工具将各类可编程技术结合在一起,能够可扩展实现多达 1 亿个等效 ASIC 门的设计。

图二,Vivado 设计套件加速集成和实现,能够可扩展实现多达 1 亿个等效 ASIC 门的设计。

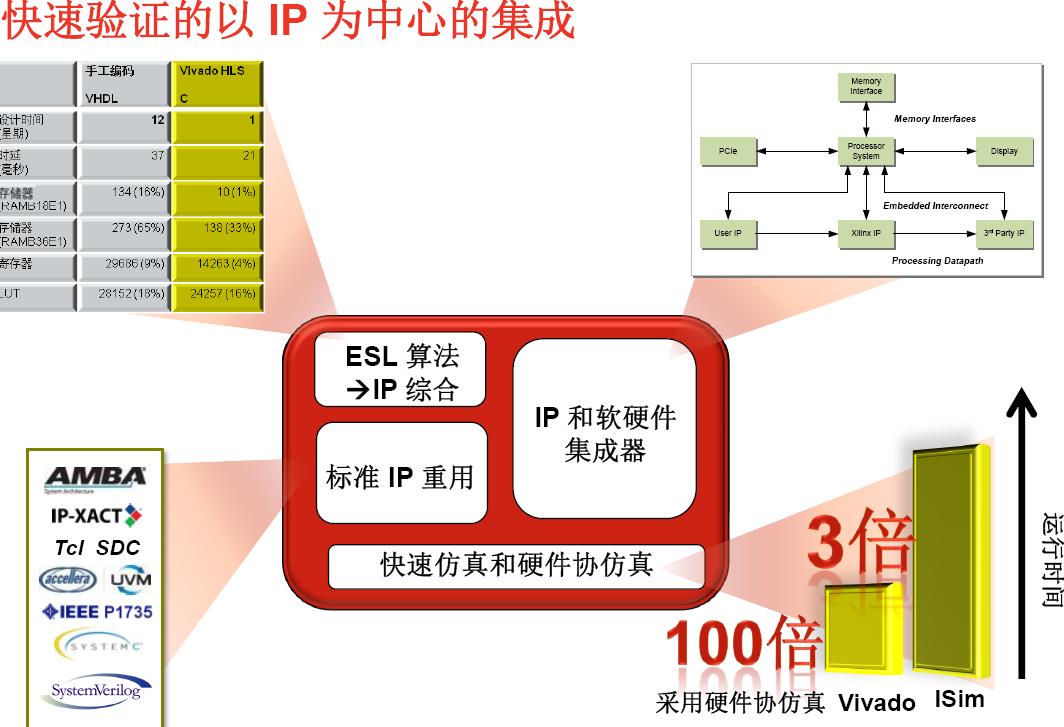

为了解决集成的瓶颈问题,Vivado 设计套件采用了用于快速综合和验证 C 语言算法 IP 的 ESL 设计,实现重用的标准算法和 RTL IP 封装技术,标准 IP 封装和各类系统构建模块的系统集成,模块和系统验证的仿真速度提高了3 倍,与此同时,硬件协仿真将性能提升了100倍。

图三,模块和系统验证的仿真速度提高3倍,硬件协仿真将性能提升了100倍。

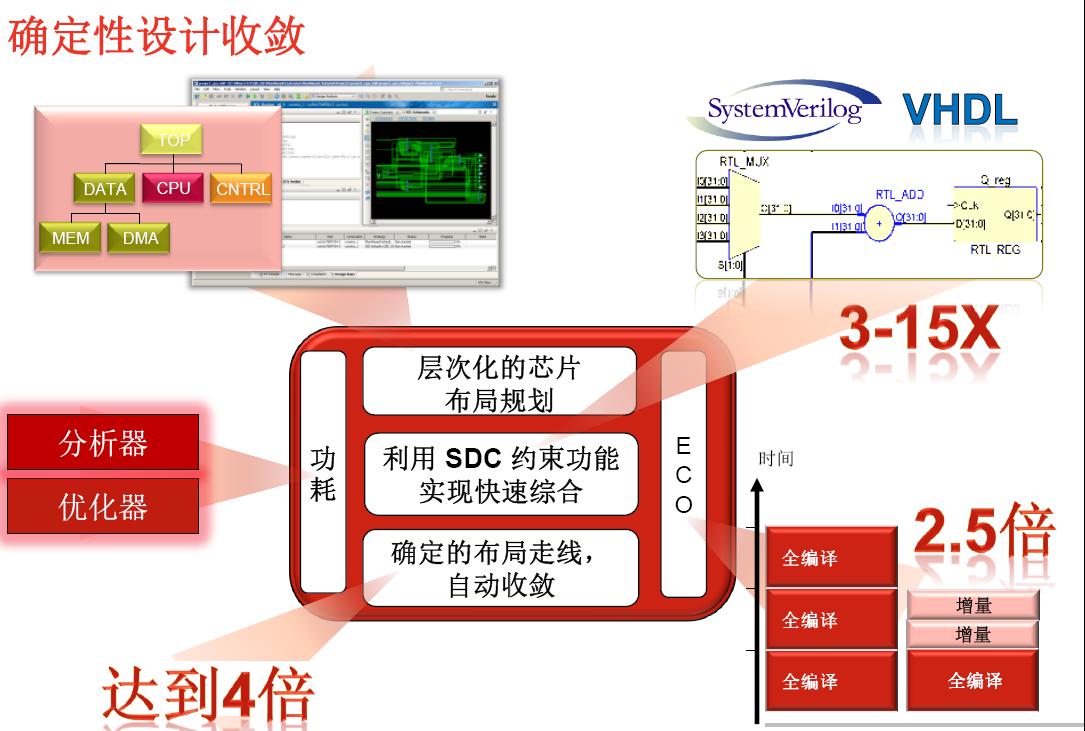

为了解决实现的瓶颈,Vivado工具采用层次化器件编辑器和布局规划器、速度提升了3 倍~15 倍,且为 SystemVerilog 提供了业界最好支持的逻辑综合工具、速度提升 4 倍且确定性更高的布局布线引擎,以及通过分析技术可最小化时序、线长、路由拥堵等多个变量的“成本”函数。此外,增量式流程能让工程变更通知单 (ECO) 的任何修改只需对设计的一小部分进行重新实现就能快速处理,同时确保性能不受影响。最后,Vivado 工具通过利用最新共享的可扩展数据模型,能够估算设计流程各个阶段的功耗、时序和占用面积,从而达到预先分析,进而优化自动化时钟门等集成功能。

图四,Vivado工具采用层次化器件编辑器和布局规划器、速度提升 了3 倍~ 15 倍。

Vivado 工具能解决当前哪些主要挑战?

“All Programmable”器件不只是涵盖可编程逻辑设计,还涉及到可编程系统集成,要在更少的芯片上集成越来越多的系统功能。为了构建上述系统,工程师们都会面临着一系列全新的集成和实现设计生产力瓶颈,例如,集成 C 语言算法和 RTL 级 IP ,混合 DSP、嵌入式、连接功能、逻辑领域问题以及模块和“系统”验证和设计和 IP 重用 等问题。而赛灵思的Vivado 设计套件,采用层次化芯片布局规划与分区,多领域和多晶片物理优化,多变量“设计”和“时序”收敛的冲突和设计后期发生的ECO及变更引起的连锁反应等技术,很好地解决了这些瓶颈问题,Vivado 设计套件从总体上把集成度和实现速度提高至原来的4 倍。

Vivado设计套件相对ISE设计套件有何优势?

汤立人说,赛灵思早在 1997 年就推出了 ISE 设计套件。ISE套件采用了当时非常具有创新性的基于时序的布局布线引擎,这是1995 年 4 月赛灵思收购 NeoCAD 获得的。在其后 15 年的时间里,随着 FPGA 能够执行日趋复杂的功能,赛灵思为 ISE 套件增添了许多新技术,包括多语言综合与仿真、IP 集成以及众多编辑和测试实用功能,努力不断从各个方面改进 ISE 设计套件。

汤立人表示,赛灵思通过借鉴 ISE 设计套件的所有经验、注意事项和关键技术,并充分利用最新的EDA 算法、工具和技术,才打造出了这一颠覆性的全新 Vivado 设计套件。Vivado 设计套件远远超越了赛灵思目前的ISE 设计套件。为帮助客户顺利过渡到Vivado 设计套件的使用,赛灵思将继续坚定地为采用 7 系列及更早期的赛灵思 FPGA 技术的客户提供 ISE 支持。今后 Vivado 设计套件将成为赛灵思的旗舰设计环境,支持所有 7 系列器件及赛灵思未来器件。

/4

/4

用户377235 2015-7-24 13:43

用户406329 2012-5-14 11:02

智慧,受益,推广到群用层的设计更好.

飞言走笔 2012-4-28 11:40