再谈ALTERA FIFO的读写控制

王敏志

概述

之前写过相同标题的文章,最近修改工程的时候翻看之前的文章,发现当时写的还不够透彻,故这次试图写得更清晰一点。

“读空”,这里的意思是指一种读已空FIFO的误操作。“写满”,这里是指一种继续往已满的FIFO写入数据的误操作。写文章的目的就是要在实际设计中如何避免这两种误操作。通常使用“almost”空和满能轻松达到控制FIFO读写操作的目的,但是本文笔者要谈论的是一种相对较特殊的FIFO应用。

为什么要读空FIFO?

注意这里的“读空”和上一节提到的“读空”误操作的区别,这里是指如何真正安全的将FIFO的数据一个不留的读出来。也即在没有后续数据写入的情况下,如何把FIFO里剩余的数据安全的一个不落地读出来。

至于为什么不用“almost”空标志信号控制FIFO,且要读空FIFO,是因为项目中数据流的特点决定的。系统有非常多路数据,而数据流又是随机的,后端需要根据时间信息来处理这些数据。所以如果是“almost”空标志信号就有可能在某种情况导致某些数据被“Blocked”在FIFO中很长时间,进而使得这些数据因为时间关系而失效,而这对系统来说是不允许的。所以系统要求数据要被“及时”并“安全”地读走。

如何防止“写满”

其实对于系统来说,用“半满”来控制FIFO的写是可以接受的。这里不用“半满”来控制写,只是为了探究一下如何安全地将FIFO写满,所以就要防止对已经被写满的FIFO再次写入数据,这里假定FIFO的深度是N。那么判决FIFO非满的条件就是USEDW小于N-1并且满标志“full”等于零,即低电平。

如何防止“读空”

这是本文的关键,即如何防止对已经空了的FIFO再次采取读操作。采取“读空”误操作的后果就是数据处理的时候所有FIFO最后读出的那个数据被处理了两次,这显然是不对的。

上一篇文章介绍了一种纠错方法,即判决FIFO非空的条件是USEDW大于0且空标志“empty”信号为0,除此之外或者当满标志信号“full”为1。但是上一篇文章也讲了,控制读有效信号的语句必须放在进城外面。其实效果就是empty为1的时候读信号绝对不能为1。

所以换一种在进程内的描述方法就是空标志“empty”为0成立且(相与)USEDW大于1或者满标志“full”信号为1二者有一成立即可。

另外,还有一种控制方法就是分两步,第一步根据空标志“empty”信号产生一个读操作的中间信号(其实就是将empty取反打一拍);第二步是将此中间信号和empty的反相与产生最终的读信号。

分析及结论

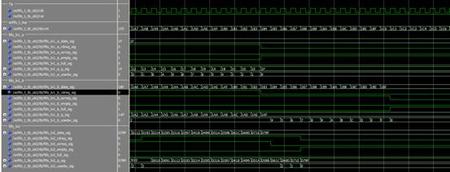

记录这些其实就是为了在实际使用FIFO的时候能够安全的操作FIFO,另外还有一个目的是为FIFO级联操作积累经验。下图是FIFO级联操作仿真结果,注意程序中已经按照上述分析进行“读空”和“写满”误操作的规避。

/5

/5

coyoo 2016-5-24 08:44

用户436615 2016-5-23 18:58