PLL那些事之乘除因子

王敏志

概述

PLL的基本概念可以在ALTERA的官方网站上找到详细的说明,这里引用一下里面的PLL框图用以更好的说明PLL的乘除因子。

图1:PLL框图

一个问题引出的PLL乘除因子的故事

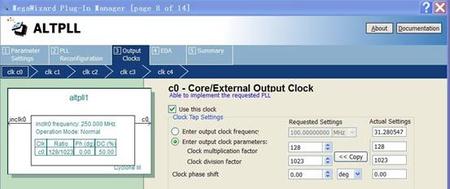

在研究基于FPGA的TDC的时候,为了产生一个相位与系统时钟尽量不相关的低速时钟来模拟hit,所以需要使用PLL来产生。如图2所示显示的是使用PLL产生一个31.280547MHz时钟,是由输入的250MHz时钟除以1023再乘以128得到。

图2:乘因子128,除因子1023

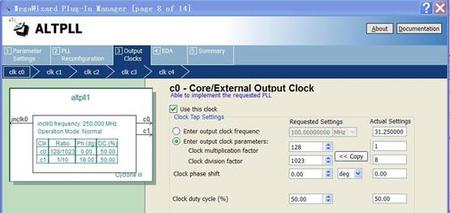

注意图2包含的两个细节,第一个是此时PLL只有一个输出信号;第二是此时器件选择的是Cyclone 3系列。这里的故事就是跟这两个细节有关系,即改变这两个条件里任何一个都有可能导致上述时钟无法产生。图3显示的是改变第一个条件造成的后果。即如果我需要增加一个PLL的输出的时候上述时钟无法产生,实际上QuartusII自动得到一个31.25MHz的时钟,即实际的乘除因子分别是1和8。

图3:增加PLL的输出数量使乘除因子设置受限

乘除因子的真相

其实我们在讲乘除因子的时候必须搞清楚PLL的几个counter,即M、N以及C计数器。首先我们可以确定的是Megawizard里“Clock multiplication factor”就等于M计数器的值,而“Clock division factor”等于N计数器的值乘以C计数器的值,这些可以从上述公式里找到答案。

在进行PLL例化设置的时候,Megawizard一般不提供,ALTERA也不建议客户去设置M、N以及C计数器,而是通过设置乘除因子来设置PLL,编译器会自动设置这些计数器的值。只有高级应用,即高级用户可以通过特殊方式来设置M、N以及C计数器来配置PLL。另外,应用ECO工具手动修改FPGA设计的时候也可以修改这些计数器以及其他参数。

故事问题的答案

上面那个故事给出两个条件,即不能多于1个PLL输出和更改器件选择。那么到底为什么呢?

首先介绍为什么不能多于1个PLL输出。其实也不是不能多于一个PLL输出,而是因为第一个时钟设置的乘除因子限制了获取其他时钟的配置参数。为什么这么说呢?因为PLL所有输出都是通过FVCO除以Ci(对应PLL输出端口的C计数器的Value)计数器产生的,上述例子中FVCO=250x128/31约等于1032.258MHz。而为了得到第一个时钟,M和N已经确定为128和31了,那么第二个时钟也必须依据这个M和N值来产生,所以后面的时钟频率不能随意产生了,而是有所限制。故图3中的c1在设置为25MHz的无法在c0上得到31.280547MHz这个特定时钟了。换句话说为了在c0上得到31.280547MHz这个特定时钟,这个PLL的剩下的输出端口的时钟频率就限制为(250x128/31*Ci)其中Ci的值为1到512。

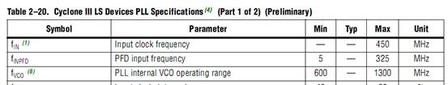

其次是为什么不能更改器件呢?其实也不是不能更改器件,而是当时31.280547这个频率限定了FVCO的值,即1032.258MHz。并且当时的情况是先在CIII的开发板上做实验,后面移植到了实际产品,而产品使用的器件是ArriaGX系列。查手册发现这两个器件的PLL的FVCO范围还不一样。如图4和图5所示。

图4:Cyclone 3中PLL的FVCO范围

图5:ArriaGX中PLL的FVCO范围

由图5可知,当换成ArriaGX以后显然无法再得到所需特定频率的时钟了。

用户377235 2013-3-6 23:42

coyoo 2013-2-1 13:12

用户403664 2013-2-1 11:55

coyoo 2013-1-4 18:24

coyoo 2013-1-4 11:56

用户39003 2007-12-20 14:01

用户104816 2007-3-29 17:48

有没有联系电话?修的如何啊?请联系我,13938230001

用户1053025 2006-12-11 12:46

用户1053025 2006-12-4 09:44