PLL那些事之core输出抖动(续2)

王敏志

分析及结论

图4到图28显示了不同的相移对应的测试结果,图的左边是对应HIT在延时线中的位置,而右边对应的是这些延时线单元在随机HIT测得的延时时间。将这些图中的结果总结到一张表中如表1所示。

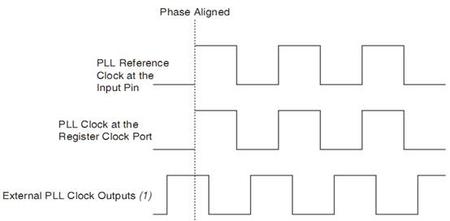

从表1可以看出所有不同相位测量结果的uncertainty的范围是84.4到241.7ps之间。这里之所以叫“uncertainty”而不是直接冠以jitter是因为这个数值范围是由两个时钟的uncertainty来决定的而非单一时钟决定,即这个测量结果应该由25MHz和250MHz这两个时钟的抖动共同来决定。如果我们不能证明25MHz和250MHz这两个时钟相位是严格对齐的,就不能直接将上述测量所得的结果简单地认为就是PLL的core输出jitter。前面我也有提到,25MHz时钟和250MHz时钟之间的相位关系只有一种组合,这是在相对宏观的角度来说,如果我们考虑到PLL内部引起的jitter,那么这个两个时钟沿是否还是严丝合缝的对齐呢?手册里似乎给出了一个唯一可以作为参考的答案,即在PLL的Normal Mode下PLL的时钟之间的相位关系图,如图29所示。

这里分析的基础就是假定如图29所示PLL的输入时钟和内部寄存器时钟的沿是严格对齐的,而我们实际也正好是使用Normal模式。有了这个基础我们再来分析这个最大uncertainty值范围,最小是84.4ps,最大达到241.7ps。仔细看这两个测量结果,发现84.4ps是相位偏移833ps的测量结果,直方图落在三个cell单元里,且三个cell的延时时间均较小,而这个最大值是相位偏移500ps时候的测量结果,直方图也是落在3个cell单元里,只是这三个cell单元中有个cell的延时时间超级大,我们称之为ultra-wide延时单元。另外,从表1同时可以看到相移333ps、1833ps、2333ps、3000ps、3333ps以及3667ps的测量结果直方图均落在一个cell里,而这些cell均为ultra-wide延时单元,察看这些ultra-wide延时单元的延时可以知道其最大延时时间为169.9ps,而其中最小的延时时间也有99.8ps。所以84.4ps可以认为是本实验测量到PLL的core输出最大的jitter值范围即±42.2ps。

图29:Normal Mode下PLL的时钟相位关系

/4

/4

文章评论(0条评论)

登录后参与讨论