PLL那些事之core输出抖动

王敏志

概述

这里的PLL是指ALTERA的FPGA内部的PLL,PLL的输出有两种,一种是core output,另外一种是external output,由于ALTERA只给出了PLL的输出到外部引脚的jitter,并没有给出PLL的core输出jitter,这里试图通过基于FPGA的TDC来量测一下该jitter。从ALTERA的器件手册只能查到PLL的external output的抖动参数,我们使用的ArriaGX系列,在输出时钟频率大于等于100MHz的时候只给出这个参数的最大值即250ps,当时钟频率低于100MHz的时候也只给出最大值,即25mUI。

为什么要了解PLL的core输出抖动呢?

在进行基于FPGA的TDC设计的时候系统时钟的抖动肯定会影响TDC的精度,这里的抖动(jitter)包括时钟源,即晶振,以及时钟分配器和PLL所产生的抖动。时钟分配器的抖动是可以查厂家手册获取,而且一般都很小,基本都是飞秒级别。由于在设计TDC的时候需要FPGA里的PLL倍频得到一个相对高速的时钟,那么PLL引入的jitter又是多少呢?ALTERA并没有给出答案。

测量方法

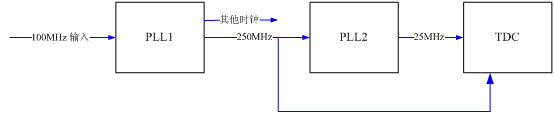

FPGA的输入时钟是100MHz,通过第一个PLL产生一个250MHz的时钟作为TDC的高速采样时钟,另外第二个PLL从250MHz降频得到一个25MHz的时钟作为TDC的输入HIT(如图1所示)。这个25MHz时钟跟TDC的高速采样时钟只有一种相位关系,所以可以通过PLL的移相功能大致量测出不同相位下该TDC的测量结果,再通过测量结果以及TDC的RAW BIN结果来进行分析。

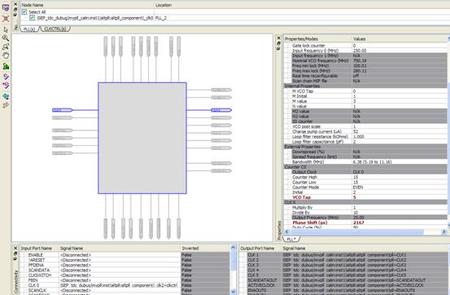

TDC的Raw BIN是通过外部随机HIT测量得到,另外,TDC的延时线位置进行了锁定,这样随机HIT Raw BIN和PLL产生的HIT测量的时候使用的是相同的延时线,这样尽量保证减小测量的误差。还有一点,是在更改PLL的HIT的相位的时候使用了ECO的方法(如图2所示),即手动修改,这样工程没进行重新全编译,只是进行了FIT,如此尽量保持了工程的一致性。

我们假定PLL的输出不存在jitter,那么TDC测量出来的结果肯定具有唯一性特点,即某个相位测出来的结果肯定只有一个值,这个可以通过直方图的方法轻易得出。前面的假设肯定是不成立的,所以直方图的结果就一定是某个中心值附件左右偏移,而我们所需要知道的就是这个偏移的大小即抖动(jitter)。

图1:测量示意图

图2:利用ECO手动修改PLL输出的相位

测量结果

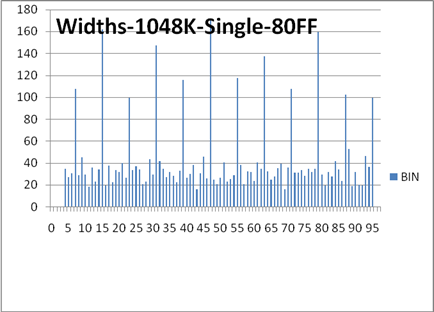

我们的TDC使用了128级延时线(delay-line),在使用PLL产生的HIT进行测量之前,我们使用随机HIT来测量该TDC(主要是延时线)的基本属性。图3显示的是延时线每一级延时单元的延时时间,这里我们称之为TDC的Raw BIN。

图3:TDC的Raw BIN

ArriaGX的PLL的VCO最大只能到840MHz,而从250MHz产生25MHz的时候,VCO只能是750MHz,所以最小相移是167ps(1/(750*8)ns)。那么从0相位开始每次步进167ps测试各个不同相位25MHz作为TDC输入HIT时的结果,由于250MHz的周期是4000ps,所以相移到4000ps即可完成一周测量。

/3

/3

coyoo 2013-3-12 11:38

coyoo 2013-3-12 11:25

用户403664 2013-3-12 09:14

用户1244064 2006-11-2 21:15