同步复位

所谓同步复位是基于这样的一个前提,即服务信号只是在寄存器时钟的有效沿时影响该寄存器的状态。同步的典型优点是它们能确保电路为百分百的同步电路。同步复位的另一个优点是它们的时序可以很容易被静态时序分析器比如Altera的TimeQuest分析器分析。由于同步复位信号是被时钟启动(Launch)和锁存(Latch),而启动和锁存的时钟彼此同步,所以复位信号的到达时间(Arrival time)和所需时间(Required time)就能很轻易的确定并进行正确的slack分析。同步复位还有一个优点是它们更易于仿真当它们作用于一些基于周期机制的功能模块时。

同步复位也有自己的缺点。例如,它们可能要求脉冲宽度满足一定要求,以保证在需要复位的时钟沿复位信号是有效的,所以这时候电路中也许需要脉冲延伸器或者说脉冲扩展器。也许更重要的是,同步复位总是需要一个时钟来完成对电路的复位。如果因为某些因素导致复位信号的启动时钟沿错误,那么就会导致整个电路复位功能的失败。

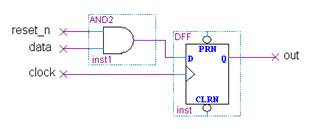

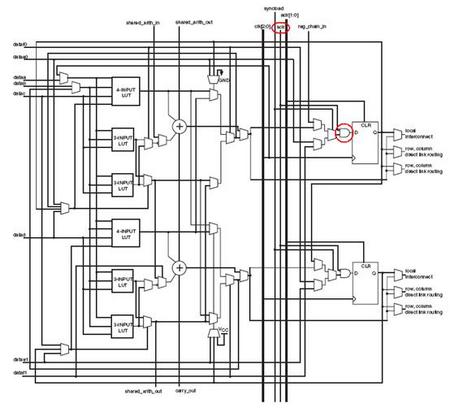

在Altera FPGA中,有两种方法可以将复位信号送达寄存器。一种是随数据门控输入,如图1所示,另一种是使用LAB宽控制信号,如synclr,如图2所示。

图1:使用组合逻辑的同步复位

图2:LAB-wide控制信号

我们看,第一种方法存在潜在的缺陷,即额外的门延时可能不得不被添加到逻辑电路当中,从而导致复位信号数据到达时间(Data Arrival Time)增加。在这种情况下,就可能会导致建立时间的slack为负。第二种方法依赖于LAB到寄存器的专用布线资源。尽管如此,还是比异步复位到同一个寄存器要慢。如图3所示,同步清零(synclr)到达寄存器的路径上经过了一个与门,而异步清零(aclr)到同一个寄存器的路径是直接到达的。此外从图3我们可以看到每个LAB的控制信号里边,只有一个同步清零(synclr),却有两个异步清零(aclr)。所以使用大量同步复位信号会导致fitter工具使用更多的LAB模块。然而,如果没有使用这些LAB范围内的同步清零信号,逻辑单元(LC)利用率可能会增加。这些都是在FPGA中采用同步复位时必须要做出的权衡。幸运的是,在Quartus II提供了一些控制措施来让用户在这两种方法选择采用哪种方法。这些控制可以是全局控制,也可以是只施加于给定的模块(entity)上,但是不能针对单个寄存器施加此控制。在AE中可以添加以下两类约束来进行此控制,分别是ALLOW_SYNCH_CLEAR_USAGE 和FORCE_SYNCH_CLEAR。第一个设置将允许综合器在需要的时候使用LAB范围同步清零信号,第二个设置,迫使工具总是使用它。无论哪种方式,同步复位将是比异步复位慢,在FPGA设计中不是最好的方式。

图3:ALM细节

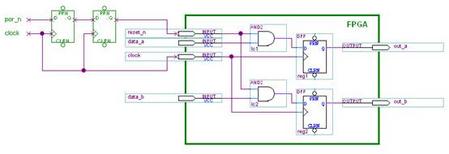

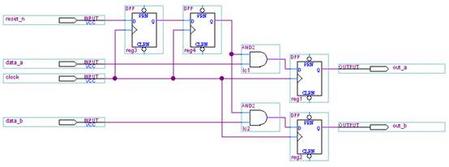

如果我要检视同步复位信号的时序,那么有两种同步复位信号需要考虑,即外部同步复位和内部同步复位信号。所谓外部同步复位信号是该同步复位同步于FPGA外部时钟域,只是这种同步复位在一般FPGA设计中是不常见的。图4显示了一个外部同步复位的例子。

图4:外部同步复位原理图

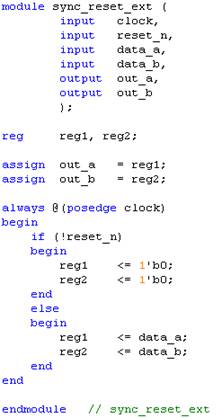

如图4所示,一个上电异步复位信号por_n在外部被系统时钟寄存两次后才输入到FPGA。而在FPGA内部,该复位信号和数据一同经过一个与门后作为一个寄存器的数据输入,产生一个同步复位。图5显示了一个图4所示原理图电路的Verilog代码,需要注意的是当使用同步复位时,复位信号不能放在进程的敏感列表中,否则就是异步复位了。

图5:外部同步复位Verilog代码

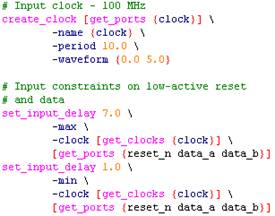

上述电路的时序约束如图6所示,由于外部复位信号是同步复位,所以只需要将reset_n约束为普通的输入信号,可以施加set_input_delay约束。

图6:SDC文件中约束外部同步复位信号

而大部分时候,输入到FPGA的复位信号是异步信号,在这种情况下,复位信号必须在内部先同步后再送达寄存器。如图7所示,现在同步寄存器位于FPGA内部。

图7:内部同步复位原理图

相应的,等效图7电路等效Verilog代码如图8所示。同样地,注意这里时钟沿还是唯一敏感列表。

图8:内部同步复位Verilog代码

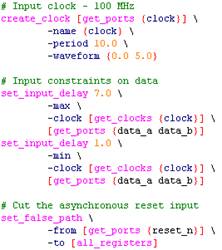

SDC文件里的约束和外部同步复位类似,只是现在复位输入信号不能被约束,因为它是一个异步输入信号,所以它应该被施加一个伪路径约束,如图9所示,这样就可以避免这样的路径被系统认为是未约束的路径。

图9:SDC文件中约束内部同步复位信号

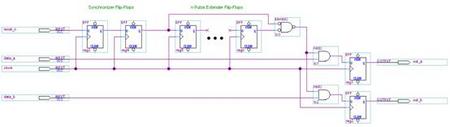

同步复位的另一个问题是图8中的同步寄存器的输入是异步信号,而常常有可能该异步信号的脉宽比较小(小于一个时钟周期)。一方面,这可以看作是一个缺点,因为异步信号同步的时候必须保证脉宽至少要一个时钟周期长,这样才能保证异步复位信号在第一个同步寄存器被捕获。另一方面,这又可以看作是一个优点,因为短脉宽增加了其抗噪声性能。这个异步输入上的一些虚假脉冲,如毛刺,很有有机会被第一个寄存器捕获,所以它们也就不会触发同步复位。在某些情况下,我们可能需要进一步增强抗干扰能力,可以让电路拒绝比如任何小于n个时钟周期的脉冲触发同步复位。这其实也非常有益于对异步输入的复位信号进行去抖动。为了做到这一点,应将电路作出以下修改,如图10所示。

图10:经过脉冲扩展的内部同步复位原理图

在许多设计中,可能不止一个时钟信号。在这些情况下,每一个时钟域都应该采用一个独立的复位同步电路。如果设计中使用了PLL,那么使用的时候有些地方需要格外注意。如果采用PLL的输出时钟来创建同步电路,那么这些时钟域将不会被复位,直到PLL锁定和PLL的输出时钟已经稳定。另外值得一提的是,如果PLL使用了复位信号,那么这个复位信号没有必要同步到PLL的输入时钟。一个异步复位即可用来复位PLL。同样,PLL使用复位,当PLL的输出时钟域都使用内部同步复位的时候,将进一步拖延这些时钟域同步复位置位。这个问题我们将在同步化的异步复位中再讨论,而且我们将看到这个问题被同步化的异步复位很好的解决。

/5

/5

用户438728 2014-3-28 23:59

coyoo 2013-6-18 17:16