在前面一篇博文里在介绍PET的FEE电路时我们见到过一个模拟ASIC芯片,如图1所示。这芯片对于我们来说就是一个黑匣子,但是经过笔者之前几篇文章的分析,我们似乎能够略微窥知了些内部乾坤,笔者打算试图画出其内部框图来。

图1:模拟ASIC芯片

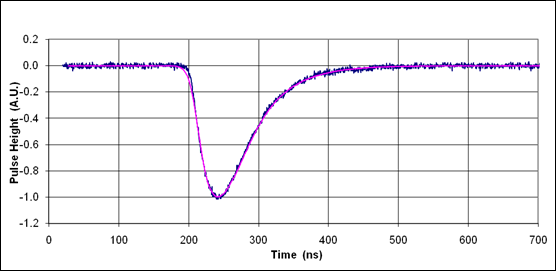

在剖析ASIC内部框图之前,我们有必要明确该ASIC芯片的输入和输出,输入是四个PMT信号,这四个信号属于负极性电压信号,如图2所示。

图2:典型PMT输出信号

这四个PMT信号进入ASIC之后,兵分两路,一路进入CFD功能模块,这里不过多介绍,可以参考前面博文,所以CFD功能模块这里我也只是使用CFD模块大框图标识。第二路是这四个信号要分别进行整形处理,第一步是要将这四个信号翻转为正极性信号;第二步是因为PMT的输出一般幅度不大,所以一般都需要进行放大处理;第三步是进行滤波等整形处理;第四步是分别产生X、Y和Energy输出。

以上描述了ASIC的输入到内部各个功能模块,这里需要解释一下ASIC的输出,即X、Y和Energy。一般根据PET原理,X和Y是四个PMT信号中两个能量之和,而Energy就是四个PMT的信号的能量之和。这里所说的“能量”是指PMT信号的积分而来,所以ASIC中上述第四步产生输出的功能模块里包含有积分模块。

由此,我们可以大致勾勒出该模拟ASIC的内部框图,如图3所示:

注:图3中,第一列放大器属于VGA放大处理,用于放大PMT信号;最后一列放大器实现了加法器功能。

/5

/5

文章评论(0条评论)

登录后参与讨论