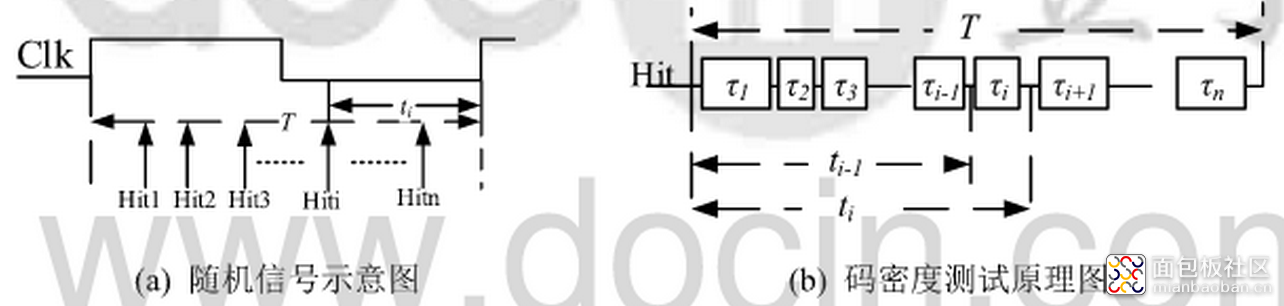

图1:随机信号码密度测试原理图

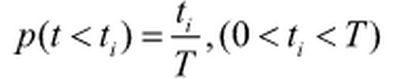

延时链中输入大量的随机跳变脉冲,对随机脉冲的上升沿进行采样,采用得到的数据即为码密度数据。由于跳变脉冲Hit信号是随机信号,则Hit信号落在参考时钟周期内(0,T)任何一个相位点的概率相同,即任何一次Hit信号与参考时钟上升沿的间隔时间t也是完全随机的,其中t的范围为(0,T)。

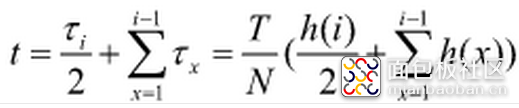

随机时间间隔t

(1)

(1)

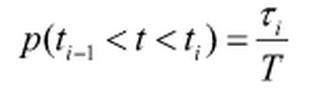

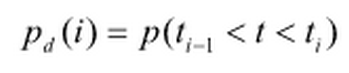

如图1(b)所示,当随机时间间隔t的范围为(ti-1,ti)时,说明随机信号Hit落在延迟链中第i个抽头处,其概率为:

(2)

(2)

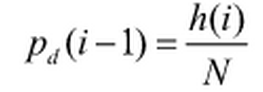

假设在N次测试过程中,Hit信号停在第i个抽头的次数为h(i),其发生概率为:

(3)

(3)

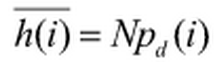

当测试次数N无限大时,则有:

(4)

(4)

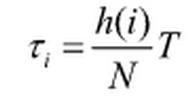

根据公式(3)和公式(4),则可以求得第i个抽头延时时间为:

(5)

(5)

根据公式(5)可以依次求出每个延迟单元的延迟时间,进而可以求出i个延迟的累计延时为:

(6)

(6)

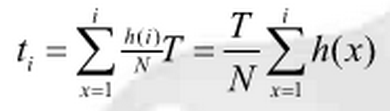

但是时间间隔t是落在第i个抽头内部,所以无论TDC的测量值取ti还是ti-1,都会产生较大的测量误差。假设取测量值δ,则ti-1<δ

(7)

(7)

当δ=(ti+ti-1)/2 时,标准方差达到最小值(ti+ti-1)²/12,所以应取测量值为:

(8)

(8)

即把测量值校准到延迟单元的中间位置。

公式(8)所确定的测量值需要足够多的测试样本数N才能保证其精确度,但是在实际测试中,测试样本数N不可能无限大,所以,在有限个N次测试中,Hit信号停留在第i抽头的次数h(i)是服从二项分布。其平均值为:

(9)

(9)

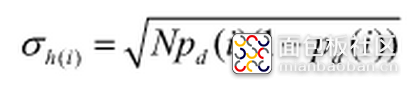

标准差为:

(10)

(10)

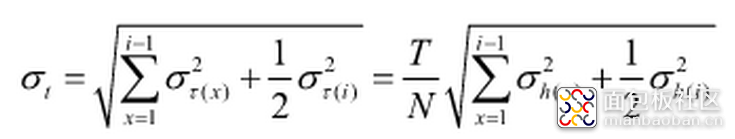

由于所有的样本都是随机的,由公式(5)和公式(8)得:

(11)

(11)

假设在一个参考时钟周期T内内插了K个延迟单元,理论情况下这K个延迟单元的延迟时间相等,则有:

(12)

(12)

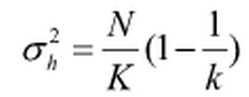

从公式(11)可知,当i=K时,σt达到最大值为:

(13)

(13)

如果标准误差σtmax要小于10ps,系统参考时钟周期T为5ns,则由公式(13)可得:N要大于250000。

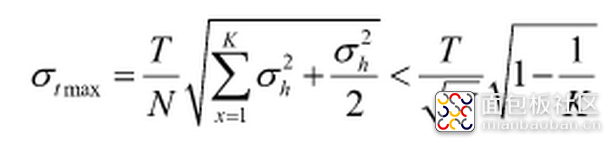

通过以上分析,设计一个如图2所示的校准电路。校准电路模块主要由随机信号产生电路、随机信号保持电路以及校准查表存储电路组成。随机信号产生电路是利用环形振荡器产生随机校准信号;校准查找表存储电路是对TDC校准结果建立累加查找表。

图2:校准电路基本结构

随机信号产生电路

码密度测试需要对大量的随机信号进行量化统计,为了保证延迟链中不对同一个位置进行重复采样,必须使得校准信号与参考时钟无整数倍关系。在数字电路中,通常由奇数个反相器级联构成的环形振荡器来产生随机信号。

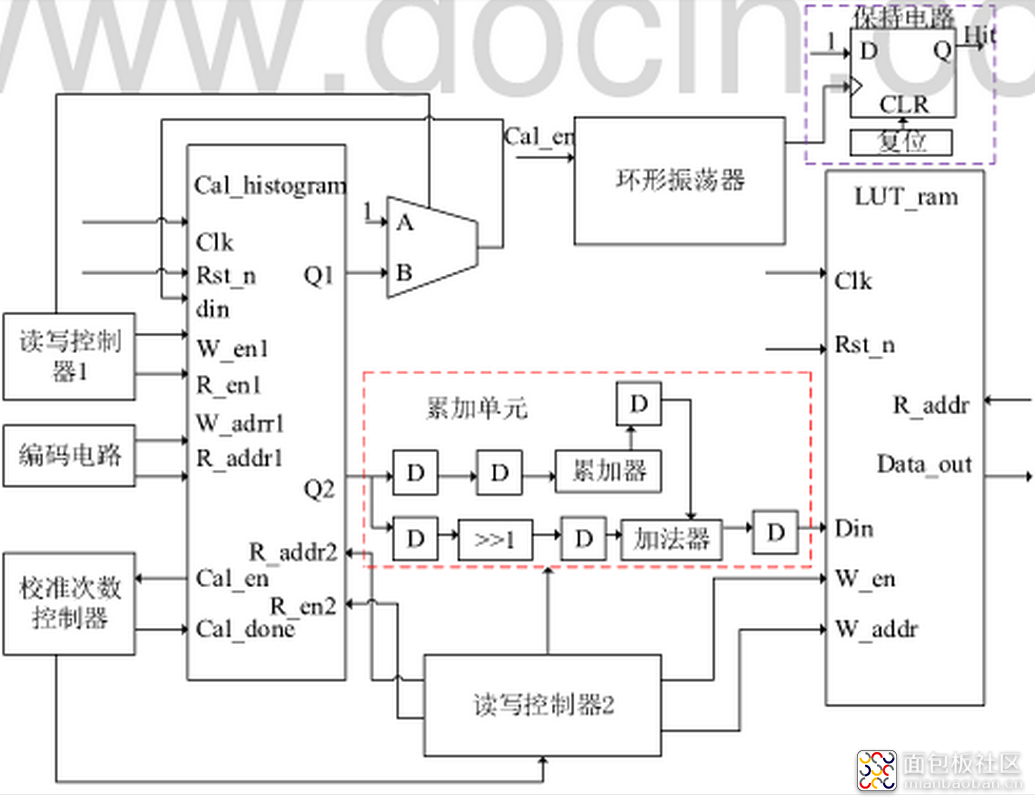

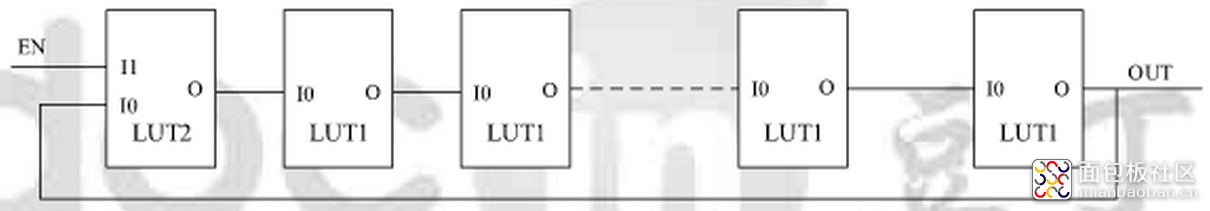

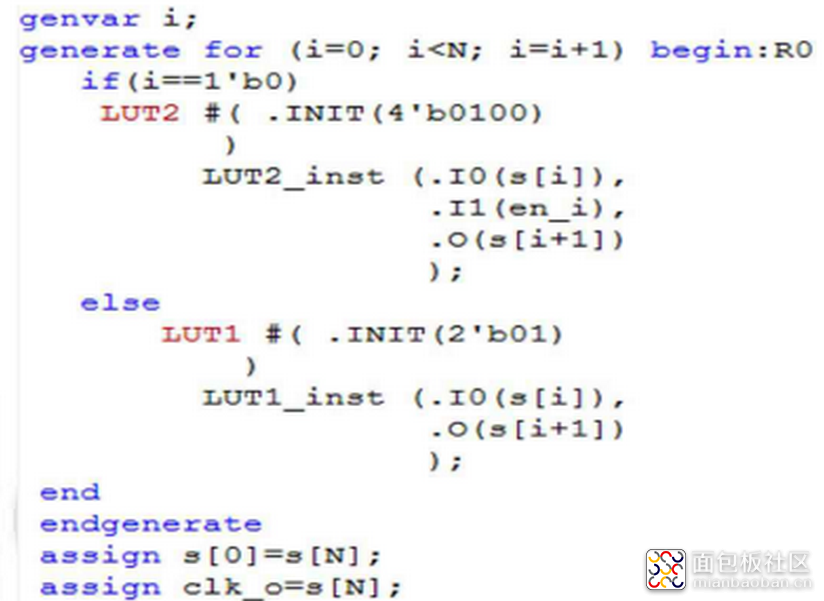

FPGA采用的是基于SRAM工艺的查找表结构,没有专门的反相器,都是利用LUT来实现所谓的反相器。图3是基于LUT的环形振荡器结构图,包括偶数个LUT1和一个LUT2。在TDC测量中,只有在校准模式下TDC才会需要环形振荡器产生随机信号对延迟链进行实时地校准,因此对环形振荡器加入了使能控制信号,使得环形振荡器只在校准模式下工作,从而降低电路功率的消耗。查找表LUT1和LUT2配置分别如表1和表2所示。

图3:查找表构成环形振荡器结构图

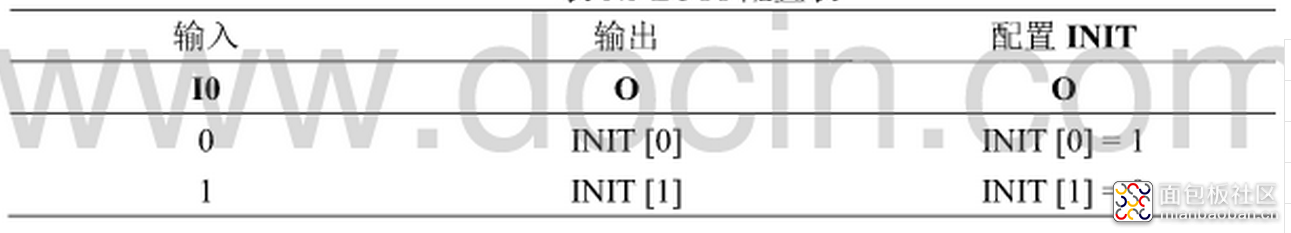

表1:LUT1配置表

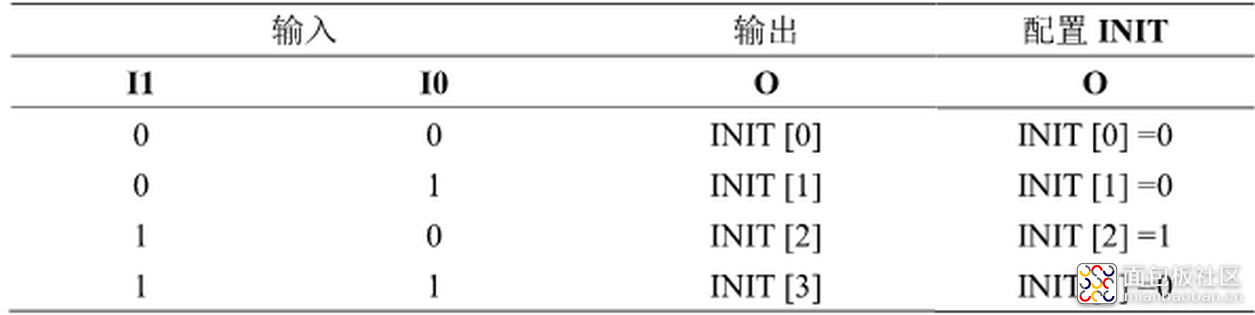

表2:LUT2配置表

从表1和表2可以看出,通过把LUT1的内部初始值INIT0-INIT1设置为“10”,便可使LUT1实现反相的功能;LUT2内部初始值INIT0-INIT3设置为“0010”,当I1输入值EN为“0”时,不管I0的输入是“1”还是“0”,LUT2的输出均为0,不会实现反相的功能,即环形振荡器不会起振;当I1输入值EN为“1”时,LUT2对输入信号I0进行反相。所以由偶数个LUT1和一个LUT2级联可以构成环形振荡器,并且通过使能控制信号可以控制环形振荡器的工作状态。环形振荡器核心代码如图4所示:

图4:环形振荡器核心Verilog代码

由于TDC完成一次校准需要时间,为了使得TDC在未完成本次校准前,不对接下来的随机信号上升沿进行采样,所以每次校准前需要对随机信号进行保持处理,该部分电路结构如图2中紫色线框所示。环形振荡器输出接到D触发器的时钟端,输入端设置为高电平“1”,当随机信号到来时,该触发器就输出一个高电平信号,校准完成后再利用复位端对其清零,然后等待下一个随机信号到了继续进行保持处理,以此类推,直到全部的校准信号完成。

校准查找表存储电路

校准查找表电路主要由图2中Cal_histogram、累加单元、LUT_ram以及一些读写控制逻辑组成。Cal_histogram电路是对TDC中各个抽头的随机跳变次数进行统计存储;累加单元是根据公式(8)把测量值校准到延迟单元的中间位置。LUT_ram是对累加单元处理后的数据建立查找表。在TDC校准模式时,TDC需要根据Cal_histogram中存储值实时地更新查找表LUT_ram;测量模式时,根据编码电路结果读取查找表LUT_ram中对应地址的校准数据。

TDC整个校准操作流程如下:

1. 复位清零。读写控制器1和读写控制器2分别依次生成0-255位作为Cal_histogram和LUT_ram的写地址,将数据0依次写入Cal_histogram和LUT_ram的各个存储单元。

2. 启动码密度测试。每进行一次校准,随机信号会在延迟链被捕获一次,该被捕获的信号通过编码电路得到其在延迟链的位置(地址),在Cal_histogram中该地址中对应的值加1,如此循环直到所有的校准次数完成,其中,校准次数控制器来控制校准次数;读写控制器1控制Cal_histogram中的读写。

3. 建立查找表。全部的校准次数完成后,校准次数控制器启动读写控制2,读写控制器2依次生成0-255位Cal_histogram的读地址,然后经过累加单元依次把数据累加到每一位的中间位置并存入相应地址的LUT_ram中,查找表建立完成后,TDC由校准模式转换到测量模式,并根据编码结果读取LUT_ram相应地址位存储的数据,即可得到校准后的“细”测量结果。每测量完一次,校准电路都会被复位并重新建立查找表。

框图

coyoo 2025-2-19 09:41

Pie 2024-12-9 20:58

coyoo 2024-3-18 11:06

从头越x 2024-3-16 16:47

coyoo 2024-3-13 16:05

从头越x 2024-3-12 21:45

islcbyzzz 2024-2-20 15:39

coyoo 2024-2-20 15:28

coyoo 2024-2-4 08:57

islcbyzzz 2024-2-2 11:35