编码方法:

- 顺序查找:利用for循环,从tc的第0位依次遍历到第一个0-1(或1-0)跳变的位置,输出跳变处的位置序号,完成编码。顺序查找法比较直观,无需任何外加电路就可以抑制bubble现象,缺点是最大循环次数为n次。

- 折半查找:根据tc的特征,可以使用折半查找法查找0-1(或1-0)跳变的位置。折半查找法的循环次数最大为m(2的m次方=n),但是bubble现象会导致错误的输出,故需要外加电路来消除bubble现象。

- 累加法:通过累加tc中1的个数来判断0-1(或1-0)跳变的位置。累加法需要循环累加n次,bubble现象引起的误差在编码上体现为几个LSB的误差。

编码电路设计:

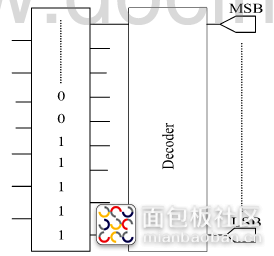

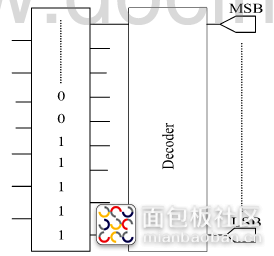

延迟链中触发器阵列锁存的数据以温度计码形式输出,如图1所示。

图1:温度计码示意图

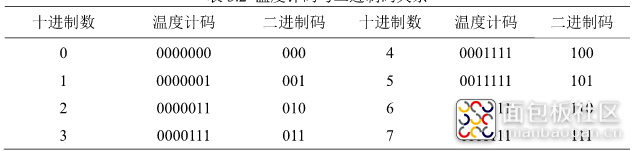

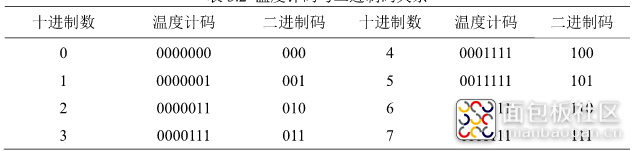

当没有输入信号的时候,延迟链中所有的输出均为0,当有待测信号进入延迟链时,延迟链输出信号将从低级开始一级级发生0-1跳变,待测信号经过延迟单元输出1,而待测信号没有经过的延迟单元将输出0,从而可以根据延迟链所有1的个数来判断待测信号在延迟链传播延时。以7位温度计码为例,温度计码与二进制码对应关系如表1所示。

表1:温度计码与二进制码关系

如果延迟链中总共引出了255个抽头,即255个延迟单元,如果按照温度计码形式输出就需要输出255位温度计码,这样不但浪费了大量的存储资源,而且造成下一级的逻辑运算变得更加复杂,故需要将温度计码转换为二进制码。

而实际延迟链输出经过寄存器锁存后,各抽头的数据数据可能不是严格的递进关系(根据不同工艺的FPGA逻辑结构会有不同,在Altera的65nm工艺之前的器件基本不会重新bubble问题,但是采用新工艺后的fpga,虽然延迟单元的延迟时间缩小,带来的问题是更容易出现bubble),触发器阵列中锁存的数据也不是标准的温度计码,而是带有“冒泡”(Bubble Error)的温度计码如(000...01011111)形式,而且“冒泡”出现的位置也包含着延迟信息,如果忽略不计,将会造成较大的测量误差。所以编码电路要能够识别“冒泡”的位置。

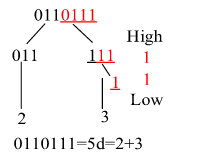

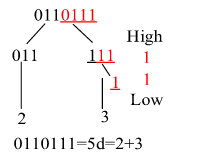

冒泡的位置一般发生在待测信号被锁存时位于延迟链中的位置,而对应Xilinx的器件来说就是最后捕获待测信号的carry4之中。这里以7位带有“冒泡”温度计码(0110111)转换为3位二进制码(101)为例来阐述其基本原理。具体步骤如下:

- 首先对7位“冒泡”温度计中的第1-4位进行判断,如果四位的值全部为1,则代表温度计码中的0-4位数都为1,相应地把二进制码中最高位置1,表示为3'b1xx;如果四位不全为1,则代表温度计码为1的值肯定小于4位,相应地把二进制码中最高位置0,表示为3'b0xx。本例中四位的值不全为1,所以对应的二进制码的最高位置为0.

- 根据7位“冒泡”温度计码中的第1-4位来对温度计码,进行折半,如果四位全部为1,则选择高三位数值(011)进行下一次查找,如果四位的值不全为1,则选择低三位数值(111)进行下一次查找并且把高三位的数值(011)进行累加。本例中四位的值不全为1,所以选择低三位的数值(111)进行下一次查找并把高三位的数值(011)进行了累加。

- 最后把低三位查找的值与高三位累加的值进行加法运算得到最后的查找值。至此就把“冒泡”温度计码(0110111)转换为了二进制码(101)。

上述步骤体现的编码电路原理示意图如图2所示:

图2:编码电路原理示意图

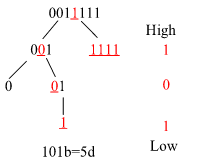

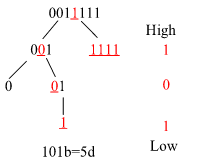

如果延迟链经过优化可以使得各个抽头的数据按照严格的递进关系输出,从而触发器阵列中锁存的数据为标准的温度计码,其编码电路原理如图3所示,同样的,以7位温度计码(0011111)转换为3位二进制码(101)为例来阐述其基本原理。具体步骤如下:

- 首先对7位温度计码中的第四位进行判断,如果第四位的值为1,则代表温度计码中的0-4位数都为1,相应地把二进制码最高位置1,表示为3b1xx;如果第四位的值为0,则代表温度计码中为1的值肯定小于4位,相应地把二进制码中最高位置0,表示为3'b0xx。本例中第四位的值为1,所以对应的二进制码的最高位置为1.

- 根据第四位的值来对温度计码进行折半,如果第四位的值为1,则选择高3位数值(001)进行下一次查找,如果第四位的值为0,则选择第三位数值(111)进行下一次查找。本例中第四位的值为1,所以选择高三位的值(001)进行下一次查找。

- 根据第二步选择的三位数值,对其中间位进行判断,如果中间位的值为1,则代表选择的3位温度计码中低2位的值都为1,相应地把二进制码中次高位置1,表示为3'bx1x;如果中间为的值为0,则代表选择的三位温度计码中为1的值肯定小于2位,相应地把二级制码中次高位置0,表示为3'x0x。本例中选择的3位温度计码的中间位置的值为0,所以对应的二进制码的次高位置为0.

- 以此类推,继续对剩余部分进行折半查找,图3中剩余数据为1,因此二进制码表示为101,至此已经把温度计(0011111)转换为了二进制(101)。

图3:标准温度计码编码原理示意图

图3所示的编码电路在Xilinx的Vertex-5实现的Verilog代码以及电路结构分别如图4和图5所示,其中红框内的触发器为保持寄存器,从启动编码电路开始,等待两个参考时钟后对编码电路采样,然后保持不变,直到下一次编码电路的启动。

图4:编码电路Verilog代码

图5:编码电路结构框图

作者: coyoo, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-1010859.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

Liufd@2916 2023-12-4 20:05

curton 2019-11-1 21:04