DDS做过一次,不过使用XILINX系列的芯片,那时候FPGA的RAM容量并不太大,所以就值存储了1/4的波形数据,然后通过正弦的对称性来实现整个信号的产生,中间也没遇到什么问题,产生的波形还是可以的,今天我重新做DDS,只不过FPGA换成altera的芯片,如果对波形进行完整的存储,没有什么问题的,只不过在6M正弦的时候波形就不太好看了,我还想通过存储1/4 的波形来宽展容量,但是看到的波形在中间过渡的地方总是像滤波器那样,显示突出再回来,在频率高的时候,本来点就少,那个位置就很突出,。。。。。挺烦人的!中午到现在一直在找原因,波形沿Y轴翻转没有问题,就是在沿X轴翻转的时候出现这个问题

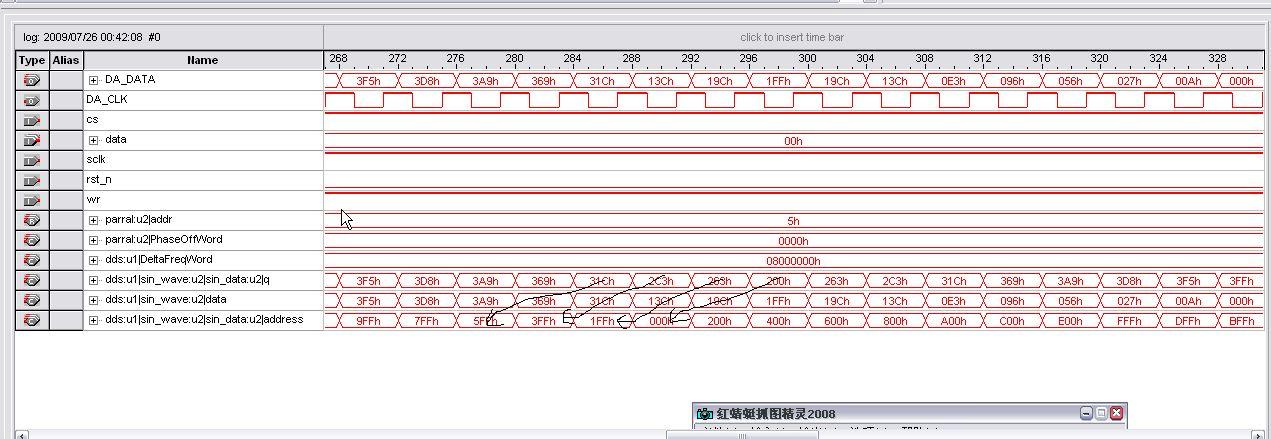

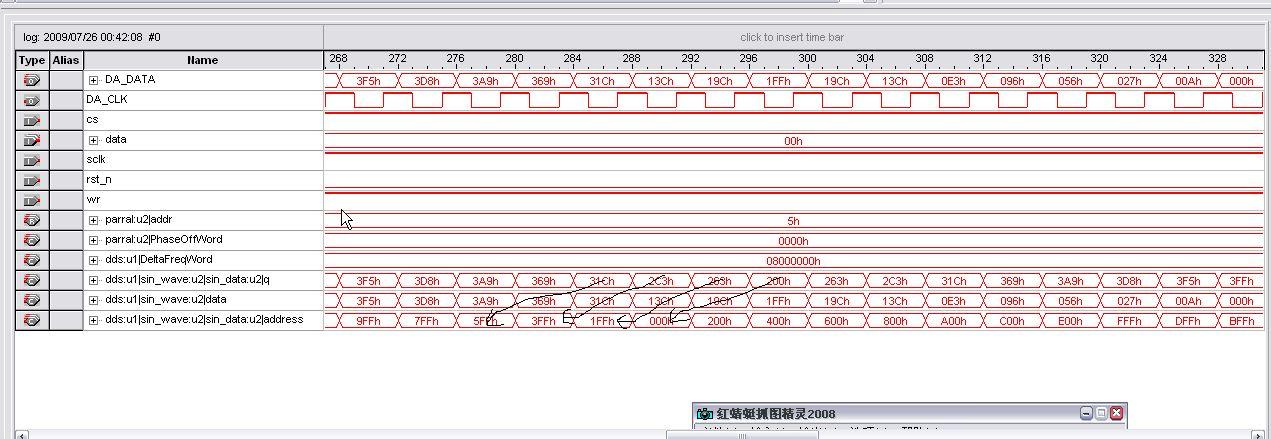

刚才在使用SIGNALTAP调试的时候总与看到问题的所在。

DDS输出频谱杂散的抑制.pdf

这个里面提到一些ROM存储扩展到方法,里面说“

由于正弦信号的波形具有四分之一对称性,ROM表中只需存储[ 0 ,π/ 2 ]的波形 ,在电路中利用相位的最高位控制输出波形的符号 ,次高位控制 ROM表的寻址 ,对相位和幅度进行适当的翻转便可得到整周期波形 ,硬件电路中易于实现ROM表压缩比4 :1”。所以在编写代码的时候;假如说是12为的地址线,10位的数据,那么通过使用累加器输出的高14位中的低12位和地13位异或的结果作为ROM的地址,这样就可以把波形沿y轴翻转,把第14位和输出的数据异或得到输出的数据,可以实现波形的沿X轴翻转,但是波形出现了问题,问题就在于altera内部实现ROM的结构和XILINX不一样,它不能够立刻将输入地址对用的数据输出,而是要等2个时钟才会输出

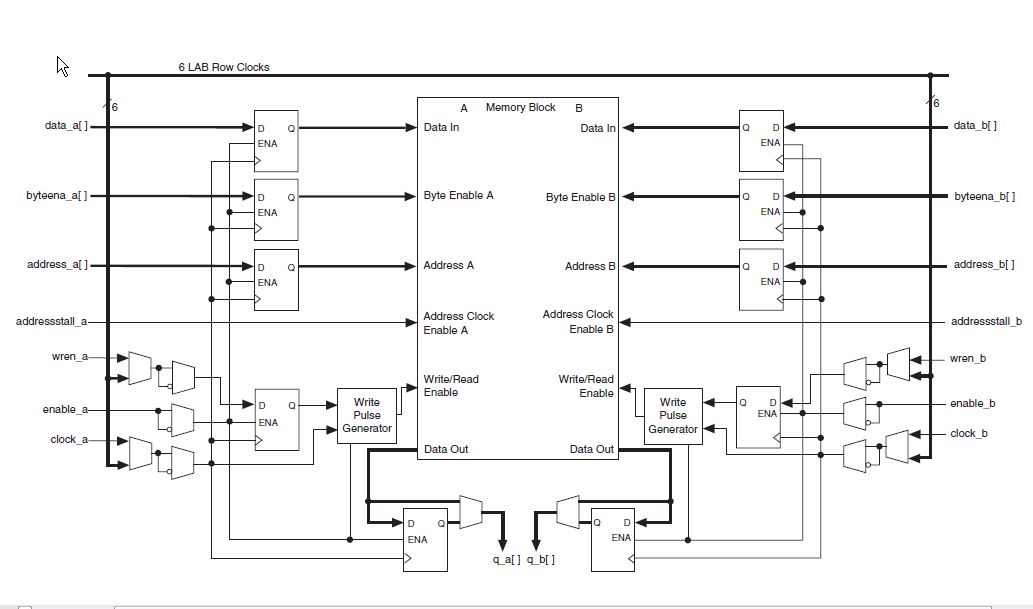

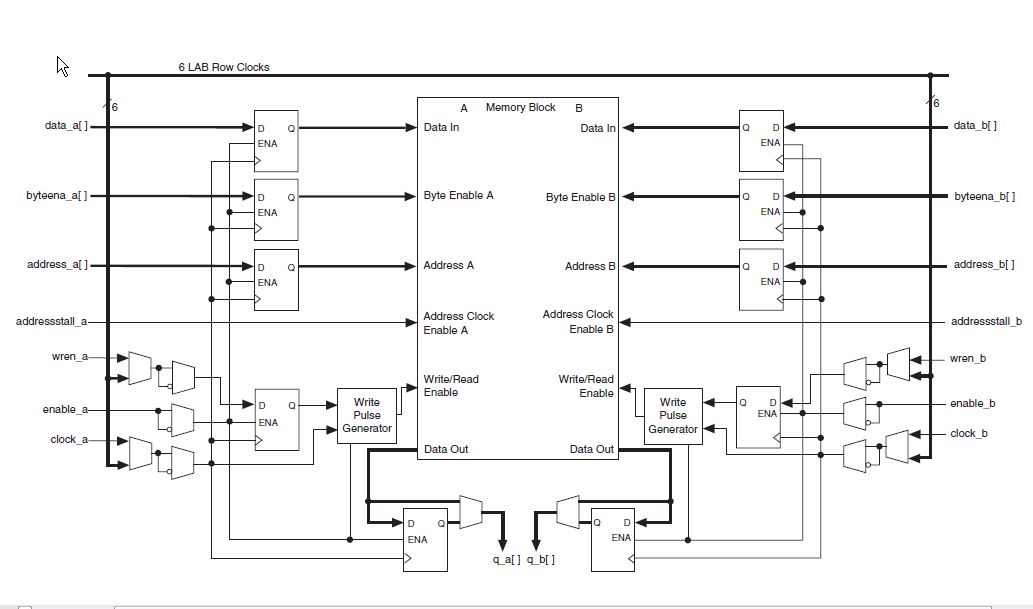

看过ROM内部的结果的话就不会奇怪了:

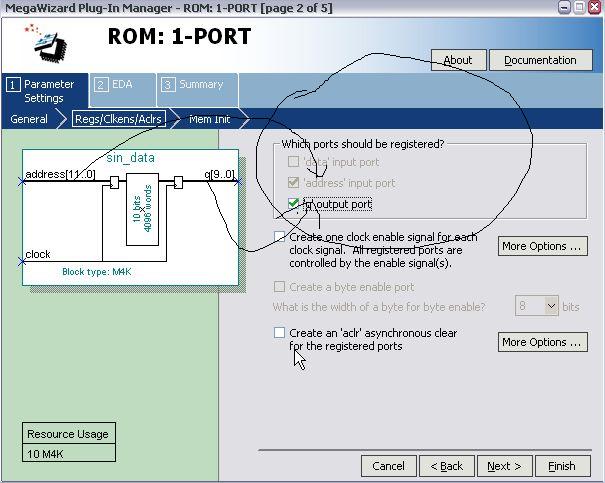

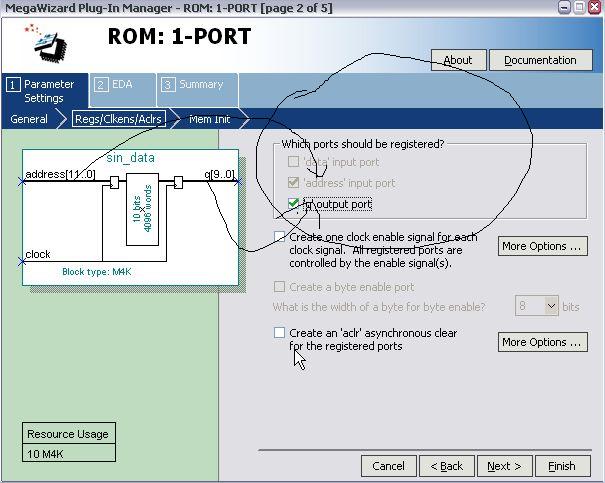

这个是双口ROM的结构 。不过已经可以说明问题了,这个IP核内部对输入数据和输出数据都做了锁存,这个锁存的选项在初始化IP的时候是可以选择的

里面可以看的很清楚,只能够对输出数据是否锁存进行选择,但是对输入是不让选择的的;

当我把里面的锁存取消后,波形的效果就会好很多,不过还是不行的。。。

可能自己的做法不对吧,对波形的翻转不该这样做。。。我把代码放上来,希望有大虾指导

https://static.assets-stash.eet-china.com/album/old-resources/2009/7/26/ed0cd0f9-2021-4b6a-afa6-a72846d2534c.rar

/4

/4

用户377235 2013-3-13 21:37

zhangshaobing517_935512703 2009-7-28 16:27

用户124183 2009-7-28 15:46