原创

BCD与二进制相互转换(含Verilog代码)(一)

BCD码转二进制:

所谓BCD码,就是用四位的二进制表示十进制,什么意思呢,举例说明。

1:0001

2:0010

3:0011

4:0100

5:0101

6:0110

7:0111

8:1000

9:1001

123:0001 0010 0011(BCD码)

123:0000 0111 1011(二进制码)

一。为什么要转换进制?

我们可以用BCD码来表示十进制,比如157,123,用BCD码来表示分别是(0001 0101 0111)(0001 0010 0011),可是BCD码不能够直接进行运算,157+123=280,而括号里面的两个BCD码相加之和显然不是280的二进制。所以就需要先将BCD码转换成二进制,经过换算之后再转换成BCD码。(有些人会问,为什么要转来转去呢,因为计算机只识别二进制,而有时我们需要输出BCD码)

二。转换原理

首先我们看二进制与十进制的转换,例1001(二进制),转换成十进制是

1*2^3+0*2^2+0*2^1+1*2^0=9(十进制)。

n位的二进制转换过程为

a(n-1)*2^(n-1)+a(n-2)*2^(n-2)+........+a(0)*2^0

转换一下形式。

(((a(n-1)*2+a(n-2))*2+a(n-3))*2........+a(0)

通过上面的形式发现,我们可以通过×2+b的方式来实现转换。而×2在可以通过左移一位来实现,下面来谈谈这个b

如上所述,BCD码用四位二进制表示0-9,而四位二进制可以表示数的范围为0-15,每进一位就会丢掉6,那么就要加上6/2=3(左移一位),那么在什么条件下左移呢?那就要看在什么情况下会进制,BCD码是二进制编码的十进制,那么就是逢十进一,10/2=5.因此得到条件,即判断每四位是否大于4,因为5-9进一位溢出。

我们来整理一下,二进制转BCD的方法是通过左移,然后每四位判断是否大于4,满足则加3.

利用组合逻辑实现的代码如下:

更新一个8bit代码2022/7/12

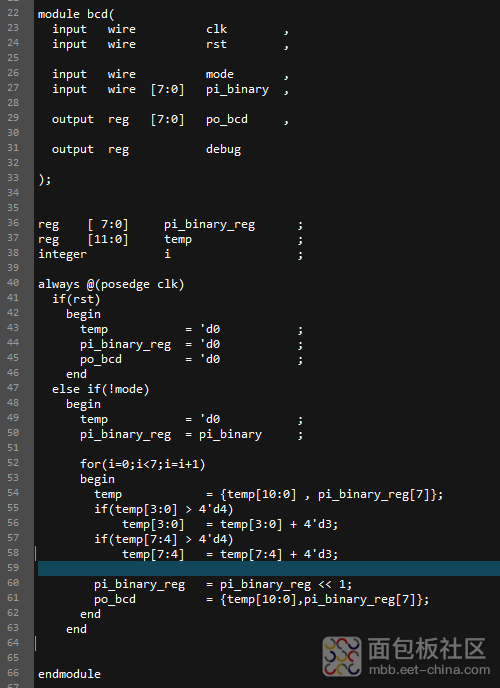

利用时序逻辑实现的代码如下:

我们可以根据不同的情况选择不同的实现方式。时序逻辑还可以使用二段式的状态机来写,笔者认为,该模块较小,这种方式便于理解。实现方法因人而异。

作者: 洋仔, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-1854387.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

用户377235 2016-3-31 17:49

83642879_827020636 2015-10-13 14:05

用户432850 2015-10-12 21:23

83642879_827020636 2015-9-18 10:52

用户1825345 2015-9-16 23:15

83642879_827020636 2015-9-16 22:44

用户1696769 2015-9-16 16:45