系 统:ubuntu 18.04

仿真平台:vcs_2018.09-SP2

开发平台:vivado 2019.2

本文的主要目的是自动化搭建基于vcs+uvm+xilinx ip的仿真平台,节省平台搭建的时间与精力。

1.2 概述拿到一个项目,一般的平台搭建的步骤:去网上找一个makefile脚本(或者使用原项目脚本),修改相应的软件路径,添加rtl与tb顶层,如果工程中包含xilinx ip核就比较麻烦,需要添加相应的库文件,这里面最麻烦的就是对xilinx ip核的独立编译。有经验的工程师很快可以搞定,对于小白来说就要花一些时间。

vivado关联vcs仿真可以导出shell脚本,天然支持xilinx ip核,解决了上述的麻烦。将生成的脚本转换成makefile脚本,添加uvm编译仿真配置以及uvm开发代码,支持vcs+uvm+xilinx ip核的平台就搭建好了。

除了自动化的部分以外,我们需要准备的东西包括

1. xilinx的工程(项目工程)

2. makefile脚本(后面会给出模板,替换相应的位置即可)

3. uvm代码(如果不需要uvm,用sv即可)

2. vivado关联vcs仿真

这一步骤需要安装好vcs,能够正常启动,然后在vivado 2019.2中做如下配置:

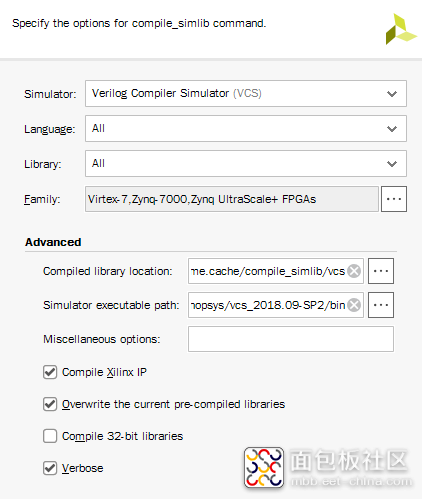

2.1编译仿真库点击Tools->Compile Simulation Libraries

Compiled library location会默认选择 *.cache下

在Simulator executable path中添加vcs 仿真器可执行文件的位置,点击compile等待仿真库编译完成。

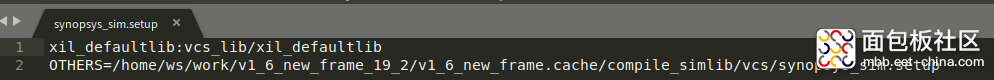

编译完仿真库,打开仿真库所在文件夹,找到synopsys_sim.setup,先记住它,后面会用到。

2.2修改仿真配置

点击打开Settings->Simulation->

1.修改Target simulator为Veriolog Compiler Simulator(VCS)

2.在以下位置添加配置

Elaboration->vcs.elaborate.vcs.more_options中添加以下配置

-cpp g++-4.8 -cc gcc-4.8 -LDFLAGS -Wl,--no-as-needed

保证系统当前使用的gcc g++版本是4.8

2.3启动仿真

3. 导出仿真脚本3.1导出仿真脚本

打开File->Export->Export Simulation,如下图Exoprt directoty路径

选择好以后,点击OK会生成相应的仿真脚本

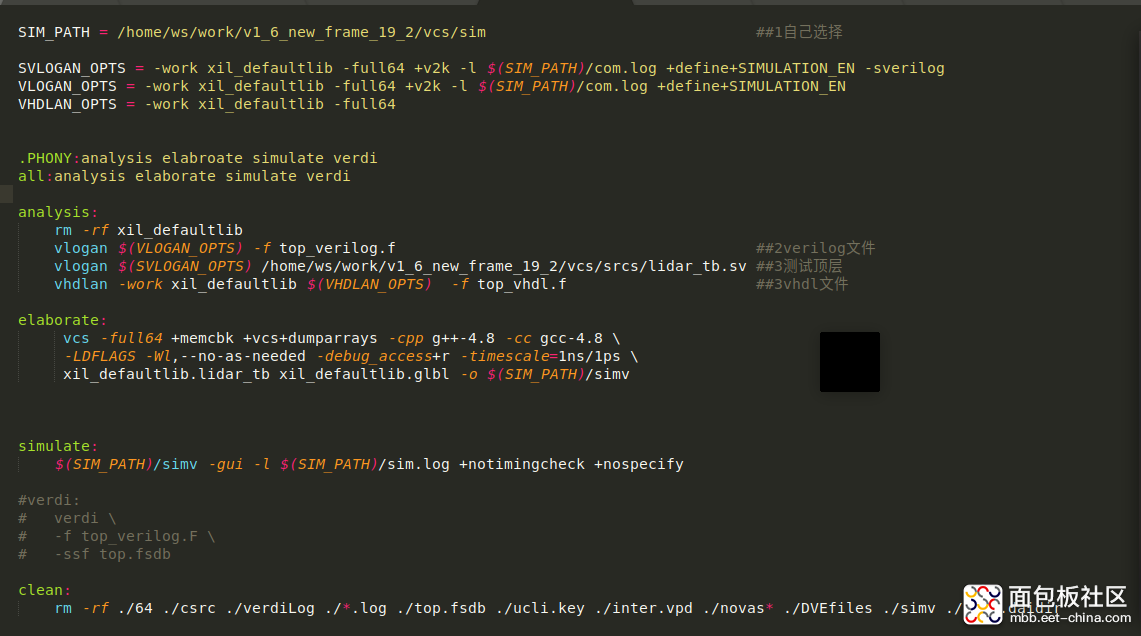

3.2 将shell改写为makefile

在导出路径下面会生成一个顶层命名的shell,将其改写成Makefile,这里已经将Makefile准备好模板,完成“填空”后直接添加即可。如下图,修改以下”##”标示的4处即可。

3.3 关联xilinx ip库

创建synopsys_sim.setup文件,将路径指向2.1小节中的synopsys_sim.setup位置,内容如下:

添加文件夹uvm与uvm-1.2,其中uvm文件夹内是uvm开发代码,uvm-1.2是uvm库文件,将目录放到与vcs(导出仿真脚本路径)同级路径下,这样修改工程后再次导出的时候文件夹就不会被覆盖。uvm相关的配置已添加在Makefile脚本中,不需要再添加。

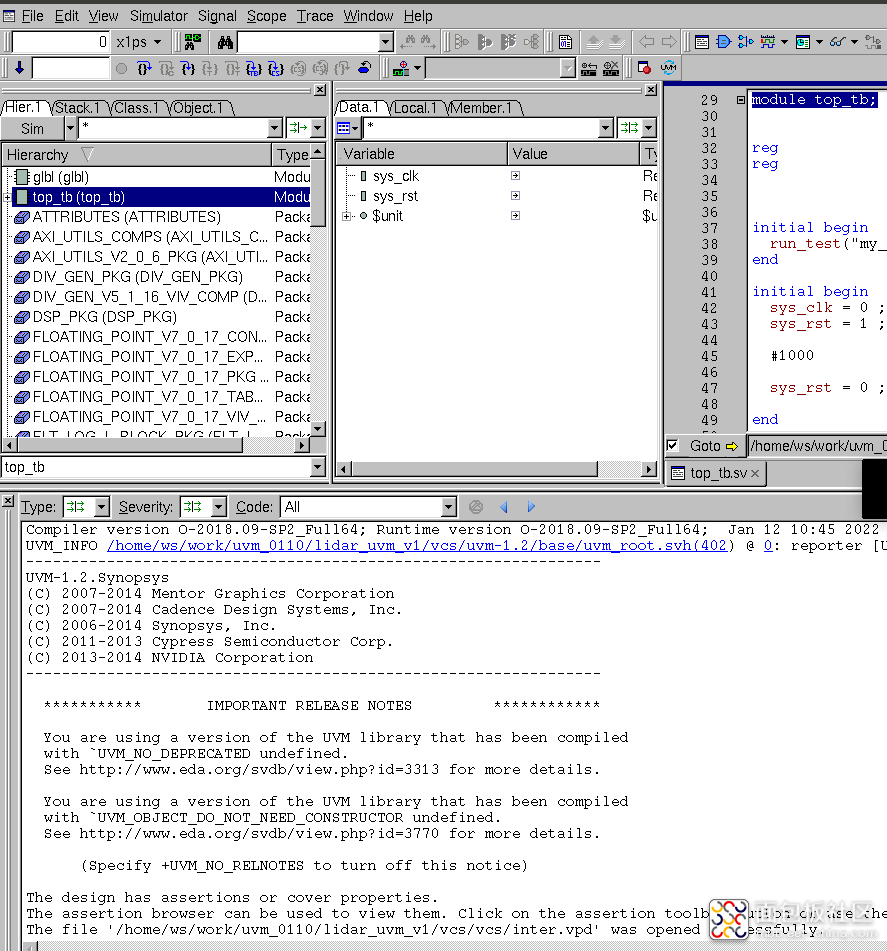

5. 启动仿真

打开终端,输入make,启动仿真。

作者: 洋仔, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-1854387.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/4

/4

文章评论(0条评论)

登录后参与讨论