新建一个zynq_2的文件夹,将上个实验的工程的文件全部拷贝到这个文件夹。

打开这个工程

(一) 添加两个GPIO实例

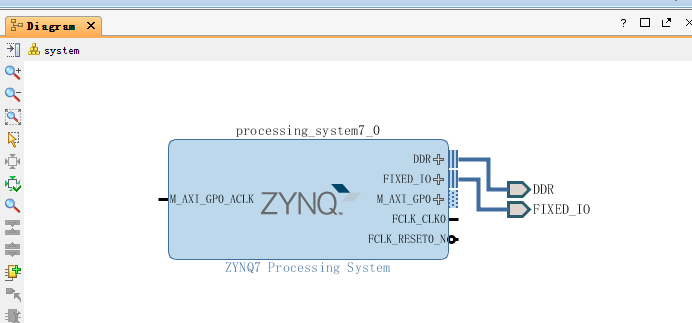

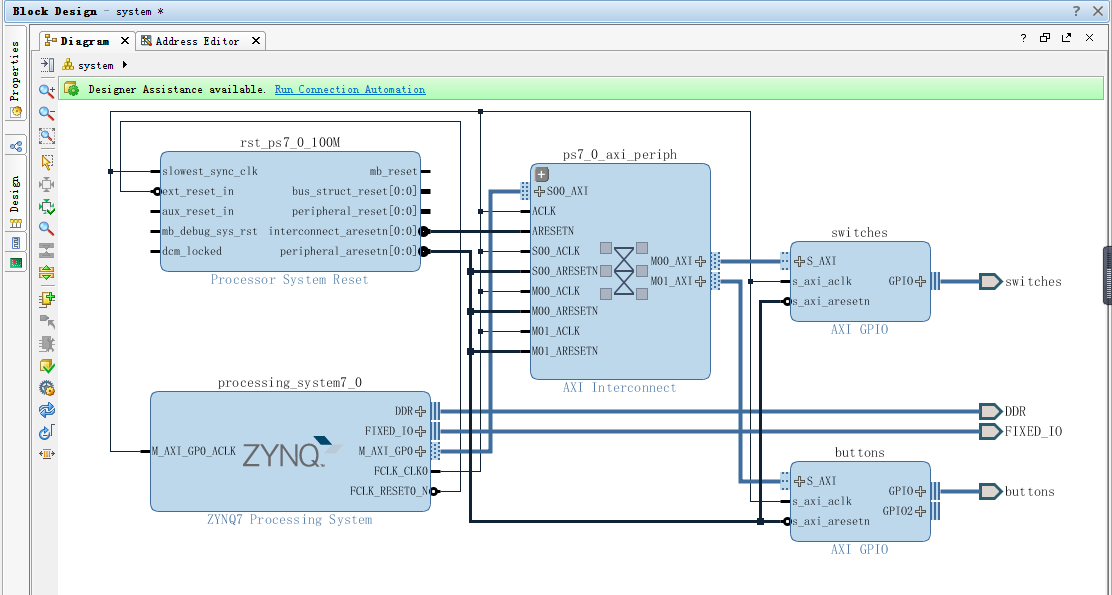

下面将使能 AXI_M_GP0 接口、FCLK_RESET0_N,FCLK_CLK0端口,从IP Catalog 中选择并添加2个GPIO例化到PS中。在 Source 标签下,展开system_wrapper,在展开项中,选择并双击system.bd文件,调用IP集成器。(也可以在Flow Navigator 窗口下,在IP Integrator 下,单击 Open Block Design)。

在Diagram窗口下,双击ZYNQ块符号,打开ZYNQ配置。单击32b GP AXI Master Ports。

在Diagram窗口下,双击ZYNQ块符号,打开ZYNQ配置。单击32b GP AXI Master Ports。弹出PS-PL Configuration界面。在该界面中,选中AXI GP0 interface后的复选框。

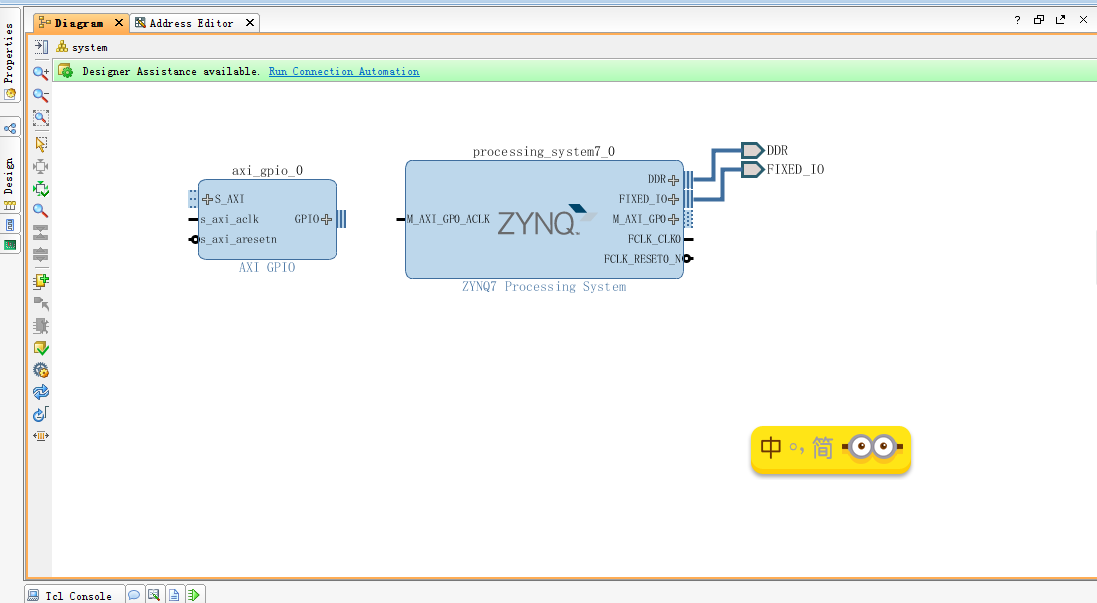

单击Diagram左侧一列工具栏内添加IP按钮,在搜索框输入g,找到AXI GPIO IP核。双击添加到设计中。

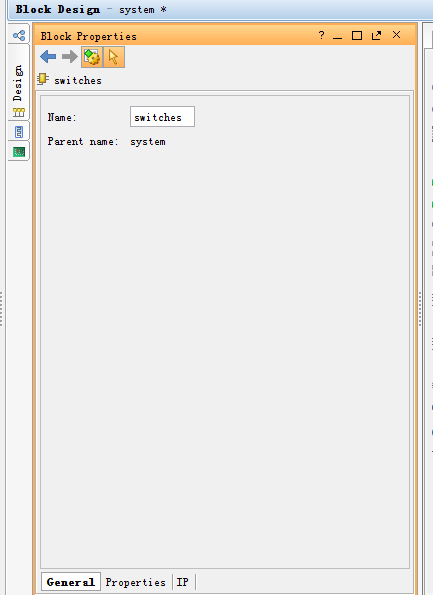

点击 axi_gpio_0块图标。在Block Properties 窗口内,将Name后面的名字改为 switches

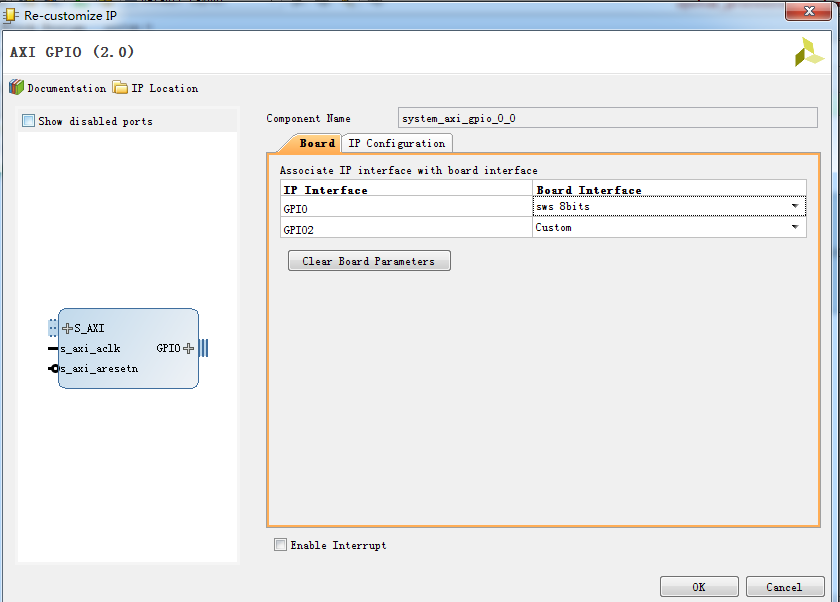

双击axi_gpio_0块图标,打开配置对话框。(由于在建立工程时已经选择了Zedboard,提供了用于zedboard的板级支持包,所以vivado知道板子可以利用的资源)。

按照如下参数配置。

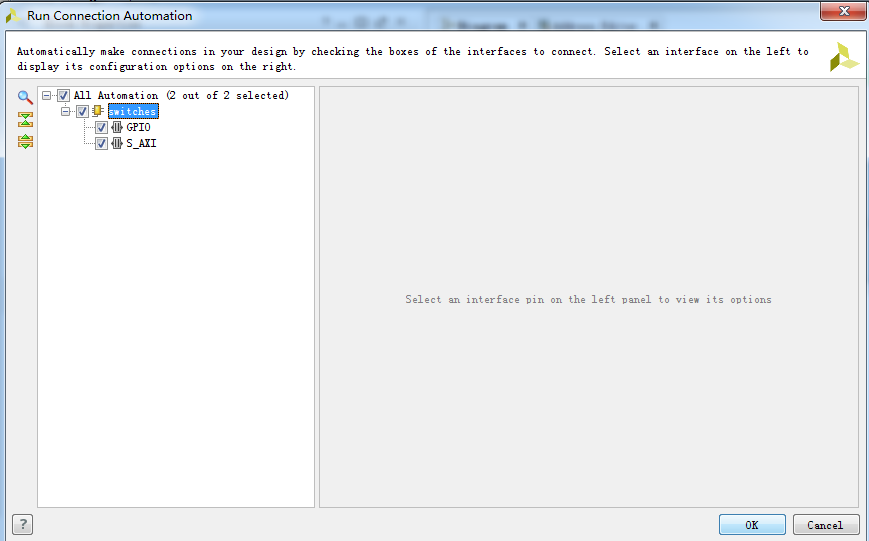

单击OK按钮。在Diagram窗口的最上面出现Designer Assistance is available 。单击右侧的 Run Connection Automation,弹出一个对话框,选中switches

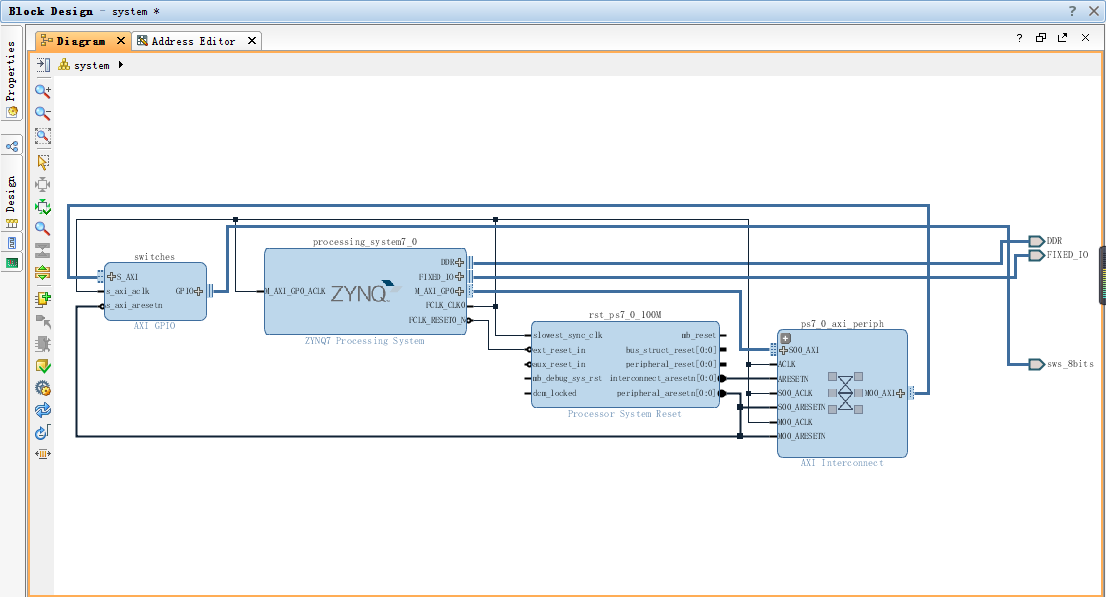

可以看到连接完成的系统结构,图中新添加了2个模块。

单击 Diagram 左侧添加IP的按钮,在弹出的额搜索框内输入g,双击AXI GPIO将其添加到设计中。

单击新添加的模块,在 Block Properties 的窗口内,将Name 后面的名字改为 buttons

双击新加的模块,按如下配置。

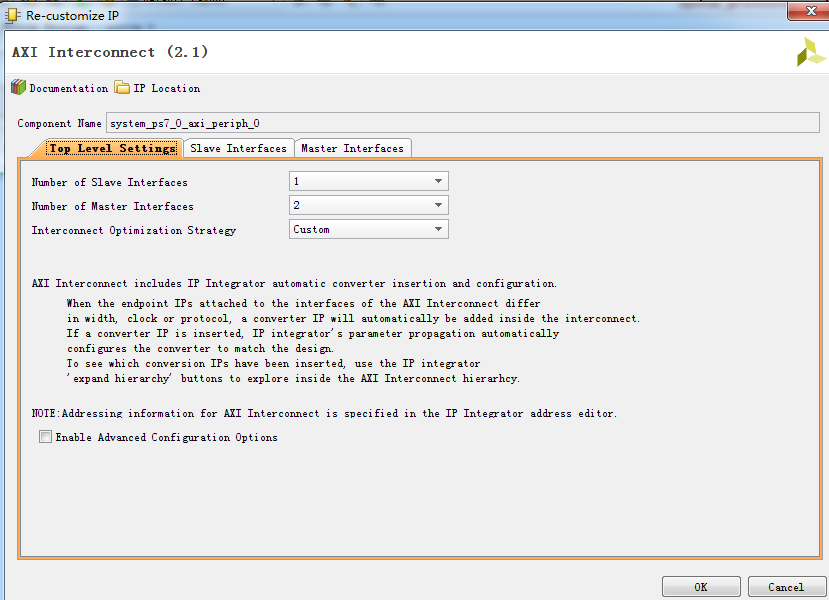

双击 AXI Interconnect 块图标,弹出配置对话框,将 Number of Master Interfaces 后的值改为2

单击新的AXI GPIO 块的 S_AXI 端口,出现一个指针箭头,拖拽并一直按着鼠标左键。出现 Found 1 interface 消息,在 AXI Interconnect的M01_AXI 端口右边出现一个勾,表示这是一个有效的连接端口,拖拽鼠标到这个端口。这样新的GPIO模块和AXI端口相连接。

类似,连接下面的端口

(二)连接外部GPIO外设

前面添加的按键和开关控制器buttons和switches,将连接到zedboard的相应的引脚,用于控制外部设备。该连接过程可以手工完成,也可以使用设计助手。相应的引脚约束信息由zedboard板给出。

连接外部GPIO外设的步骤如下:

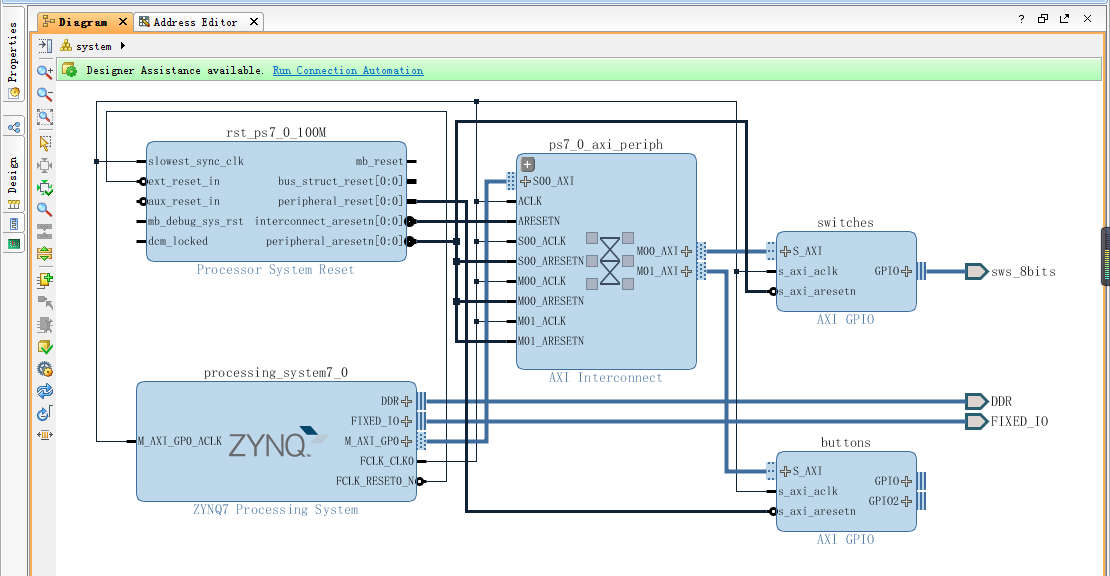

设计完成的系统结构

(三)设计约束

在Source 窗口内,右键单击system.bd 文件,在浮动菜单内,执行Create HDL Wrapper,更新HDL文件。弹出Create HDL Wrapper 对话框,在该对话框内,选中 Let Vivado manage wrapper and auto-update 前面的复选框。然后进行综合,然后打开综合后的设计。

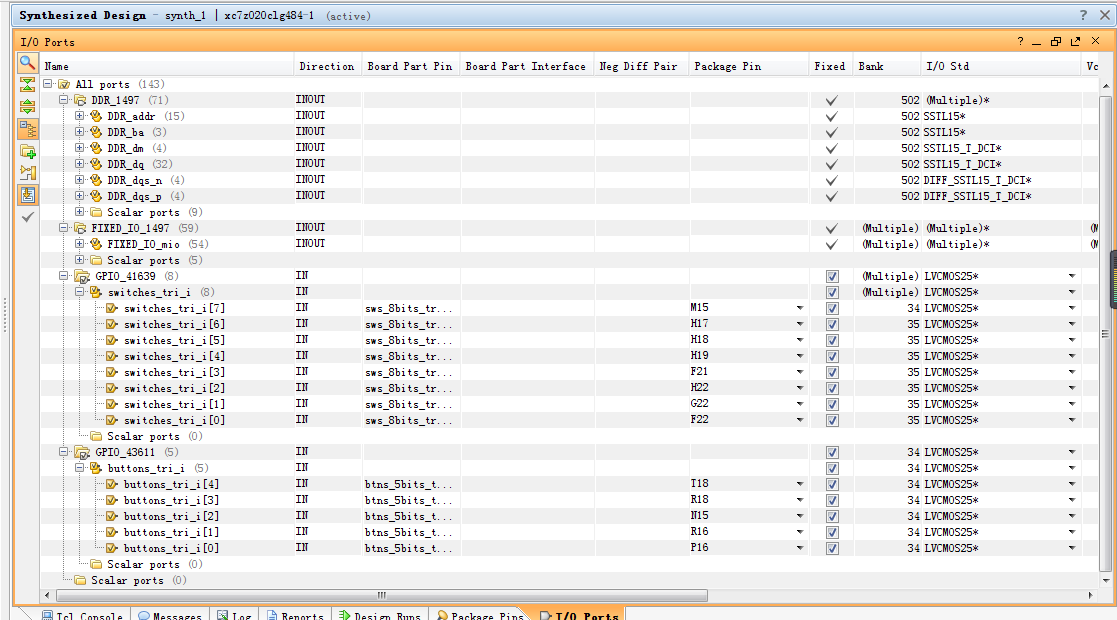

在快捷栏下拉框下,选择I/O Planning 选项。展开button_tri_i,可以看到已经为该控制器分配了引脚,引脚信息也包含在板级支持包内。当IP自动连接到端口时,自动分配引脚,Switches_tri_i也自动分配了引脚。

(四)生成比特流和导出硬件到SDK

在vivado 的Flow Navigator 窗口下找到并展开 Program and Debug 选项。在展开项中,找到并双击Generate Bitstream .

在Vivado 当前工程主界面菜单下,执行菜单命令,File,Export,Export Hardware。弹出 Export Hardware 对话框,在该对话框中吗,必须选中 Include bitstream 前面的复选框(因为设计中使用了ZYNQ的PL部分)。然后执行 File, Launch SDK。

(五)生成测试程序

在SDK主界面左侧的Project Explorer 窗口下,分别选中mem_test和mem_test_bsp,单击鼠标右键,出现浮动菜单。执行 Delete。这样就删除了前一个工程所生成的应用工程和板级支持包。

同样的,在Project Explorer 窗口下,选中 system_wrapper_hw_platform_0 ,单击鼠标右键,出现浮动菜单,执行Delete,这样就删除了前一个工程生成的硬件平台信息。

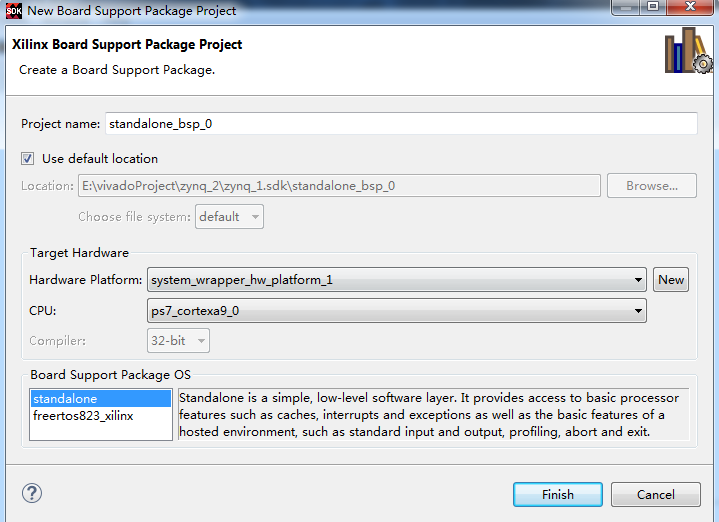

在SDK主界面菜单下,执行 File,New, Board Support Package。弹出一个对话框,单击Finish按钮,弹出Board Support Package Settings对话框,单击OK,自动编译BSP工程。

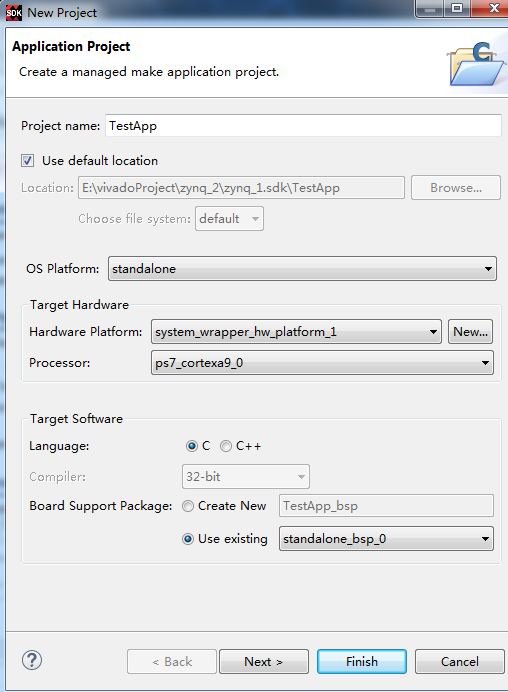

在SDK主界面的菜单下,执行命令 File,New,Application Project.弹出的对话框按如下配置

点击 Next 按钮, 弹出New Project-Template 对话框,在Available Templates 下面选择 Empty Application。单击 Finish 按钮,在后台运行库生成器并且生成xparameter.h文件

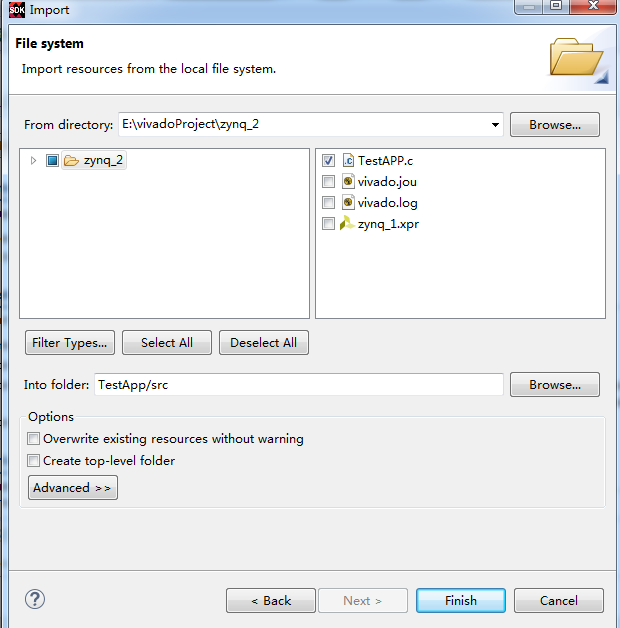

在SDK主界面的 Project Explorer 窗口下,展开 TestApp,src。选中src,单击鼠标右键,出现浮动菜单。执行Import,展开General 选项,选择File System。单击Next,按下图

其中TestAPP.c的代码如下:

#include "xparameters.h"

#include "xgpio.h"

int main(void)

{

XGpio dip,push;

int psb_check,dip_check;

xil_printf("--Start of the Programm--\r\n");

XGpio_Initialize(&dip,XPAR_SWITCHES_DEVICE_ID);

XGpio_SetDataDirection(&dip,1,0xffffffff);

XGpio_Initialize(&push,XPAR_BUTTONS_DEVICE_ID);

XGpio_SetDataDirection(&push,1,0xffffffff);

while(1)

{

psb_check = XGpio_DiscreteRead(&push,1);

xil_printf("Push Buttons Status %x\r\n",psb_check);

dip_check = XGpio_DiscreteRead(&dip,1);

xil_printf("DIP Switch Status %x\r\n",dip_check);

sleep(1);

}

}

(六)验证设计

按照前面的方法,连接PC和Zedboard直接的JTAG和UART,并且给板子上电。选择Terminal 标签,按以前的参数配置 UART。

在SDK 主界面的菜单下,执行,Xilinx Tools,Program FPGA,在弹出的对话框中,单击Program按钮,将比特流文件下载到FPGA。当编程完成后,zedboard 板上的DONE LED(蓝色)变亮。在SDK主界面左侧的Project Explorer窗口下,选择TestApp,单击鼠标右键,出现浮动菜单。执行Run As,Launch on Hardware(GDB).将应用程序下载到FPGA,执行ps7_init和TestApp.elf

/3

/3

curton 2019-5-9 21:28