首先感谢社区提供图书试读活动,能够让我有机会申请到这本期待已久的书《手把手教你设计CPU——RISC-V处理器篇》。

之所以期待已久是因为,本书作者是一线工程师出身,工程师写的书往往理论内容少一些,读起来不会很枯燥,另一方面更加结合实际的开发和应用,会有很多的经验总结和分享,能够让读者学以致用,应用到工作和学习的实际项目中。

#作为一名芯片公司的软件工程师,我对各种架构CPU和生态以及计算机各个方面的基础理论也稍有研究。

这本书主要以设计一颗RISC-V的MCU为例,详细介绍了CPU是怎样炼成的。书中描述了设计过程中的重点环节和模块,并在Github开源了相应芯片蜂鸟E203的源码以及相关文档,项目地址为https://github.com/SI-RISCV/e200_opensource,读者可以结合源码仔细阅读书中相应章节。

什么是RISC-V?

简单来说,RISC-V是一种最近几年比较热门的新的CPU架构,和x86和arm一样,它符合基本的CPU体系结构模型能够实现计算和控制功能。所不同的是它并非诞生于商业公司,而是由教育机构和开源社区合作实现并通过开源基金会管理。它能够为开发者提供开源/免费的指令集和CPU参考设计,并且是非常高效和先进的设计。

为什么选择RISC-V架构?

书中前两章很好的回答了这个问题。想当年,CPU界群雄并起,争霸江湖。但最终x86凭借wintel建立的强大生态联盟,占领了PC和服务器市场。而arm则是凭借优秀的低功耗设计和不错的运气在智能机兴起时期,迅速占领了市场并不断加强生态建设建立自己的护城河。

但是这两种架构的指令集都是归商业公司所有,想要使用相关架构的CPU甚至基于指令集实现CPU都是收费的,而且使用上也有很多限制。Berkeley的同志们就是困扰于没有可靠的免费指令集可用,遂决定重新定义新的架构并基于此架构设计芯片。

从书中概括几个RISC-V架构的主要特点:

架构简洁:相比于x86和arm,后两者都经历了多则数十年的发展,不断优化/增强的同时还要保持向前兼容,这样不断的打补丁就导致架构变的越来越臃肿,虽然众多优秀的工程师投入巨大精力使得性能仍然非常好,但是从设计者的角度,越来越难去把握其中的细节,有大量的坑在等着你,这一点从x86或者arm为架构出的errata文档就可以看出。RISC-V因为吸取了大量先进的设计理念和经验,具备后发优势,没有历史包袱,架构更加简洁清晰,用作者的话说就是短小精悍。感兴趣的读者可以从基金会官网https://riscv.org/ 或者本书项目的GitHub主页下载阅读架构文档。

模块化的指令集:相比于arm架构A / R / M三个高中低架构互不兼容,RISC-V能够使得用户灵活地选择不同个的模块进行组合,满足各种应用需求。如嵌入式选择RV32IC,高性能可选择RV32IMFDC等

扩展指令集:用户可以根据需要扩展自己的指令子集,RISC-V预留了大量的指令编码空间用于用户自定义扩展。为了狙击RISC-V,arm最近也宣布在部分CPU内核引入自定义指令功能。

CPU长啥样?

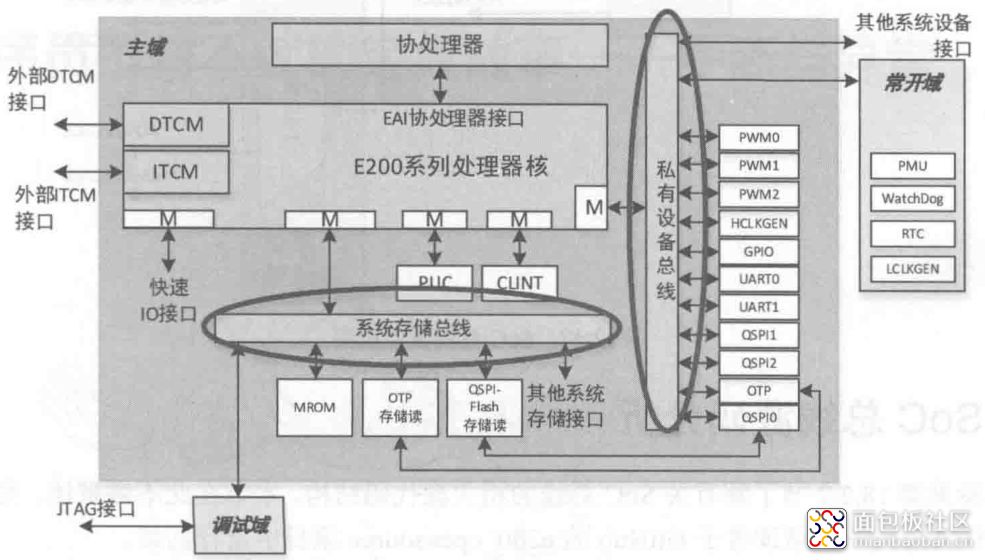

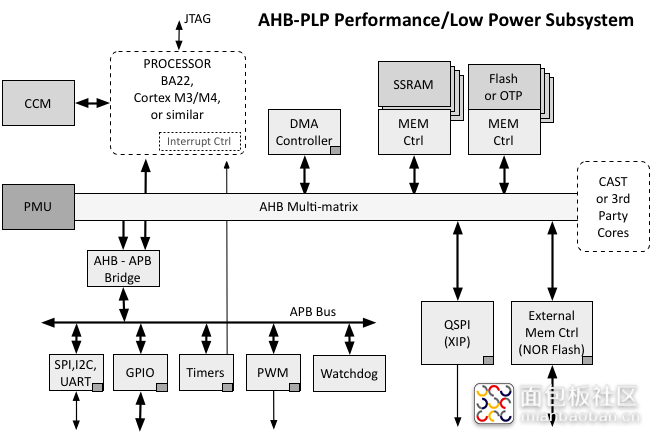

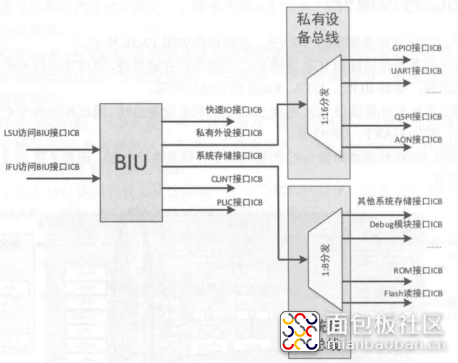

书中蜂鸟E203 SOC和Core原理图如下:

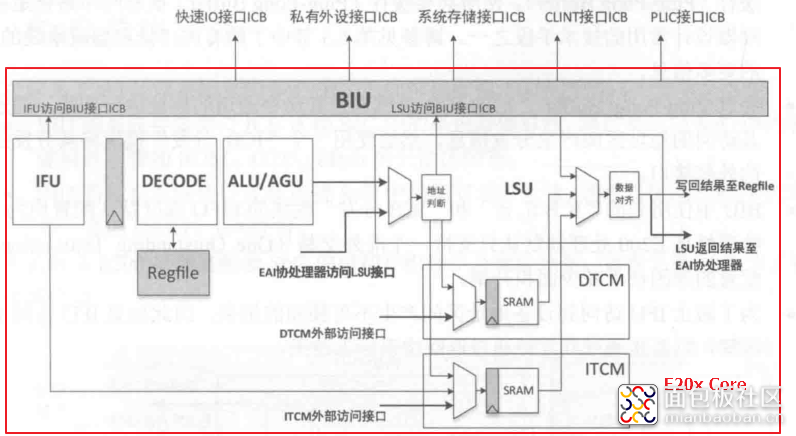

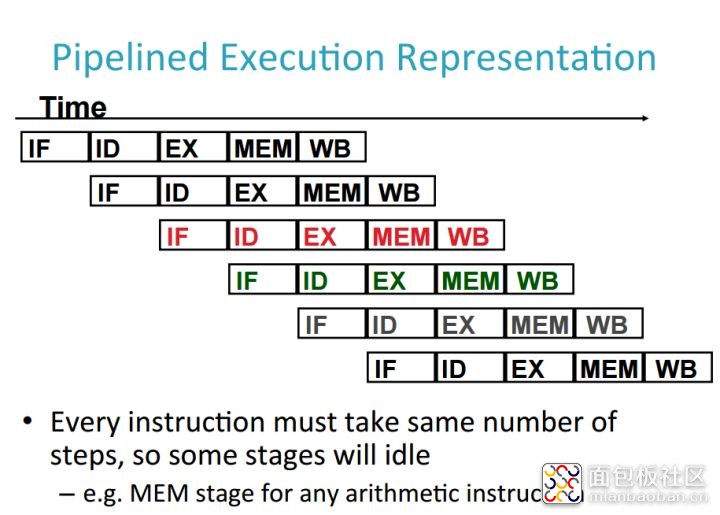

CPU Core中主要包含取指器/译码器(也叫控制器)/计算执行单元(ALU)和寄存器组,流水线的实现就是对这几个模块的硬件多次实现并行执行。

书中7-10章讲解了指令执行过程中各个步骤的硬件如何设计和优化,包括取指/ 译码/执行/交付和写回。

上层软件经过编译链接生成对应机器的字节码,CPU从相应地址根据指令长度依次取指执行。一切看上去很自然也很轻松,但是硬件设计上需要考虑很多问题,比如如何快速取值,如何处理非对齐指令和分支指令等。指令执行过程中会碰到流水线冲突和分支如何预测等更多问题,如何设计可靠的CPU确实需要非常多的经验积累,参考本书可以少走很多弯路。

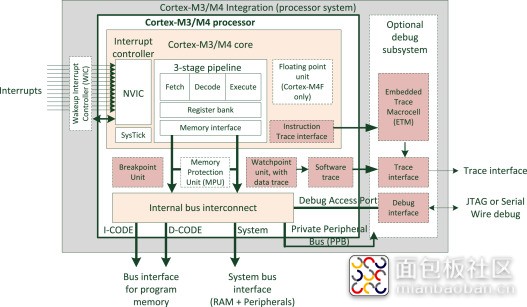

Core中其他硬件模块还包括存储器接口/中断控制器,和其他可选的如FPU(浮点运算模块)和trace接口等,参见书中相关章节。

这样我们就有了一个可以进行运算的Core。对于SOC来说,我们还需要片内总线进行core和外设的连接,常用的总线协议包括AHB APB等,蜂鸟E203中使用自定义总线协议ICB进行Core和存储器等外设的互联

书中第三部分具体讲解了如何在FPGA上运行和验证这颗蜂鸟E203 SOC,有FPGA硬件开发板并且熟悉verilog的同学可以按照书中的介绍对该芯片的开源代码进行仿真测试和运行。

最后附上arm Cortex M4架构图做为对比学习

作者: plyy, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3895810.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/1

/1

curton 2019-10-15 19:51