芯片设计是非常依赖于工具的,设想一下,如果没有 EDA 工具的支持,如何去勾勒出一个具有上亿个晶体管的海思麒麟 SoC 芯片呢?是的,学习一门技术,工具至关重要。事不宜迟,数字 IC 设计工程师或者 FPGA 开发工程师必须抓紧熟悉 FPGA 开发工具的操作,下文是详细的 Xilinx_Vivado_SDK_2019.1 开发指导教程。

01

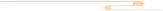

首先,打开 Xilinx_Vivado_SDK_2019.1 开发工具,点击 Create Project -> 点击Next:

02

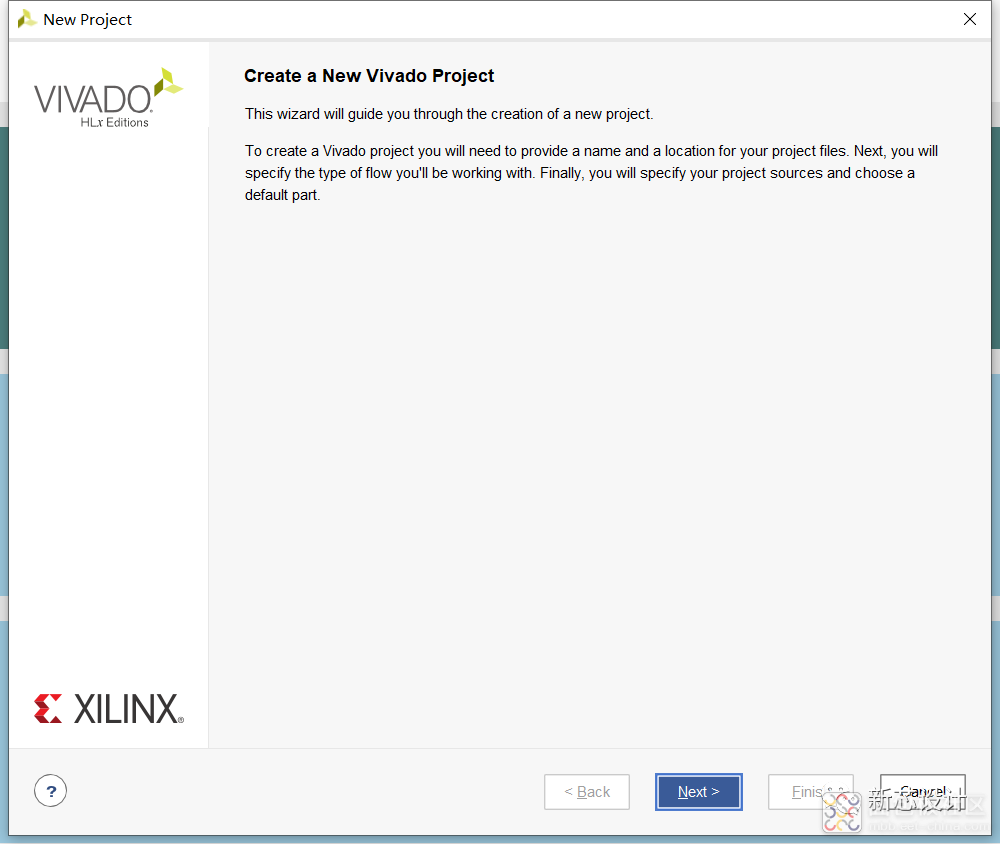

接着,填写你的 Project Name 和 Project Location 之后(注意不支持中文,无论是名字还是路径),这里,勾选 Create Project Subdirectory 为你的工程创建一个子目录。点击 Next:

03

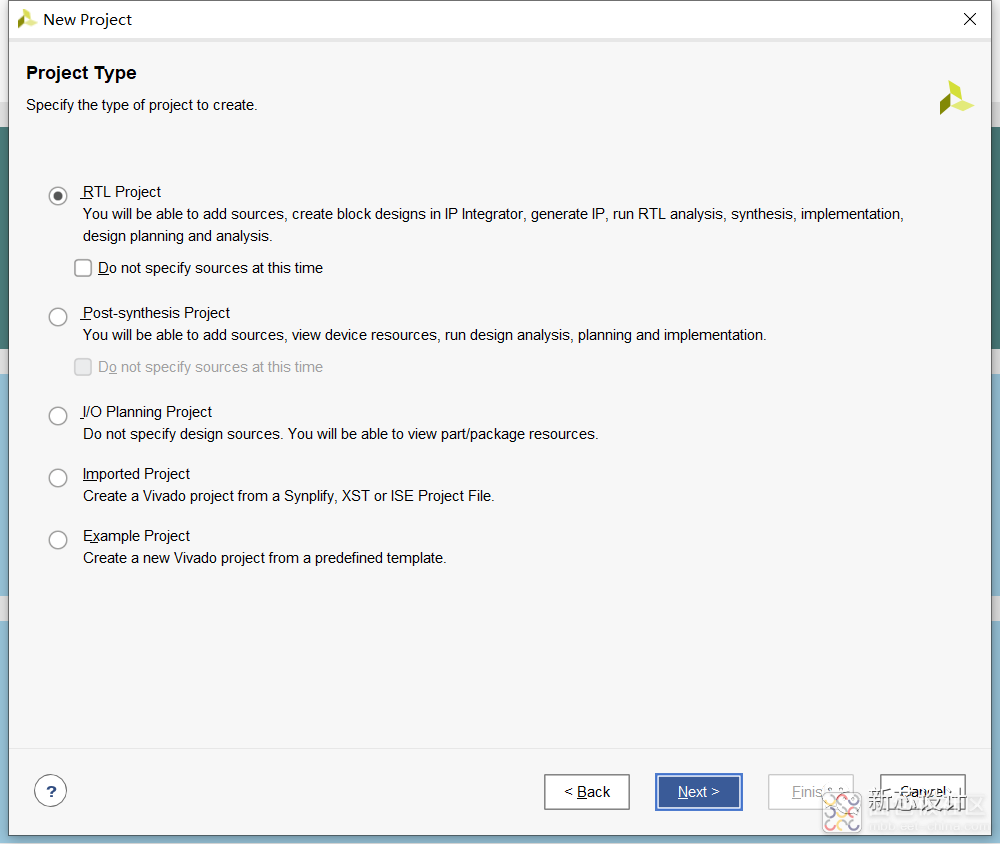

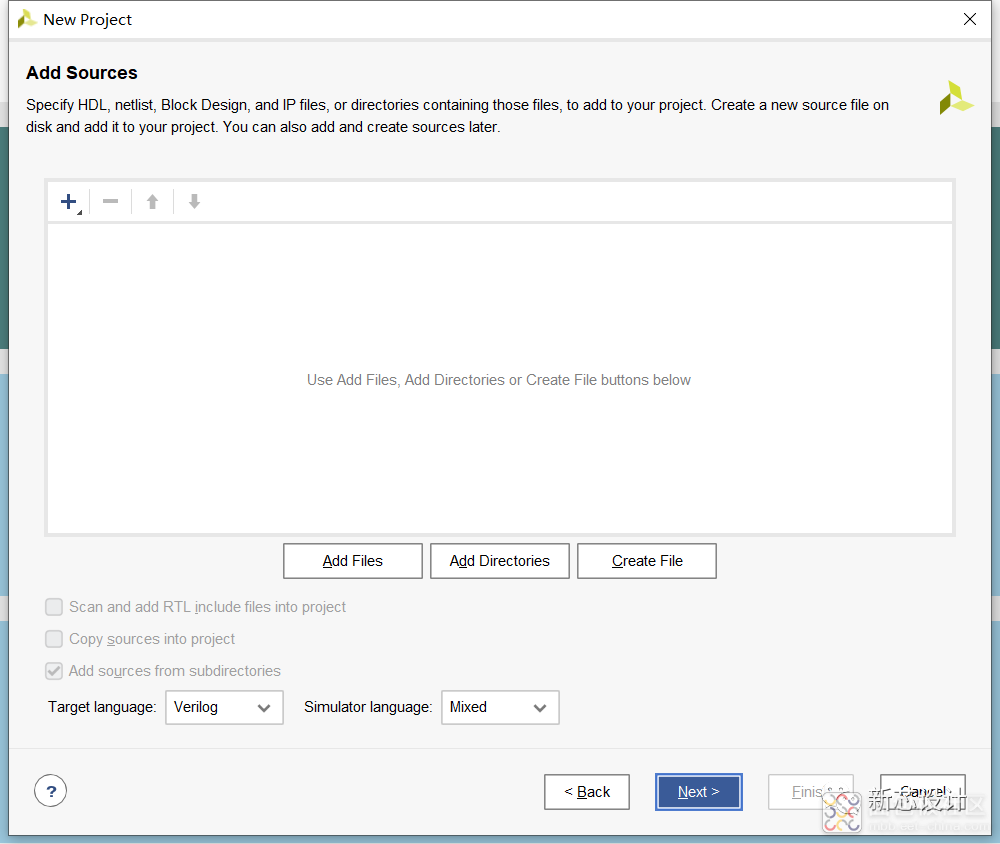

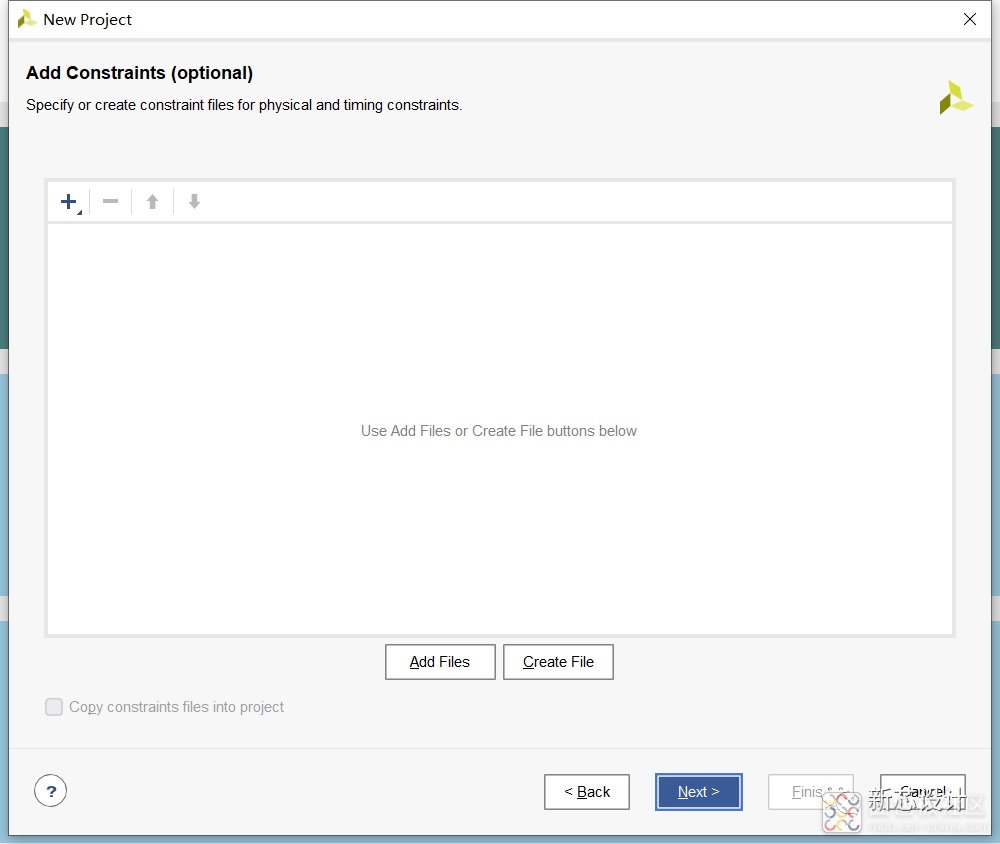

这里,选择 RTL Project,可以勾选 Do not specify sources at this time,这样的话接下来就不会让你 Add Sources 和 Add Constraints。点击 Next -> 点击 Next -> 点击 Next:

04

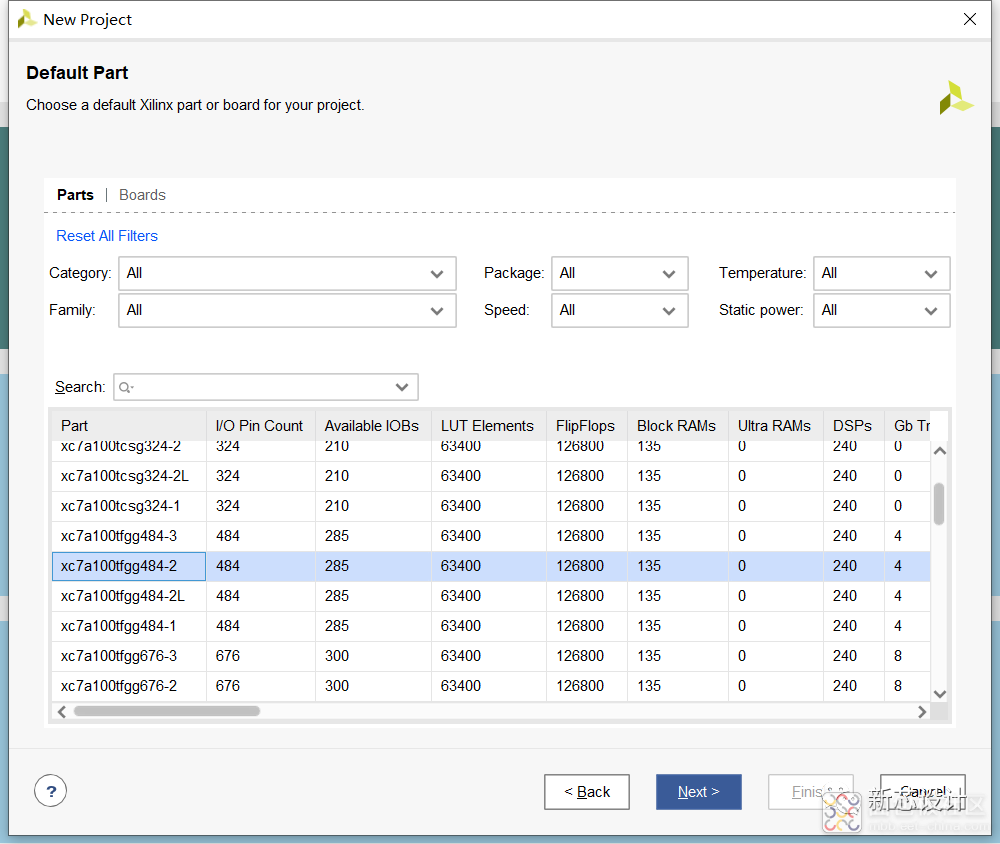

这里,选择你的器件,主要是勾选对应的 FPGA 开发板的芯片型号,主要是为了配合之后的综合、实现、上板、测试的步骤。之后点击 Next:

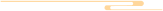

05

最终,点击 Finish 即可完成工程的建立:

06

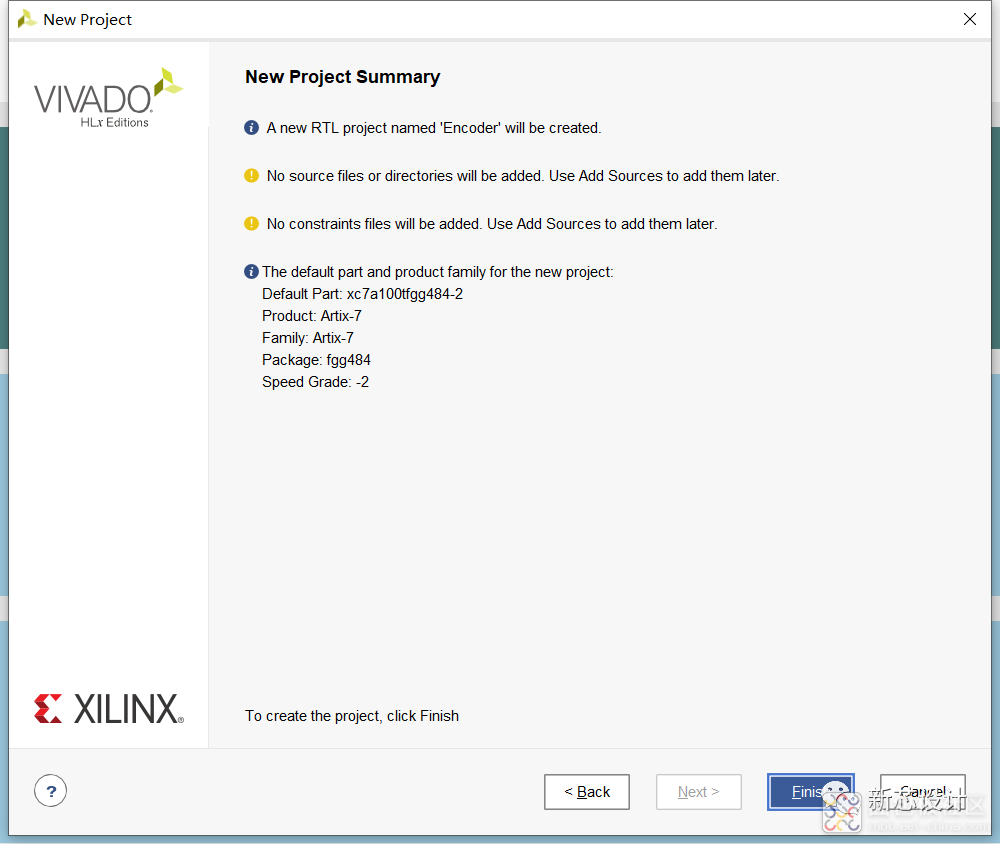

结束!这里,附加 Xilinx_Vivado_SDK_2019.1 基本的开发步骤,这些都在 Xilinx Vivado 软件的左侧工具栏里(如下所示),大家可以自行详细地去试验一下,其中,绿色加粗的文字是初学者必须跑通的步骤,蓝色加粗的文字是高阶设计必须掌握的步骤,根据个人的实际设计水准来依次执行即可。

写代码(编写源文件 Add or Create Design Sources)

看电路(查看原理图 Schematic)

写仿真(新建仿真文件 Add or Create Simulation Sources)

跑仿真(仿真分析 Run Simulation)

加约束(添加引脚/时序约束文件 Add or Create Constraints)

跑综合(设计综合 Run Synthesis)

跑实现(设计实现 Run Implementation)

看资源(综合/实现资源 Report Utilizatioin)

看时序(综合/实现时序 Report Timing Summary)

看功耗(综合/实现功耗 Report Power)

比特流(生成比特流文件 Generate Bitstream)

跑板子(下载比特流文件到FPGA:Program Device)

/4

/4

文章评论(0条评论)

登录后参与讨论