随着 2018 年中兴制裁事件和 2019 年华为制裁事件的发生,一下子打破了中国芯片技术的“繁华”,引发了中国芯片市场的“危机”。是的,我们的核心技术还没有在我们自己的手上,我们的进口芯片基本覆盖了自研芯片,只有自主研发才能够拯救中国的芯片市场。2020~2022 年,随着国家芯片战略的连续发布,不断引发了各类高校的重视和资本市场的投资,211、985 重点高校单独成立了集成电路学院、微电子学院,芯片原厂、互联网大厂甚至为了挖掘人才,给出的 OFFER 高达 25~55W 年薪,跳槽涨薪平均幅值是 30% 左右,高校应届毕业生倒挂上一届的范围更是在 20%~50% 之间。

这是近 3~5 年的统计数据,可能不是 100% 准确,却基本体现了整个 IC 行业的普遍现象。在现如今如火如荼的芯片领域中,无论是科研前景还是就业“钱”景,都着实令人非常的向往,这也是“新芯设计”公众号的初衷。

“赛洛基”团队为了支持芯片设计者,呕心沥血集成了工作、科研、竞赛于一体的《基于 RISC-V SoC 的可配置 FFT 系统设计》专栏项目。同样的,这也是在一位海归教授的带领之下的整个团队辛勤耕耘的结晶,希望大家能够在理论结合实践的指导之下,不断地提高自己的数字芯片设计技术能力,成为一名具有极大竞争力的数字 IC 设计领域专家。

1、项目价值

工作求职:这是简历上极具竞争力的一个芯片设计项目,集成了 RISC-V 指令集、RISC-V 编译原理、自定义指令、RISC-V CPU、SoC、FPGA、FFT、系统级设计以及 Verilog、C、Python、Matlab 等等的超级热门的芯片设计元素,从而找到了较好的工作(2022 年普遍能够达到 30W+、40W+、50W+ 的薪资水平),具体个人名单及其对应的公司名单就不列出来了~

科研项目:这也是科研项目中具有丰富元素的一个 IC 设计项目,无论是算法层面、软件层面、系统层面还是灵活性可配置性设计层面,都可以作为科研的一个方向。同时,还可以提升你的工程能力,毕竟科研需要的还是一种创新精神,而创新思维又需要与实际的设计工程相结合才能够绽放光芒。所以,本次的项目是一个良好的、可创新实现的、具有科研性质的设计平台~

集创竞赛:项目的来源就是基于《第三届全国大学生集成电路创新创业大赛 - RISC-V 杯》,其中具备了大部分比赛本身没有要求的创新思维和极佳的芯片设计要素。无论是对于集创竞赛本身的实现,还是芯片设计本身的升华,都是极具统治级的。对于高校参赛者和学习爱好者都是非常有帮助的,其实每一年的题目其实都差不多,这个专栏能够让你们在起点领先其它的队伍一大半,当然,机遇与努力并存,专栏提供了一个良好的学习机遇,最终依旧需要各位的努力~

2、项目概述

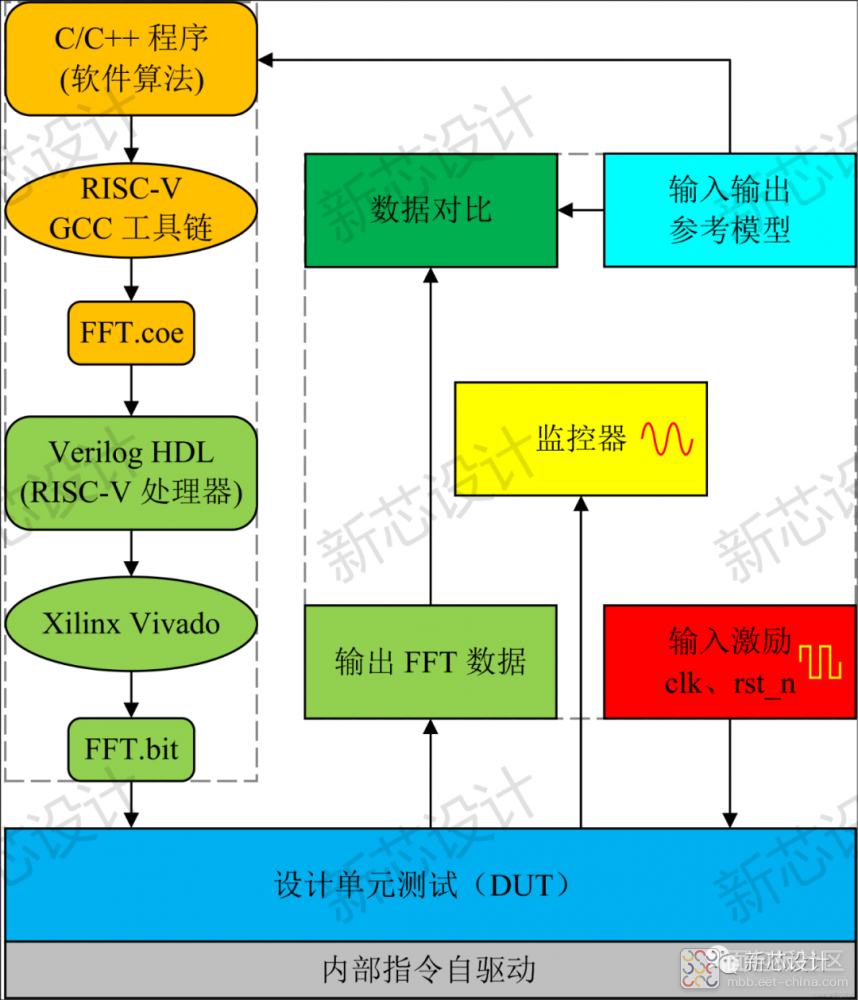

这是一个集成了 RISC-V、SoC、FPGA、Verilog、MATLAB、Python、C/C++、嵌入式系统、FFT 通信算法、交叉编译环境、软硬件协同设计等等的一个具有创新性的工程。主要的核心设计是 RISC-V 专用 CPU 的设计、FFT 嵌入式 C 的设计、以及 FPGA SoC 的设计。次要的专业技能是 RISC-V 交叉编译技术、软硬件协同验证、基于 RISC-V CPU 指令集的仿真验证环境的搭建思路、FFT 通信算法的理论掌握与代码实现等等。

3、项目展览

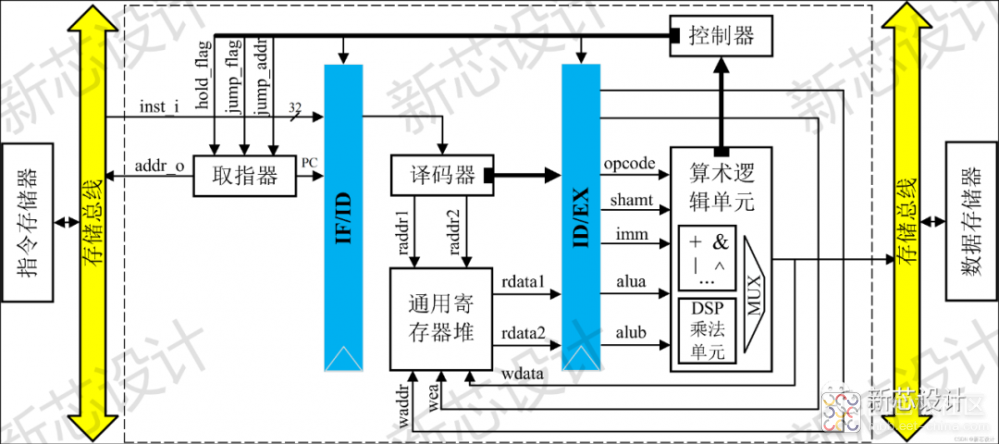

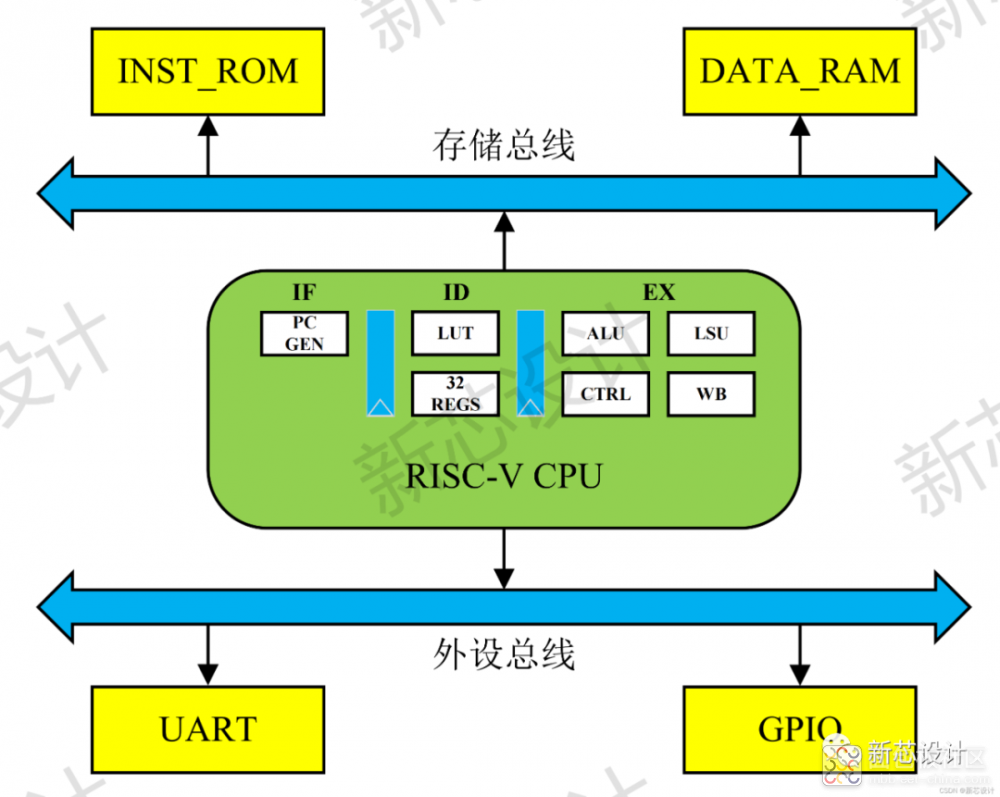

基于 5 级流水线设计的 RISC-V CPU 内核架构和 RISC-V SoC 系统架构

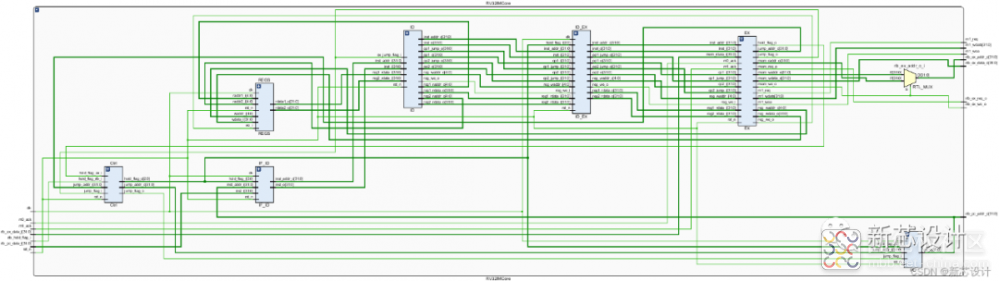

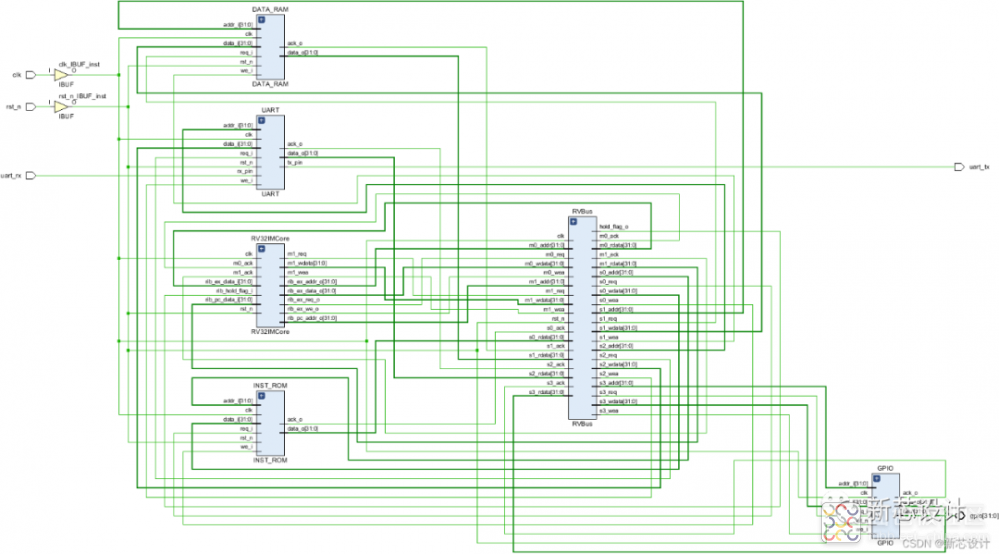

基于 5 级流水线设计的 RISC-V CPU RTL 电路和 RISC-V SoC RTL 电路

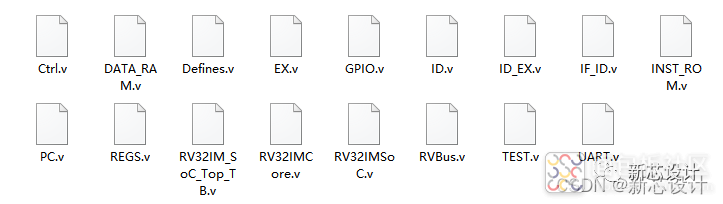

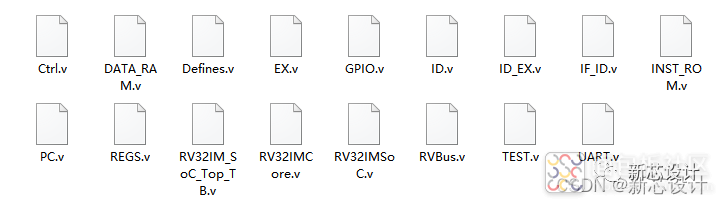

基于 5 级流水线设计的 RISC-V CPU Verilog 代码和 RISC-V SoC Verilog 代码

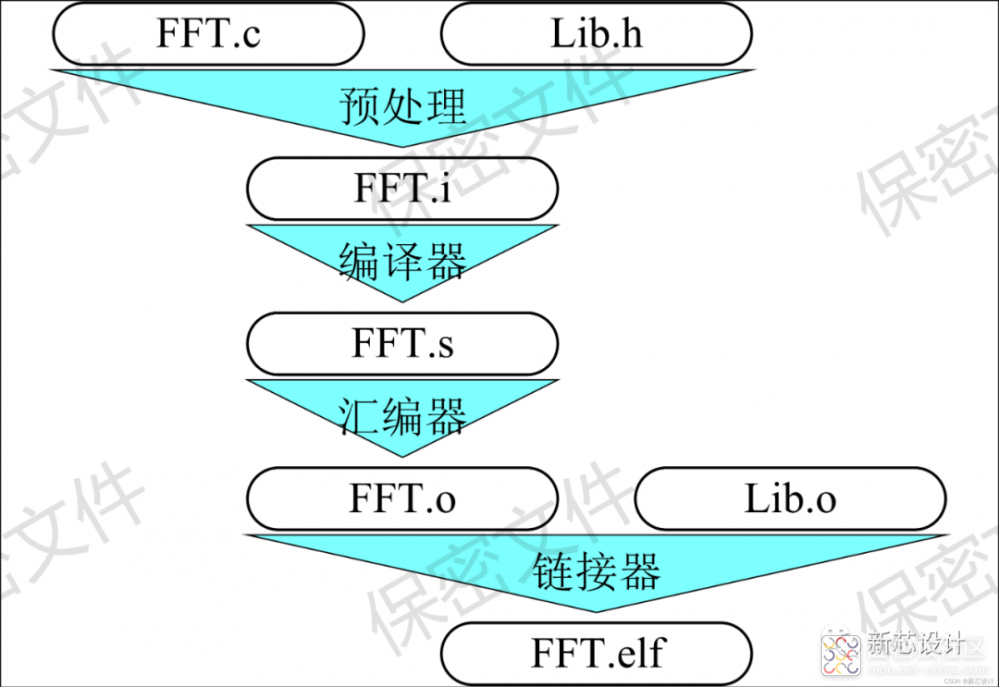

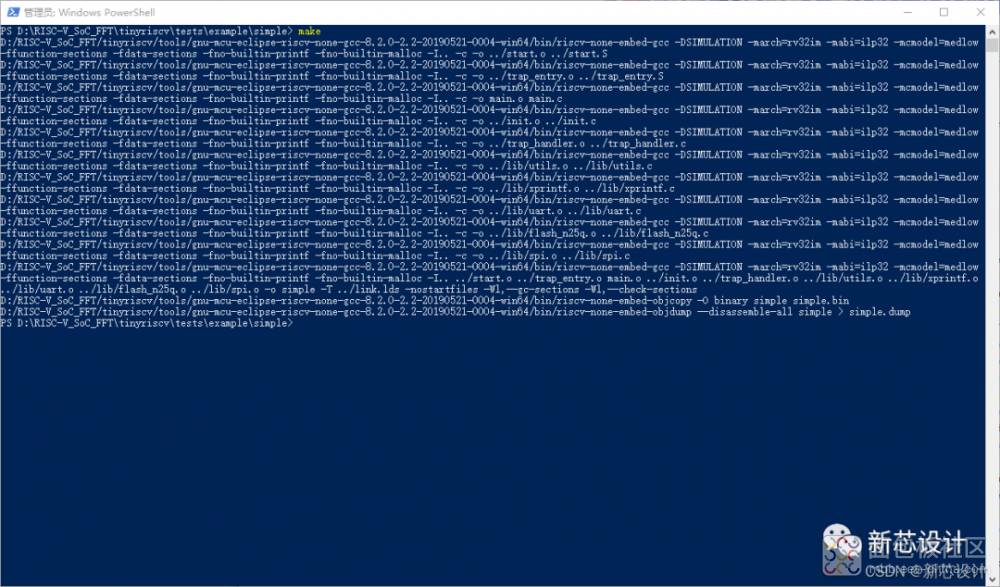

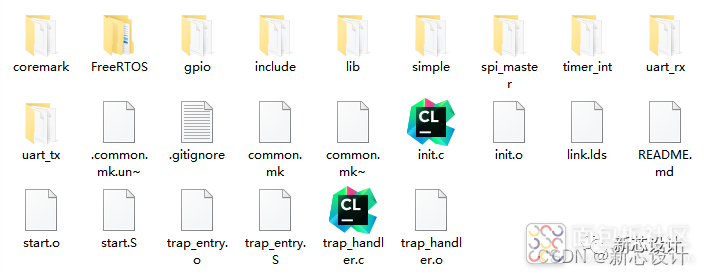

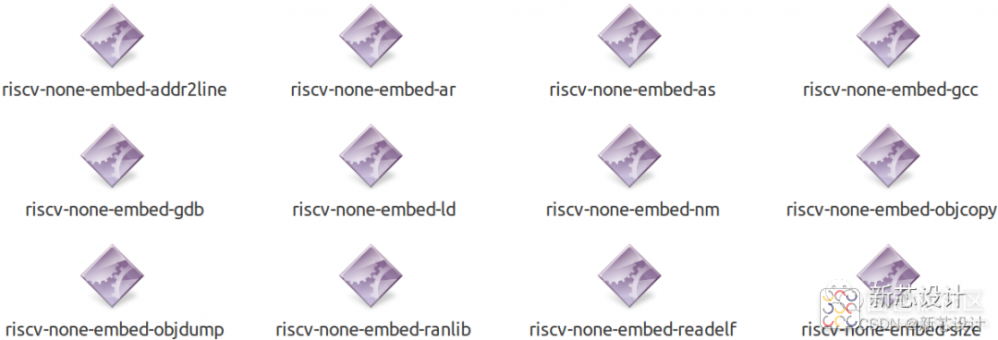

RISC-V 交叉编译流程 Flow 和脚本 Script

基于 Window 和 基于 Linux 的 RISC-V 交叉编译环境

基于 UVM 的软硬件协同验证环境

Vivado 仿真查看频偏波形

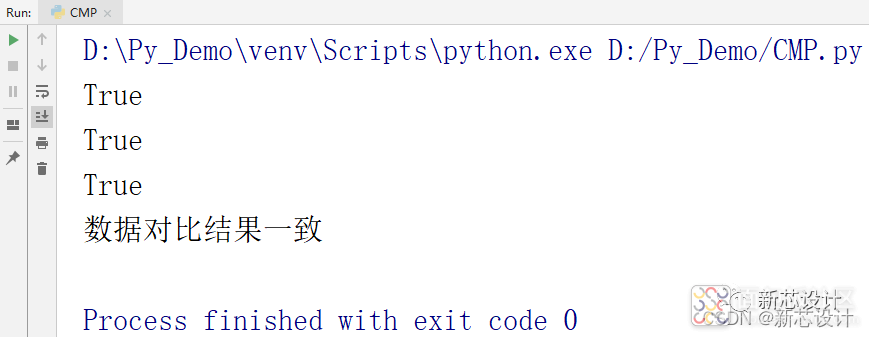

Python 脚本自动对比数据

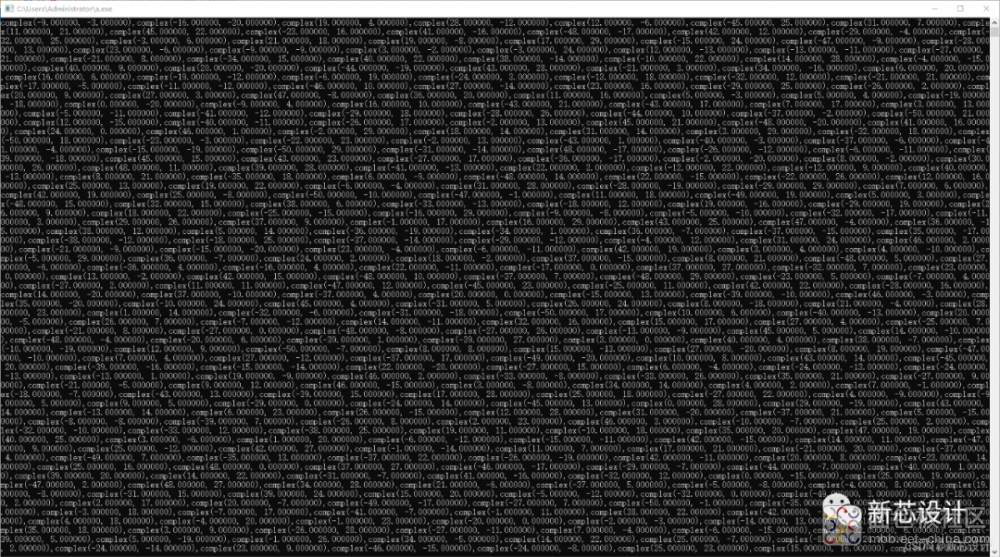

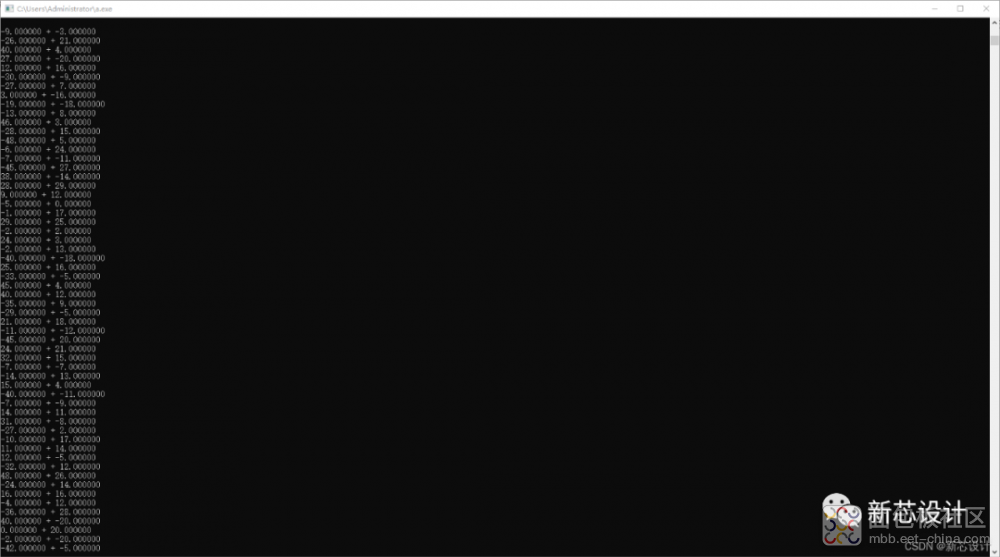

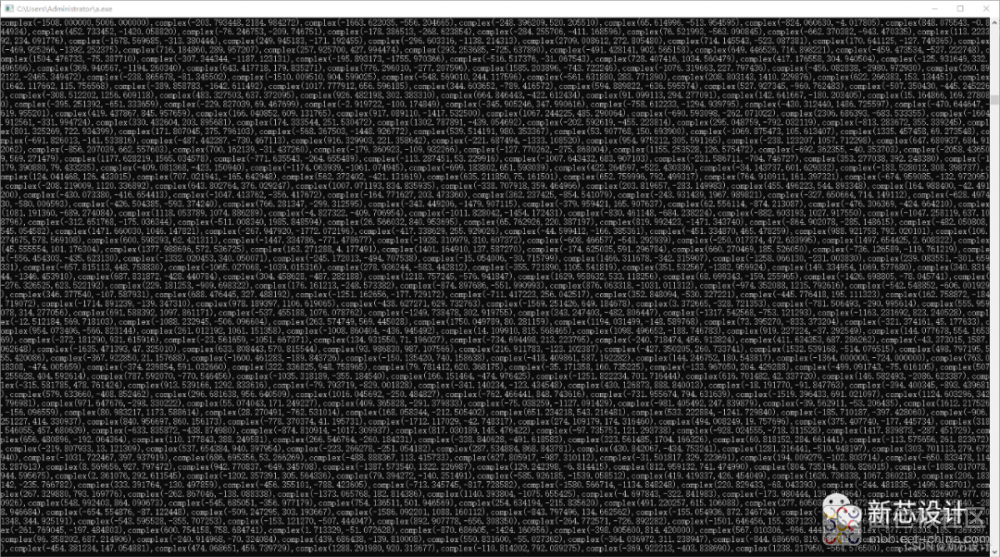

可配置点数的 FFT C 仿真输入数据、参数集合和输出数据

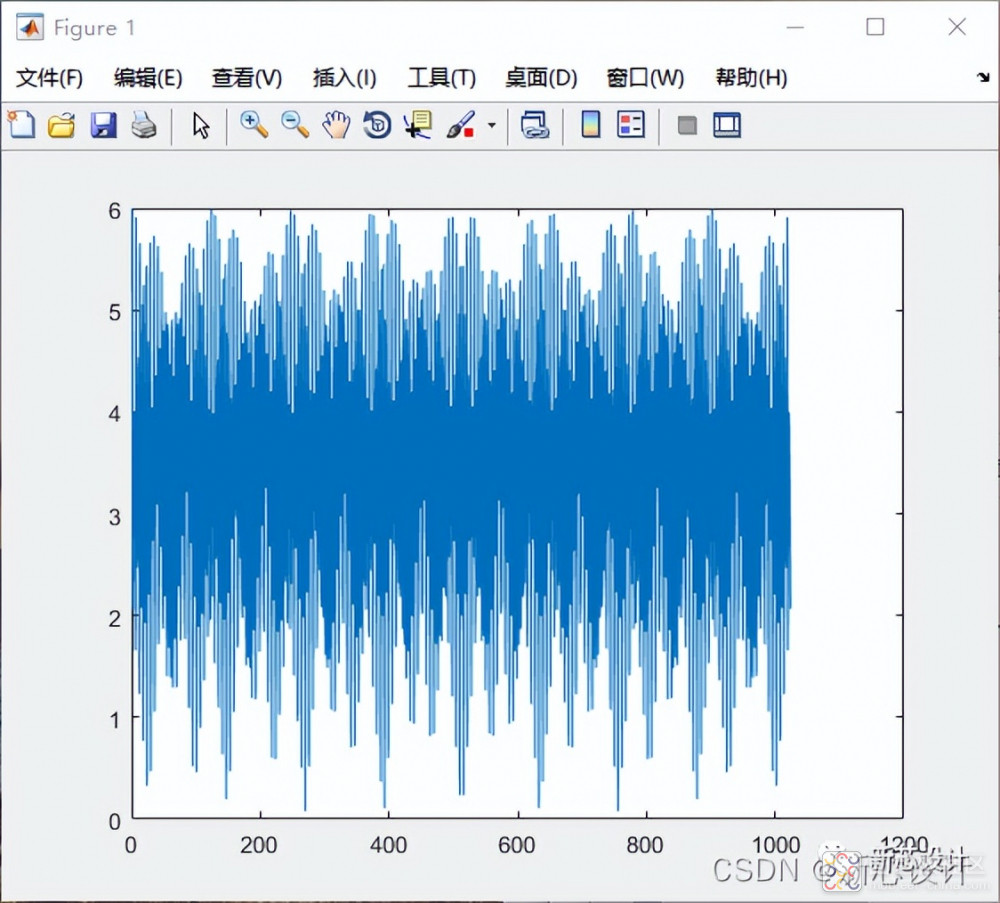

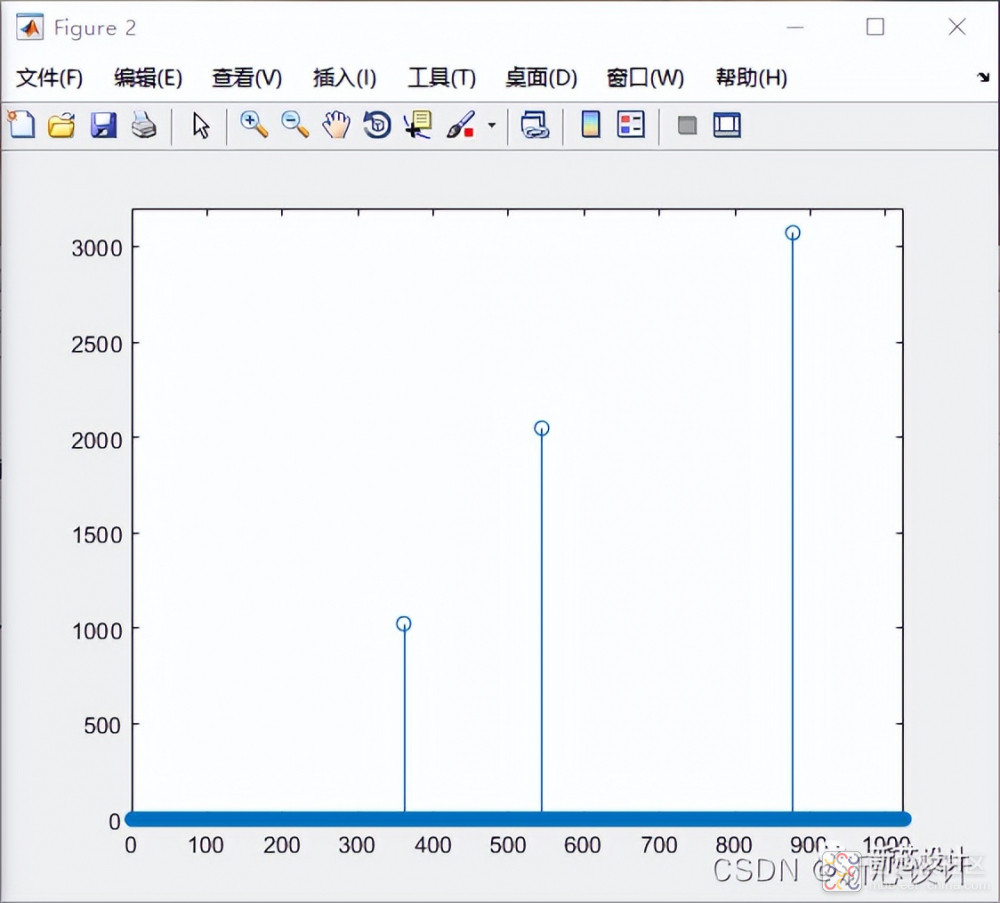

可配置点数的 FFT MATLAB 仿真时域信息和频域信息

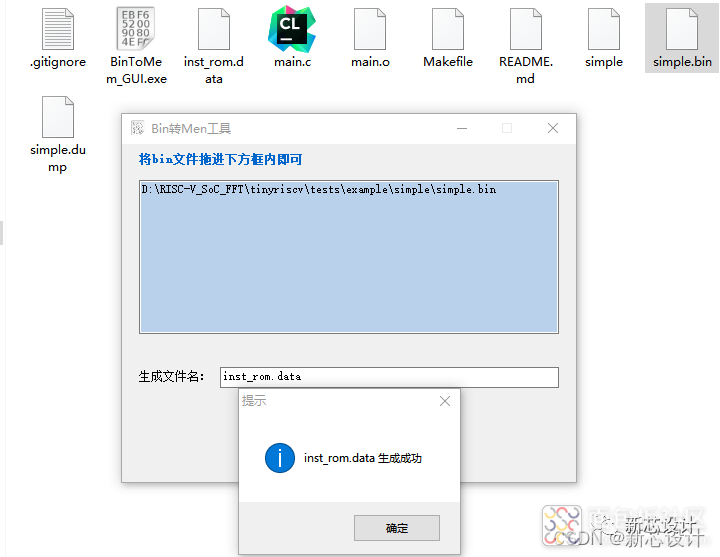

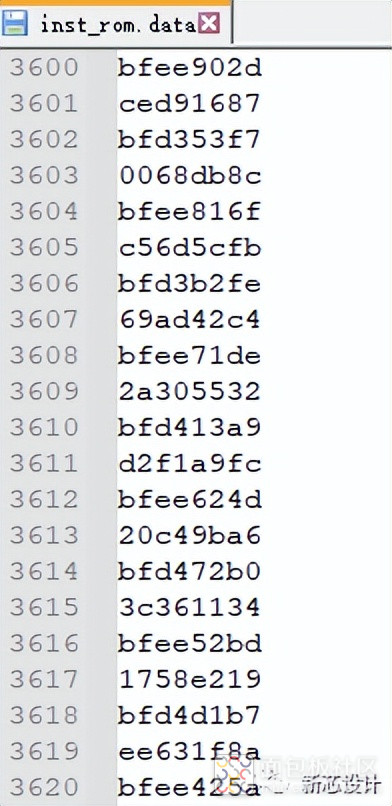

FFT 交叉编译生成 RISC-V 汇编和二进制机器代码

/4

/4

文章评论(0条评论)

登录后参与讨论