在数字 IC 设计中,有时候需要从一组输入数据中挑出某一个数据出来,比如,输入有 “A、B、C、D” 四个数据,我们需要在特定的条件和特定的时刻输出特定的数据,如何输出特定的数据就是 “选择开关” ;又或者,可以理解成多个通道输入映射到单个通道输出;于是,数据选择器(Data Selector)或多路开关(Multiplexer)的数字逻辑电路就应运而生。

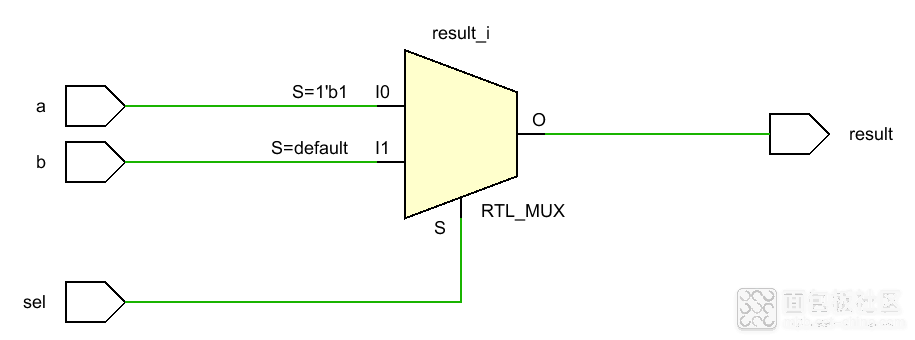

基于 2 选 1 的数据选择器的 Verilog 代码和 RTL 电路

|

Plaintext |

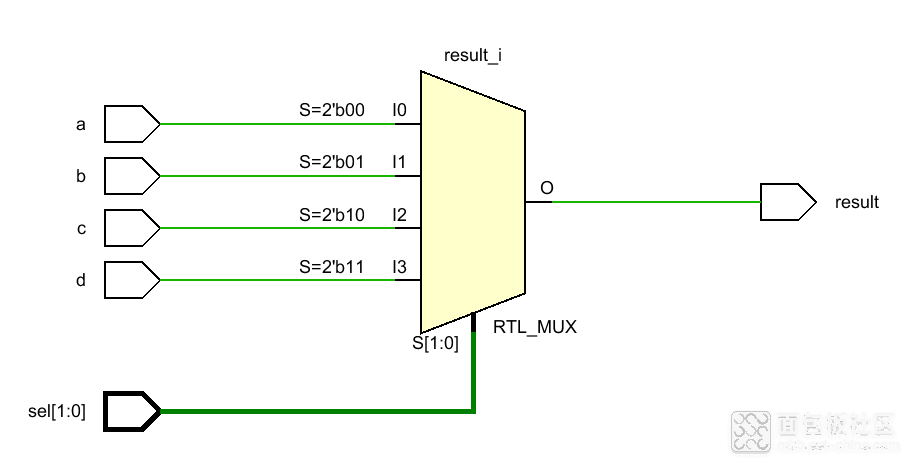

基于 4 选 1 的数据选择器的 Verilog 代码和 RTL 电路

|

Plaintext |

代码详解

基于 2 选 1 的数据选择器的设计代码,非常简单明了,主要是输入数据 a 和 b,然后通过 sel 信号来决定输出是 a 还是 b。倘若 sel 拉高(1),那么就输出 “a”,反之,倘若 sel 拉低(0),那么就输出 “b”。

基于 4 选 1 的数据选择器的设计是基于查找表 LUT(Look Up Table)(查找表在 FPGA 中非常重要,软件思维可以理解为 “索引”,它是 FPGA 芯片架构的重要组成部分,合理利用查找表,能够使你的 FPGA 硬件工程达到一定程度的优化设计)的方式实现的一个电路。

数据选择器在实际生活中应用广泛。比如,在实际中对选手进行挑选,比如在歌手舞台对 “啊三” 编号为 “a”,对 “啊四” 编号为 “b”。然后 “sel” 这个选择信号就交给 “裁判”,倘若 “啊三” 唱歌功底胜出,那么就输出 “a”,反之那么就输出 “b”,非常的形象!!!

所以还是那句话,数字电路模块没有哪一个模块是平白无故添加出来的,每一个数字电路的小模块在实际生活中都有着非常重要的应用。所有的复杂的模块,都是由这些小模块构成的。计算机再强大、AI 再智能,都离不开最基本的电路设计单元。因此,学好数字电路的基础知识之后,才能翱翔于数字电路的世界中,如果基础知识都学不好的话,那么更复杂的就更不用说了。

祝大家能够扎实掌握基础知识,从而在数字电路 FPGA 中如鱼得水、游刃有余。

/4

/4

文章评论(0条评论)

登录后参与讨论