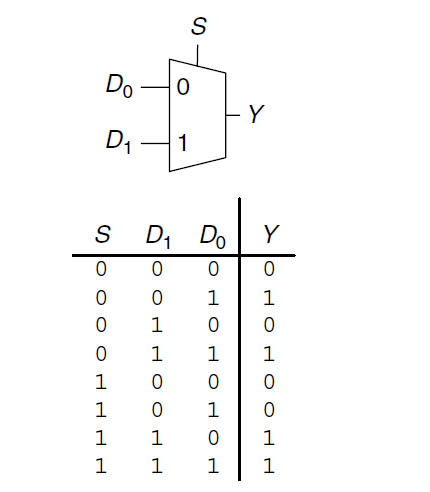

首先解释名词。由于想了好多例子,结果发现没有太好的。于是换一种办法,直接上图和真值表。。 这个东西就是多路复用器(MUX)从图中和真值表可以总结出:当s为0

这个东西就是多路复用器(MUX)从图中和真值表可以总结出:当s为0

选择D0通过,也就是Y=D0,而不在乎D1上的数据(D1是0,1都不影响输出)。而当s为1时,Y=D1。也就是说白了用S选择哪一条路可以传递数据,也就是这个逻辑回路有信号选择功能(比如,D0是键盘0,D1是键盘1,两个键盘同时连一个电脑上。这是为了输入不发生冲突,你可以选择拔下去一个键盘--你就是在相当于s,而拔下去的那个键盘你再怎么按对输入也没影响)。

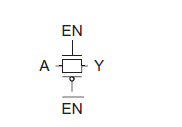

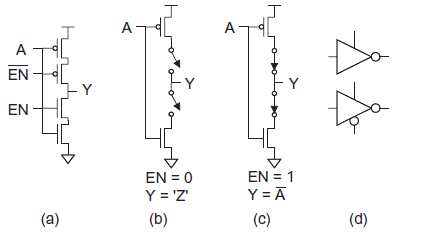

而三态缓存就是一个简单的MUX。见下图:

。

。 EN就是所谓的使能端。当EN=0时,~EN为1,这样Y就处于浮动状态。而当EN=1时,如果输入A的信号受到扰动,由于仅仅是MOS管,所以输出也会受到扰动造成Y的不稳定。所以用这个作为MUX的话,即使EN为0也会消耗电能。并且如果有很多Tristate同时使用时,保证EN的同时性是很困难的。下面是其符号,两种符号表达相同的意思哦。

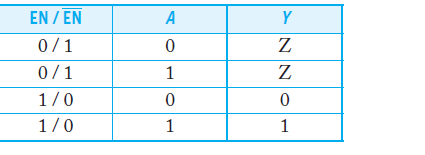

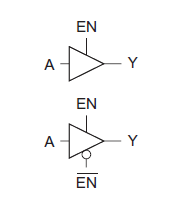

EN就是所谓的使能端。当EN=0时,~EN为1,这样Y就处于浮动状态。而当EN=1时,如果输入A的信号受到扰动,由于仅仅是MOS管,所以输出也会受到扰动造成Y的不稳定。所以用这个作为MUX的话,即使EN为0也会消耗电能。并且如果有很多Tristate同时使用时,保证EN的同时性是很困难的。下面是其符号,两种符号表达相同的意思哦。 但是我们可以用它来实现其他的逻辑门嘛。这里我给出一个带有始能输入的反相器。

但是我们可以用它来实现其他的逻辑门嘛。这里我给出一个带有始能输入的反相器。

看图就会很明显的知道了,虽然当EN=1时我们有前面讲的反相器,但是我们有了更多的控制,但是我们不能用以前的DeMOrgen定律和互补原则来设计它了,因为有了Z状态嘛!

看图就会很明显的知道了,虽然当EN=1时我们有前面讲的反相器,但是我们有了更多的控制,但是我们不能用以前的DeMOrgen定律和互补原则来设计它了,因为有了Z状态嘛!

说到这里,大家要动笔咯。内容是1.用2个Tristate设计上文图中给出的MUX 2.根据上文MUX的真值表,画出线路图(提示:要先写出逻辑表达式,根据DeMorgan定律和互补原则,这里可以用普通的逻辑门)3.*利用反向tristate设计上面的MUX(比较有意思)

/4

/4

文章评论(0条评论)

登录后参与讨论